# Digital Systems Section 2

Chapter (6)

STUDENTS-HUB.com

Uploaded By: ADAMYMORKIA

#### Solution Registers and counters are practical examples of <u>clocked</u> sequential circuits

S A register consists of a group of flip-flops each is capable of storing one bit of information

- The group of FFs normally share a **common clock**

- n-bit register consists of a group of n FFs capable of storing n bits (Each FF store 1-bit)

- S Registers may have combinational logic/gates that affect its operation (Loading/Reading Operations)

- S Flip-flops hold the data (bits)

- So Gates determine how the <u>data (bits)</u> is transferred into/from the register

- Segisters are used in computers, calculators, and almost all electronic equipment these days. Any device must have registers to store binary data. A memory unit is an array of registers

A counter is a register that goes through a predetermined sequence of binary states

The gates in the counter are connected in such a way as to produce the prescribed sequence of states.

Sounters are a special type of register

2STUDENTS-HUB.com

Uploaded By: anonymokialil

### <sup>20</sup><sub>24</sub> *Registers*

3STUDENTS-HUB.com

#### S Various types of registers are available

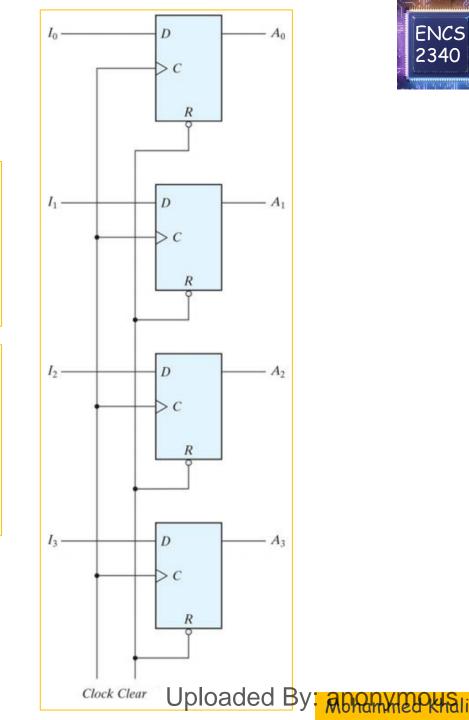

The simplest register  $\rightarrow$  **4-bit** Register

- ▷ Clear (R) is 0 → clear/reset the register to all 0's asynchronously

Note the bubble at R → Active low clear/reset

- ▷ Clear (R) is 1 → With each +ve Edge Clock, the input is stored

The value of (I<sub>0</sub>I<sub>1</sub>I<sub>2</sub>I<sub>3</sub>) immediately before the clock edge determines the value of (A<sub>0</sub>A<sub>1</sub>A<sub>2</sub>A<sub>3</sub>) after the clock edge

- To prevent the previously stored value from changing:

- 1) The Clock has to be **disabled Not Practical**

- 2) Or the **same** value needs to be **passed back** to the inputs

USE: Parallel Load Approach

- S Registers with parallel load are a fundamental building block in digital systems

- Synchronous digital systems have a master clock generator that supplies a continuous train of clock pulses

- S The pulses are applied to all flip-flops and registers in the system

- So The master clock acts like a drum that supplies a constant beat to all parts of the system

- S A separate control signal must be used to decide which register operation will execute at each clock pulse

- Soloading or updating the register is The transfer of <u>new</u> information <u>into</u> a register

- S The loading is in parallel if all the bits are loaded simultaneously at the same clock cycle

- S Recall: To keep the content of the register unchanged:

- 1) The **inputs** must be held **constant**

- 2) Or The **clock** must be **disabled** from the circuit

#### 4STUDENTS-HUB.com

Uploaded By: Abonymous

Registers with Parallel Load

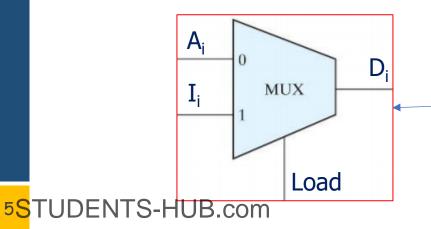

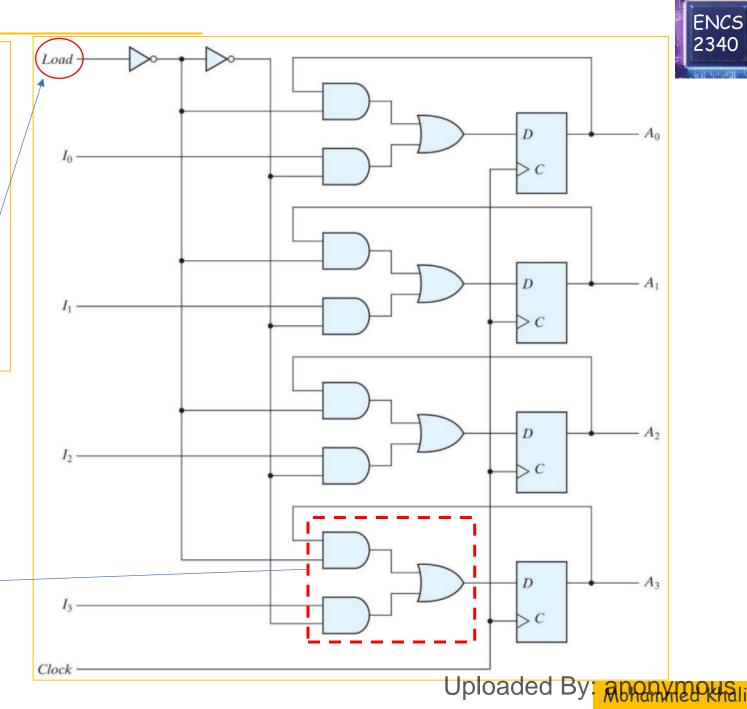

- Solution It is advisable to **control** the operation of the register with the D **inputs**, rather than controlling the clock of the FF's

- Use a **combinational** circuit to either D keep previous value, or load a new one:

- a) Load=0→ keep previous value

- Load=1→ accept (load) new b) value from **I**'s

This can be constructed using a **2x1** mux with each FF

20 24

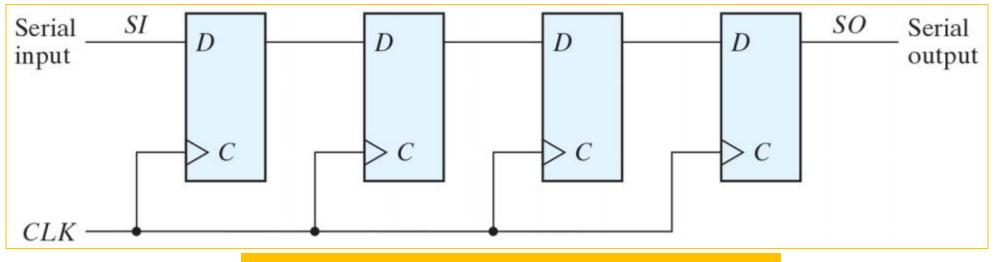

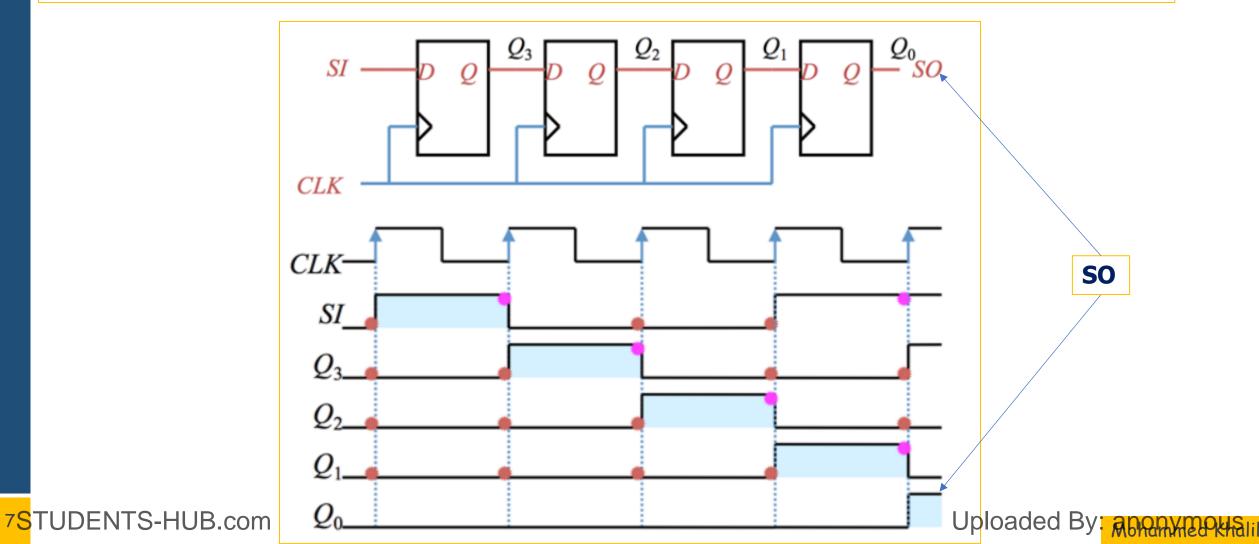

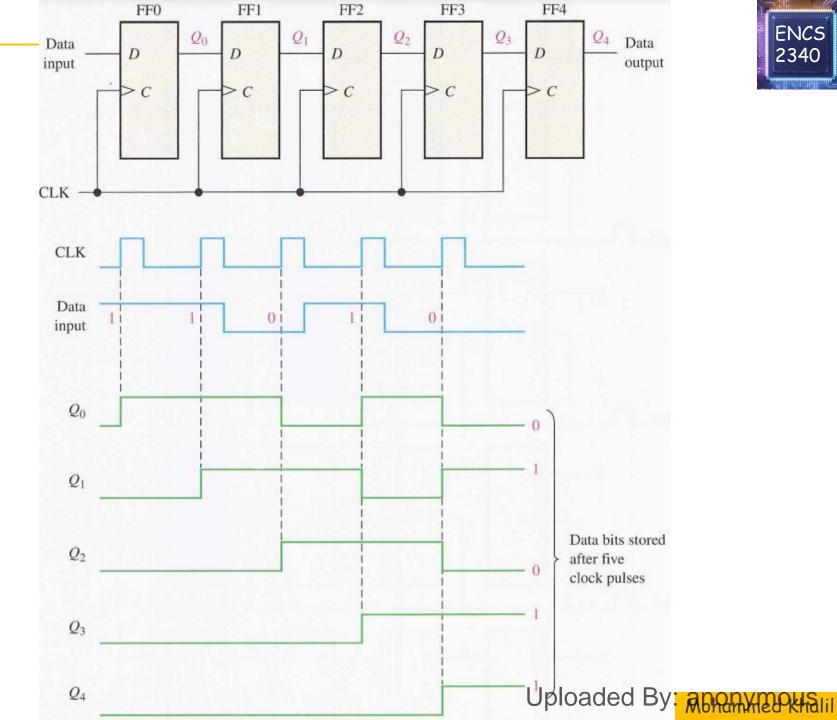

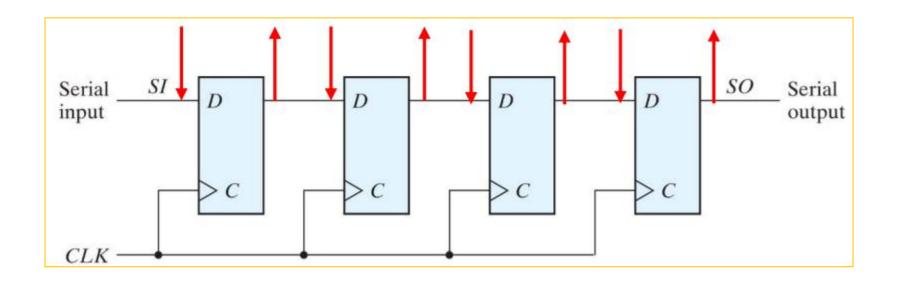

- S A shift register is a register that is capable of shifting (moving) the binary information held in each cell to its neighboring cell, in a selected direction

- S A shift register consists of a chain of flip-flops in cascade, with the output of one flip-flop connected to the input of the next flip-flop

- Solution Service Se

With **each** clock cycle, the data will **move** from one **FF** to its **adjacent** one. The **SI** will get to the **far-left** FF and the **SO** will get out from the **right-most** FF

6STUDENTS-HUB.com

Unidirectional (left-to-right) 4-bit Shift register

Uploaded By: aponymousli

- Some shift register is **unidirectional** (Does not support a left shift)

- The **serial input** determines what goes into the **leftmost** flip-flop during the shift.

- So The serial output is taken from the output of the rightmost flip-flop

- A **clear/reset** signal is required in practical designs (to reset the whole register to zero)

S-bit shift-right register

Solution States (Section 2014) Solution (Section 20

**8S**TUDENTS-HUB.com

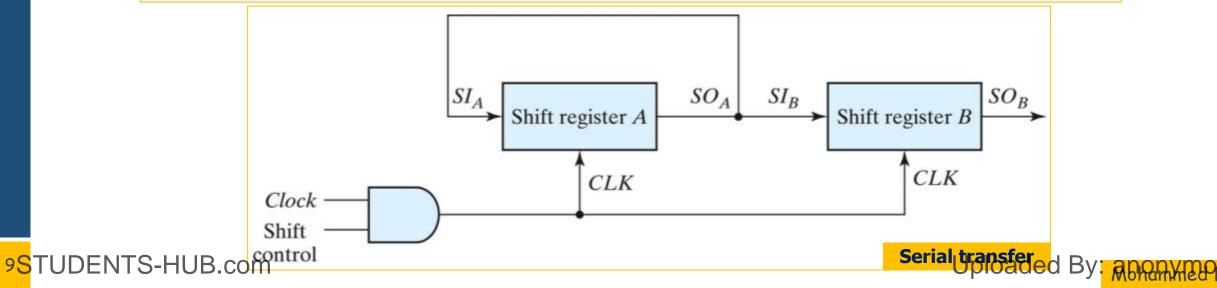

- S Two main **Operation mode** for any digital system:

- 1) Serial mode: data is transferred and processed one bit at a time

- Take **more time** to process a collection of data (**Slower**)

- The hardware needed is **for a single bit (Simpler**)

- Examples: USB cables, RS232

- 2) Parallel mode: data is transferred and processed in parallel (All at once)

- Take only **1** clock cycle to process a collection of data (**Faster**)

- The hardware needed is for a n-bits (More Complex)

- Examples: Internal Memory Bus

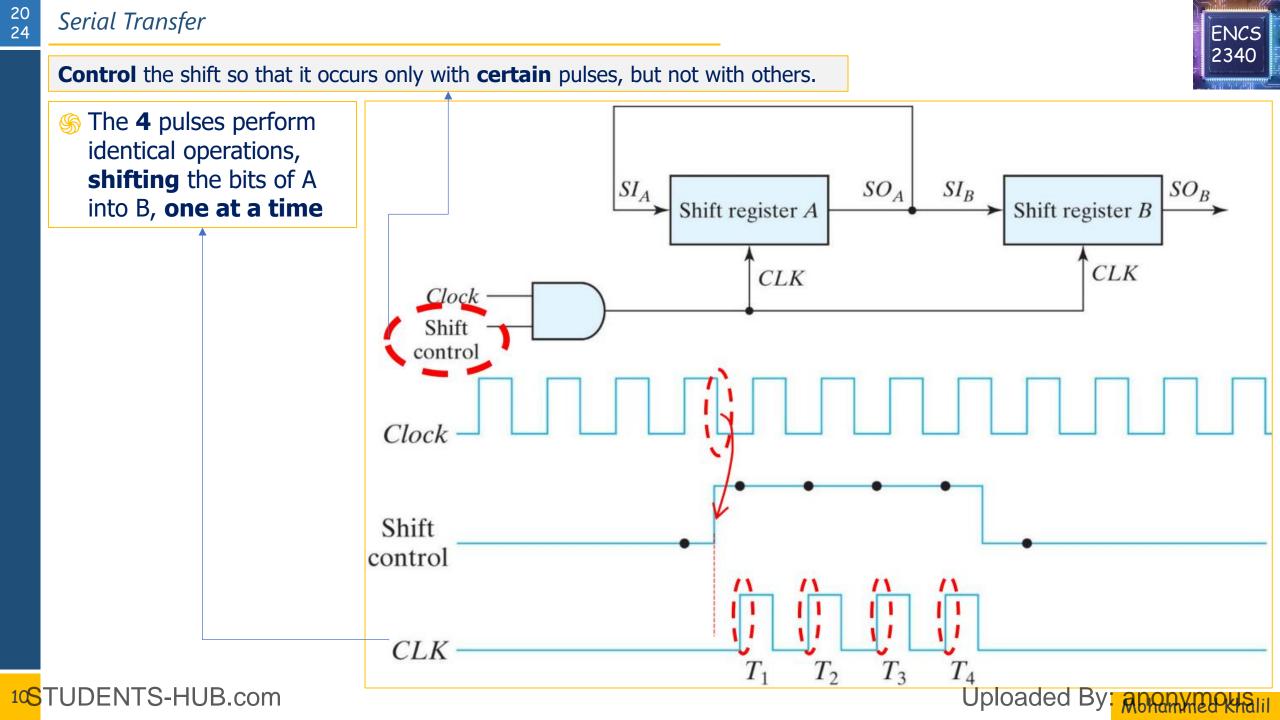

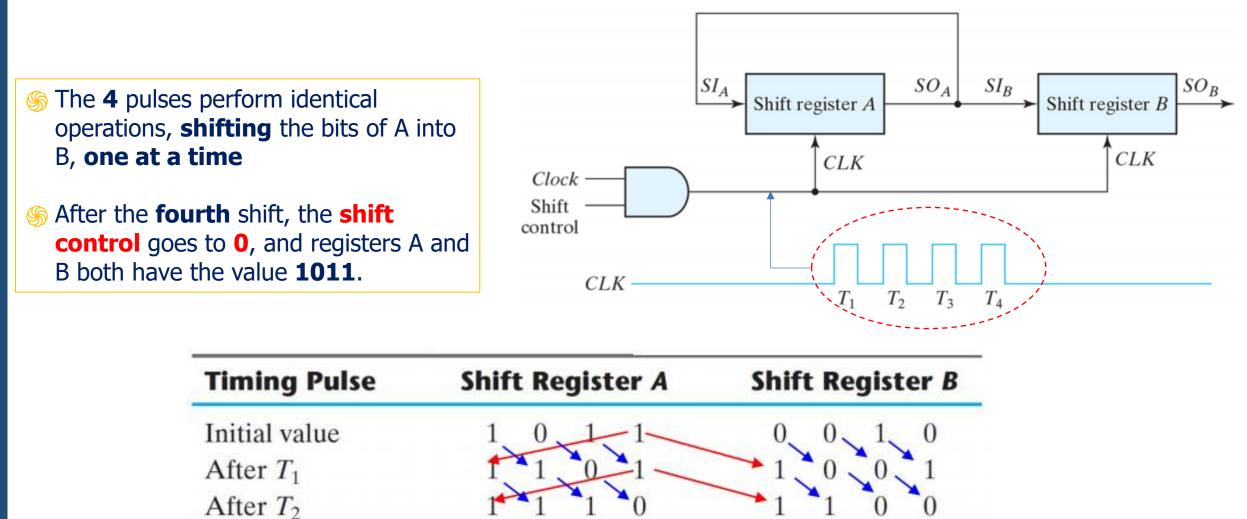

Each Register has **n-bits**. The contents of A are **copied** into B, so that the contents of A remain **unchanged** (i.e., the contents of A are **restored** to their **original** value)

ENCS 234<u>0</u>

<sup>11</sup>STUDENTS-HUB.com

After  $T_3$

After  $T_4$

Uploaded By: ADONY MORIA

0

0

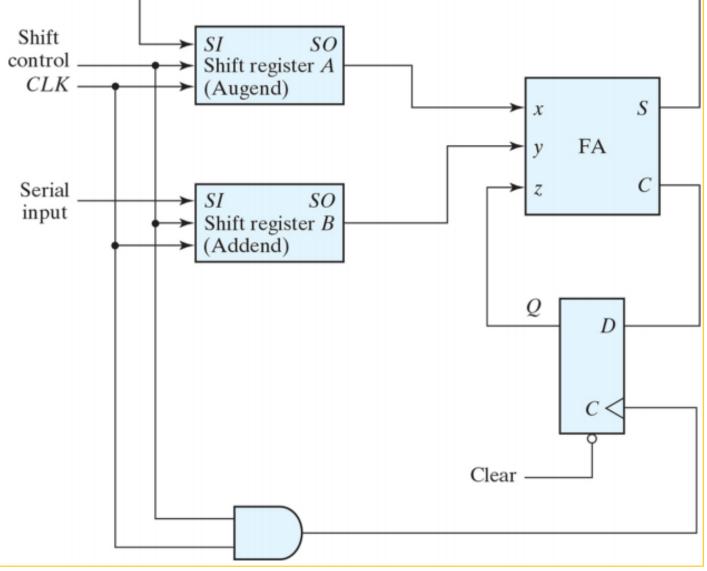

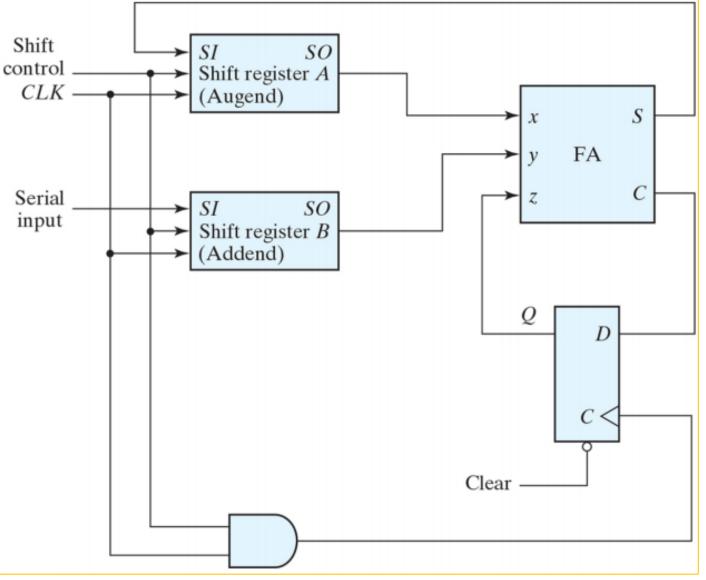

#### Serial Adder: sequential circuit that performs serial addition

- S The inputs comes from two shift registers (A,B)

- S A single full adder is used to add one pair of bits at a time along with the carry

- S The result is stored back into one of the shift registers (A)

- Solution The carry out is stored in a D-FF and is then used as the carry input for the next pair of significant bits

Only **1-FA** is used compared to **n** FAs in the **n**-bit binary adder

12STUDENTS-HUB.com

Uploaded By: ADAMYROUSII

### ENC5 2340

#### **Shift control signal** is used to control when the registers will be shifted $\rightarrow$ control the next 2-bits addition

- Segisters A & B hold the two binary numbers to be added

- Solution → Solutio

- Solution SO of both registers are connected to the inputs of the FA

- Solution The output of the FF is connected to the carry-in input of the FA

- S is connected to SI of register A

- Solution Soluti Solution Solution Solution Solution Solution Solution S

After applying **n** clock pulses the sum **result** is stored in register (**A**)

13STUDENTS-HUB.com

Uploaded By: aponymerkisiii

S

С

#### Example: 4-bit serial adder

|                    |      |      |   |   |           | Shift<br>control | SI SO                                             |            |

|--------------------|------|------|---|---|-----------|------------------|---------------------------------------------------|------------|

| CLK                | А    | В    | S | С | Q         |                  | Shift register A<br>(Augend)                      | → x        |

|                    | 1001 | 0111 | 0 | 1 | 0         |                  | Г                                                 | → y FA     |

| 1                  | 0100 | 0011 | 0 | 1 | 1         | Serial<br>input  | $\rightarrow SI SO$ Shift register B $(A dd and)$ |            |

| 2                  | 0010 | 0001 | 0 | 1 | 1         |                  | (Addend)                                          |            |

|                    | 0001 | 0000 | 0 | 1 | 1         |                  |                                                   |            |

|                    | 0000 | 0000 |   |   | 1         |                  |                                                   | <i>c</i> < |

| 1001+0111 = 10000! |      |      |   |   | <b>)!</b> |                  |                                                   | Clear      |

14STUDENTS-HUB.com

Uploaded By: Abon Mederlain

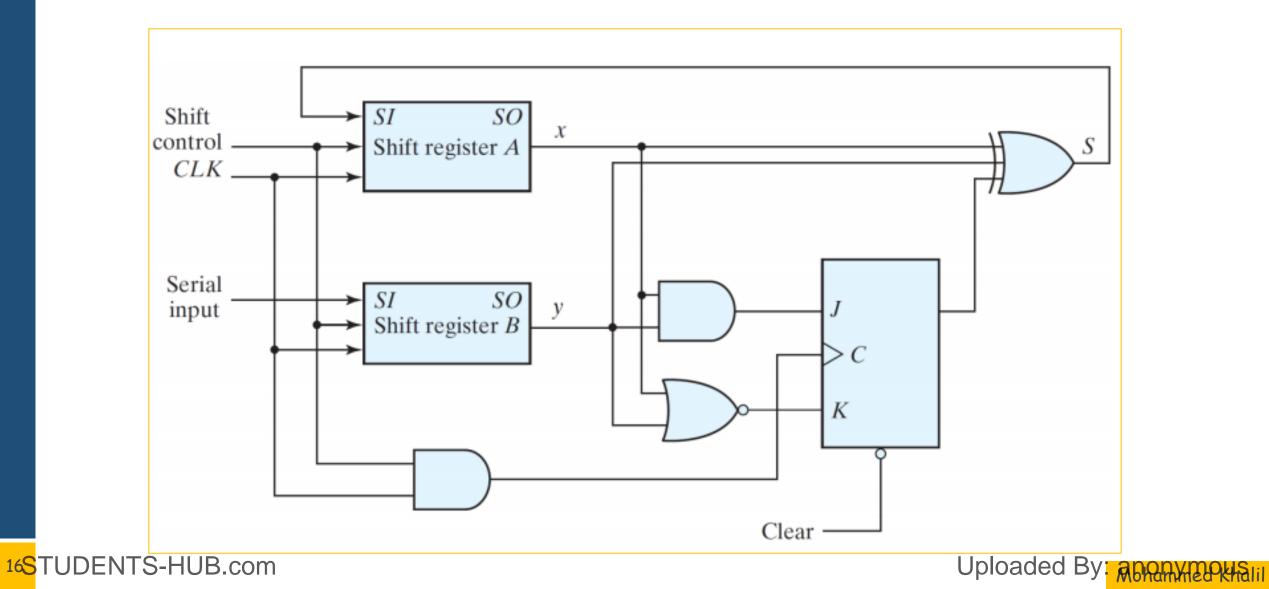

- Sollow a sequential circuit design approach and use JK-FF to store the carry

- S Let the **LSB** bits from Reg.A and Reg.B → **x** and **y**

- S x and y are available for every CLK since the Shift-Reg will provide a new x and y for each CLK

- S The circuit will have: Two **inputs**, x, y, **Output** S for the sum , Carry that is stored in **Q**

|                 | Present State |   | uts | Next State         | Output | Flip-Flop Inputs |    |

|-----------------|---------------|---|-----|--------------------|--------|------------------|----|

| C <sub>in</sub> | Q             | x | y   | C <sub>out</sub> Q | S      | Jq               | Kq |

|                 | 0             | 0 | 0   | 0                  | 0      | 0                | Х  |

|                 | 0             | 0 | 1   | 0                  | 1      | 0                | X  |

|                 | 0             | 1 | 0   | 0                  | 1      | 0                | Х  |

|                 | 0             | 1 | 1   | 1                  | 0      | 1                | Х  |

|                 | 1             | 0 | 0   | 0                  | 1      | X                | 1  |

|                 | 1             | 0 | 1   | 1                  | 0      | X                | 0  |

|                 | 1             | 1 | 0   | 1                  | 0      | Х                | 0  |

|                 | 1             | 1 | 1   | 1                  | 1      | X                | 0  |

$$J_{Q} = xy, \ K_{Q} = x'y' = (x+y)', \ S = x \oplus y \oplus Q$$

15STUDENTS-HUB.com

$$J_{Q} = xy, \ K_{Q} = x'y' = (x+y)', \ S = x \oplus y \oplus Q$$

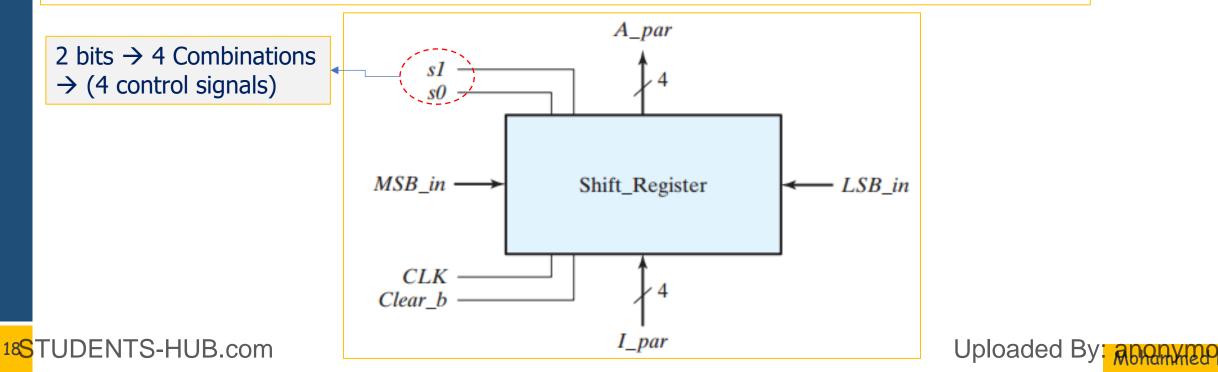

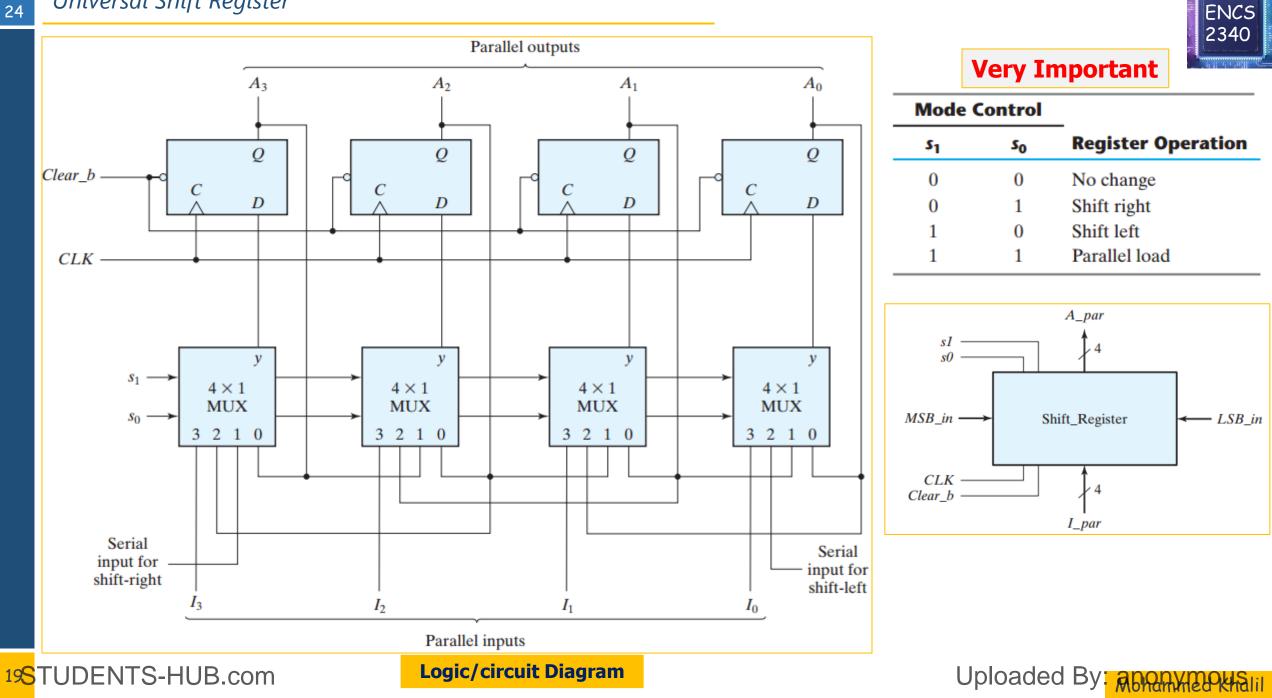

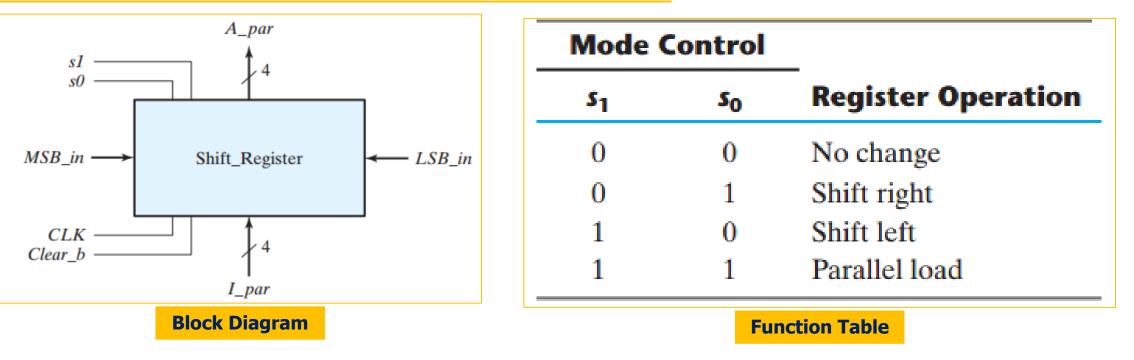

A register that can shift in one direction (left or right) is called a unidirectional shift register

A register that can shift in both directions is called a bidirectional shift register

A register that can shift in both directions and has a parallel load capability is called a Universal Shift Register

#### **Solution Shift Register:**

- The data entered serially by shifting can be taken out in parallel from the outputs of the flip-flops

- The data entered in parallel can be taken out in serial fashion by shifting the data stored in the register

17STUDENTS-HUB.com

Uploaded By: Anonymous

- So The Universal Shift Register has the following capabilities:

- A **clear** control to clear the register to 0

- A **clock** input to synchronize the operations

- A shift-right control to enable the shift-right operation

- A **shift-left control** to enable the shift-left operation

- A **parallel-load** control to enable a parallel transfer

- A **control** that leaves the data in the register **unchanged** in response to the clock

- The serial input and output lines

- **n parallel input lines** associated with the parallel transfer

- **n parallel output lines** associated with the parallel transfer

**4** Control Signals

ENCS 2340

#### Universal Shift Register

20 24

Universal Shift Register

20 24

S Universal Shift registers are often used to interface digital systems situated **remotely** from each other

- S It will be **expensive** to use **n lines** to **transmit n bits** in **parallel** for a long distance.

- S It is more economical to use a single line and transmit the information serially

- Solution for the second sec

- Solution The receiver accepts the data serially into a universal shift register and then it can be taken from the outputs of the register in parallel

- S The transmitter performs a parallel-to-serial conversion of data

- S The receiver does a serial-to-parallel conversion

- In real life, A counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred.

- S A Counter is a register that goes through a prescribed sequence of states upon the application of input pulses

- 1) Input pulses may be **clock** pulses (CLK)

- 2) Input may originate from **external** sources (Example: other signals like A, B, etc.)

- S There are two types of counters:

- 1) Synchronous Counters

- S Input sequence occurs at a **fixed** interval of time

- All flip-flops are triggered by the same clock pulses.

- 2) Asynchronous Counters (Ripple Counters)

- Solution Input sequence occurs at **random** (input occurrence time is not pre-defined)

- **C** Each flip flop is triggered by the transition of other flip-flops.

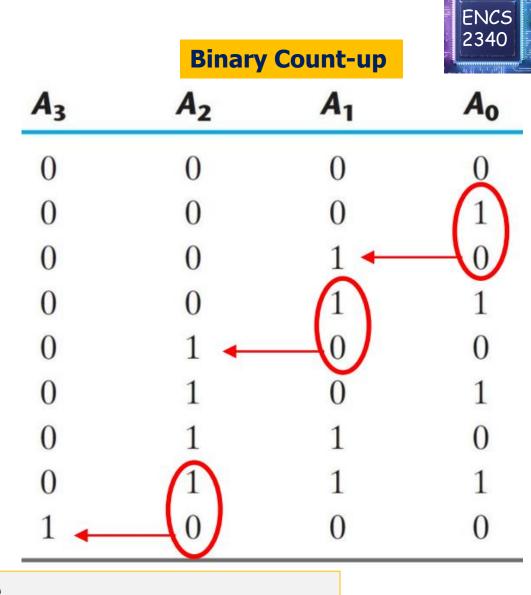

- A counter that follows the **binary** number **sequence** is called a **binary counter** (**n**-bit binary counter: count from **0** to **2<sup>n</sup> -1**)

#### <sup>21</sup>STUDENTS-HUB.com

Uploaded By: ADAMYROKISIII

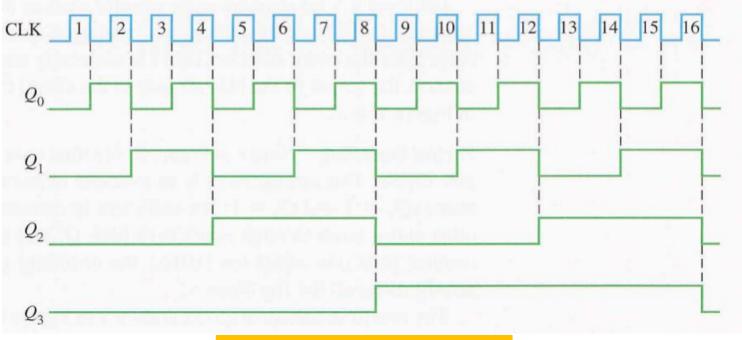

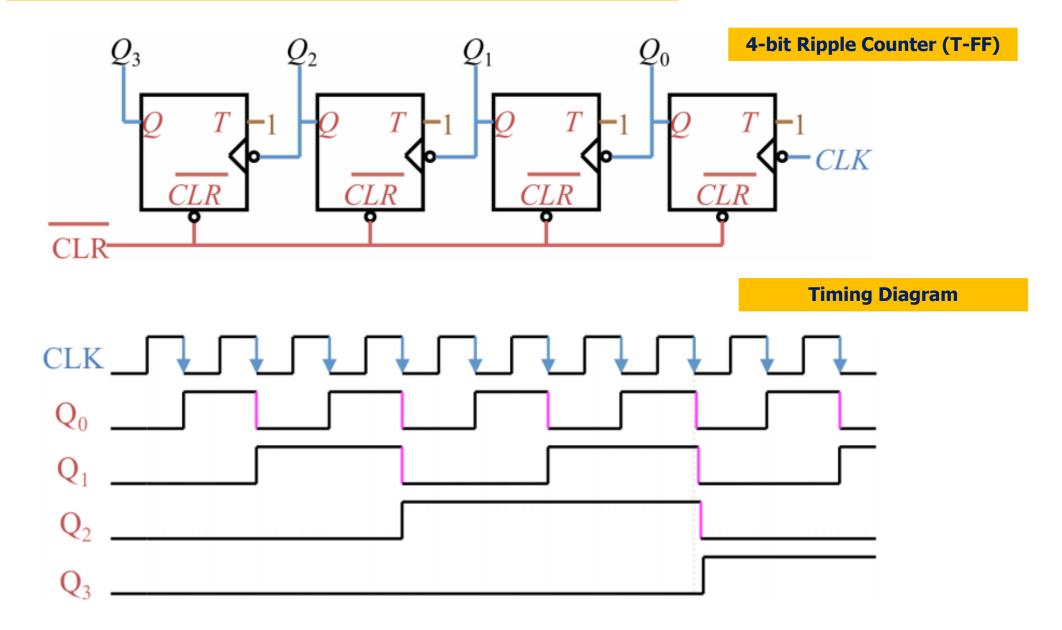

Binary Ripple Counters

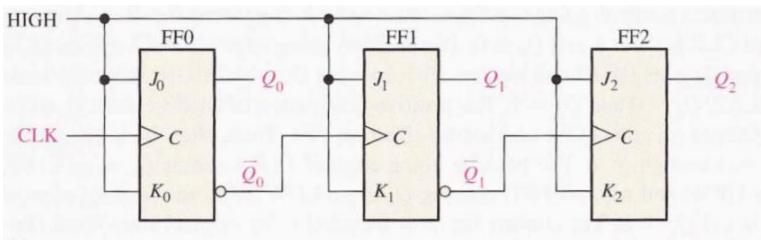

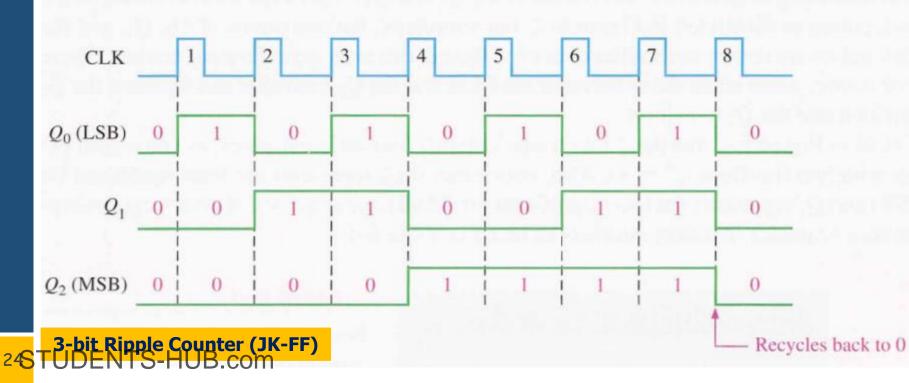

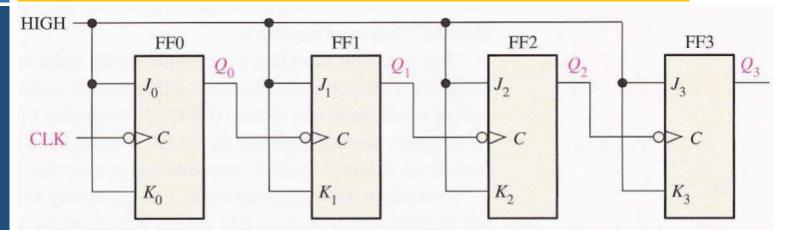

- In Ripple Counters, a flip-flop output transition serves as a trigger for other flip-flops. In other words, the CLK input of some or all flip-flops are triggered by the transition that occurs in other flip-flop outputs.

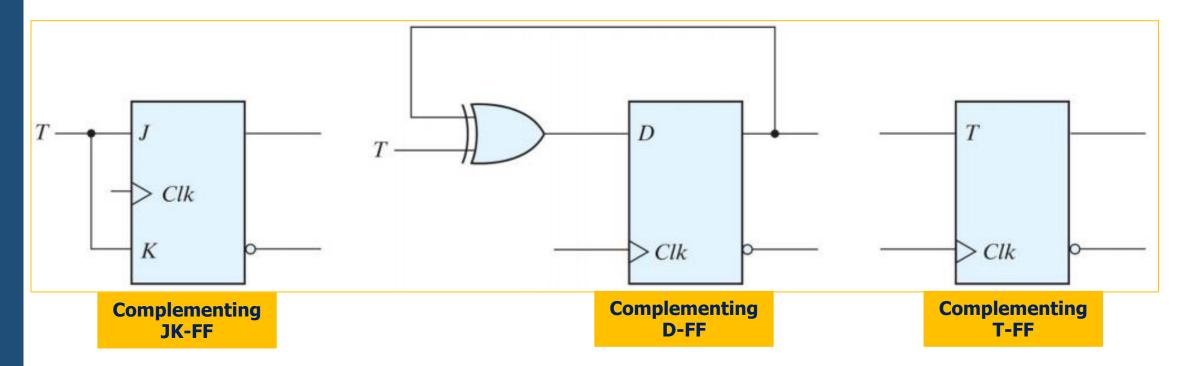

- Sinary ripple counter consists of a series of complementing flip-flops.

- Seither Count-up or Count-down

- Could be implemented using **D**, **T**, or **JK** FFs.

- Negative Edge or Positive Edge FFs could be used

- 1. The **first** FF is complemented **every** Clock Edge

- 2. The **second** FF is complemented when the **first** FF is **changed from 1**  $\rightarrow$  **0**.

- (The **first** FF **acts** as the **Clock** for the **second** FF).

22STUDENTS-HUB. Same Applied for higher FFs.

Uploaded By: Anonymoulail

#### 2-bit Ripple Counter (JK-FF)

| HIGH —                                                        | FF0                                                                                                       |                  | FF1             | CLOCK PULSE                                                                                                                           | $Q_1$                                        | $Q_0$ |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|

|                                                               |                                                                                                           |                  |                 | Initially                                                                                                                             | 0                                            | 0     |

|                                                               | $J_0 \qquad Q_0 \qquad P \qquad $ |                  |                 | Q <sub>1</sub> 1                                                                                                                      | 0                                            | 1     |

| CLK                                                           |                                                                                                           |                  | $\rightarrow c$ | 2                                                                                                                                     | 1                                            | 0     |

|                                                               | V                                                                                                         | $\overline{Q}_0$ | K,              | 3                                                                                                                                     | 1                                            | 1     |

|                                                               |                                                                                                           |                  |                 | 4 (recycles)                                                                                                                          | 0                                            | 0     |

| $CLK \qquad 1$ $\overline{Q}_{0}$ $Q_{0} (LSB)$ $Q_{1} (MSB)$ | 2                                                                                                         | 3                | 4               | Notice:<br>When <b>+Ve</b> Edge FF is<br>Connect <b>Q'</b> to the close<br>When <b>-Ve</b> Edge FF is<br><b>Q</b> to the clock of the | ck of the <b>n</b><br>s used $\rightarrow$ C |       |

23STUDENTS-HUB.com

20 24

Uploaded By: ADAMYROPHAIII

#### Binary Ripple Counters (Count-up, +Ve Edge)

(a)

20 24

S Transition of Q<sub>0</sub> from 1 to 0 triggers FF1 and it's output is complemented (Q<sub>1</sub> is complemented)

Similarly, as Q<sub>1</sub> changes from 1 to 0, FF2 is triggered (Q<sub>2</sub> is complemented)

S This is exactly what happens in binary counting

Notice:

When **+Ve** Edge FF is used → Connect **Q'** to the clock of the **next** FF

Uploaded By: anonymous

#### Binary Ripple Counters (Count-up, -Ve Edge)

(a)

20 24

#### Notice:

When -Ve Edge FF is used  $\rightarrow$  Connect **Q** to the clock of the **next** FF

### Uploaded By: ADON MEDIA

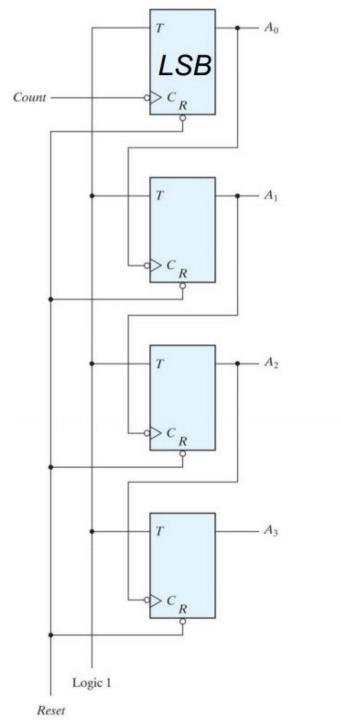

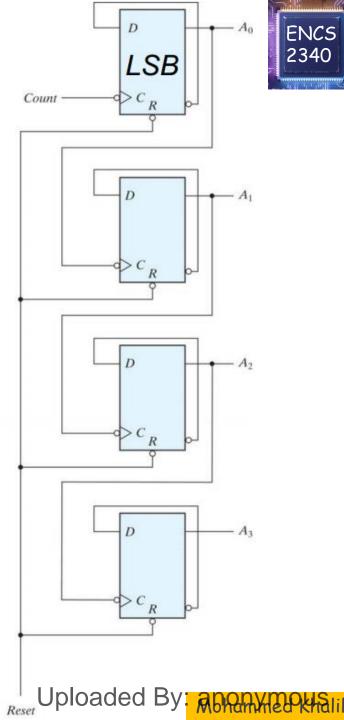

25STUDENTS-HUB.com4-bit Ripple Counter (JK-FF)

Binary Ripple Counters (Count-up, -Ve Edge)

4-bit Ripple Counter (T-FF & D-FF)

#### **Important Points**:

- To activate the complement Mode in JK/T FFs → connect Logic 1 (High) to the JK/T inputs.

- 2) To activate the complement Mode in D FFs → connect the inverted FF output (Q') back to the D input.

- Reset Signal usually used to clear/reset the counter to the initial count/state at any time.

- The CLK signal connected to the first FF is usually named Count

#### Notice:

When -Ve Edge FF is used  $\rightarrow$  Connect  $Q_{tothe Slock Bf the next FF}$

27STUDENTS-HUB.com

Uploaded By: Anonymerkialil

4-bit Ripple Counter (D-FF)

# $Q_3$ $Q_0$ CLK ю ю **Timing Diagram** CLK 0 0 $\cap$

28STUDENTS-HUB.com

20 24

Uploaded By: Anonymous

Uploaded By: ADONYMORKALII

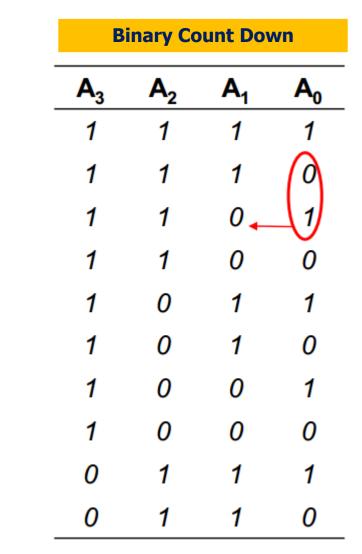

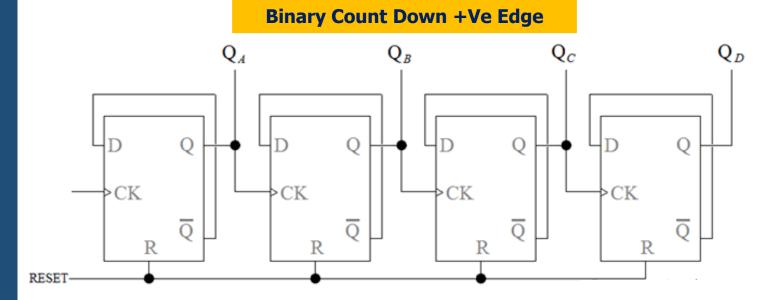

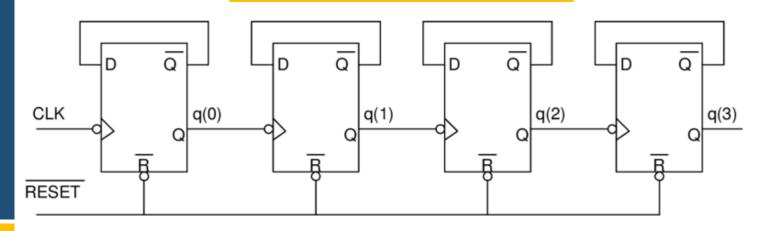

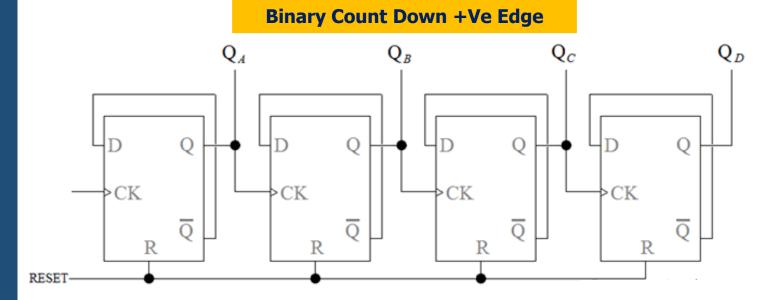

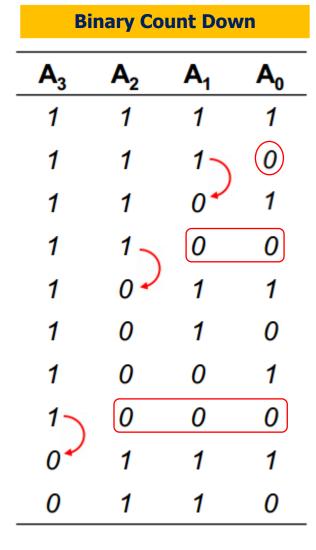

- S A binary count-down counter is a binary counter with a reverse count

- S Initial State is All 1s (4-bit counter starts with 1111)

- Solution Solution

- Same design as Count-up **Except**:

- When **+Ve** Edge FF is used → Connect **Q** to the clock of the **next** FF

- When -Ve Edge FF is used  $\rightarrow$  Connect Q' to the clock of the **next** FF

#### **Common Practice:**

Count-Up: Use **Negative** Edge Count-Down: Use **Positive** Edge

28 TUDENTS-HUB.com

## **Common Practice:** Use +Ve Edge FF $\rightarrow$ Connect Q to the clock of the **next** FF

Binary Count UP (-Ve Edge)

## **Common Practice:** Use -Ve Edge FF → Connect Q to the clock of the **next** FF

Uploaded By: anonymous

20 24

31STUDENTS-HUB.com

## **Common Practice:** Use +Ve Edge FF $\rightarrow$ Connect Q to the clock of the **next** FF

#### Binary Count UP (-Ve Edge)

## **Common Practice:** Use -Ve Edge FF → Connect Q to the clock of the **next** FF

Uploaded By: anonymous

32STUDENTS-HUB.com

20 24

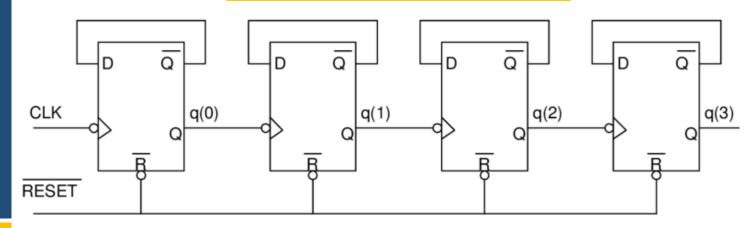

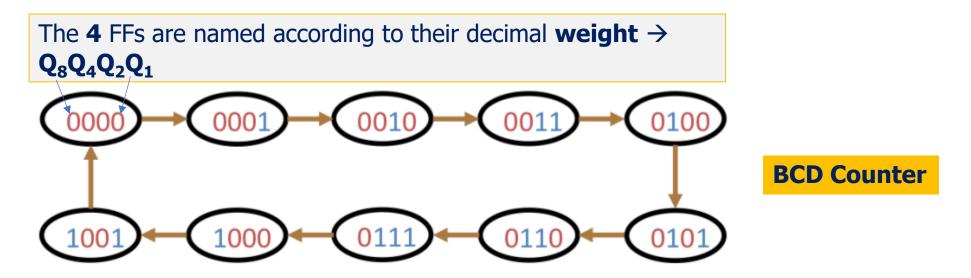

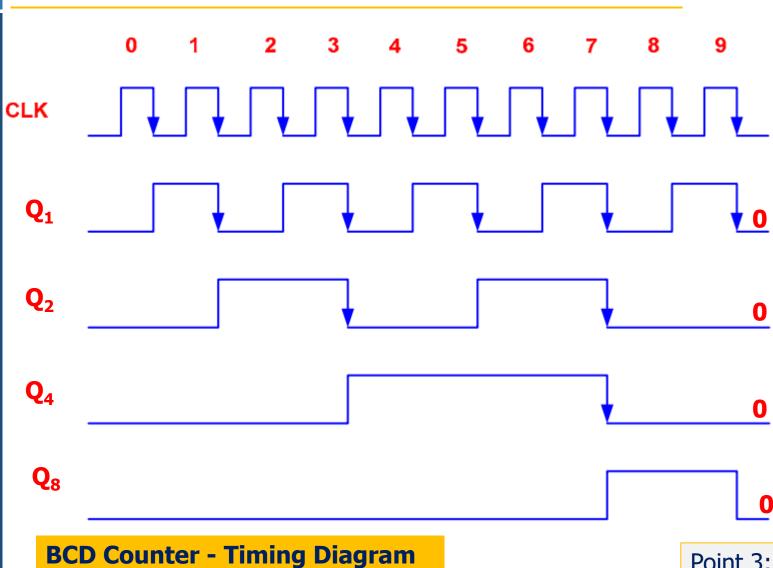

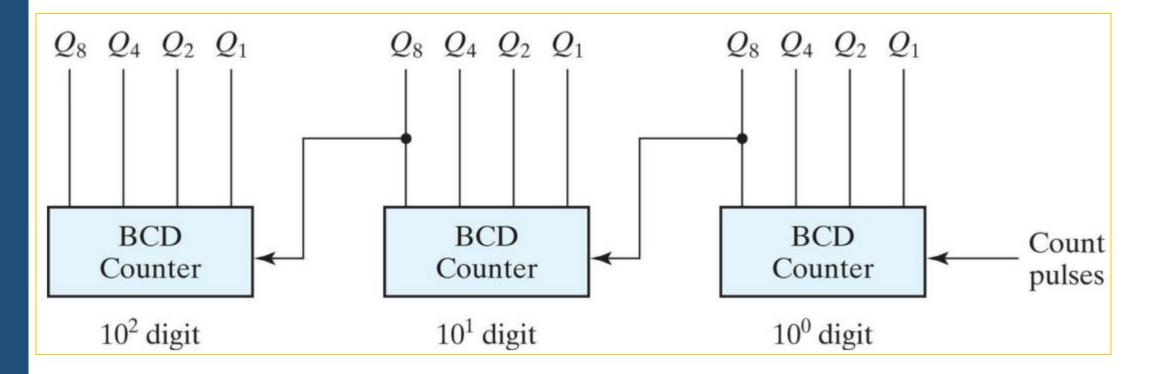

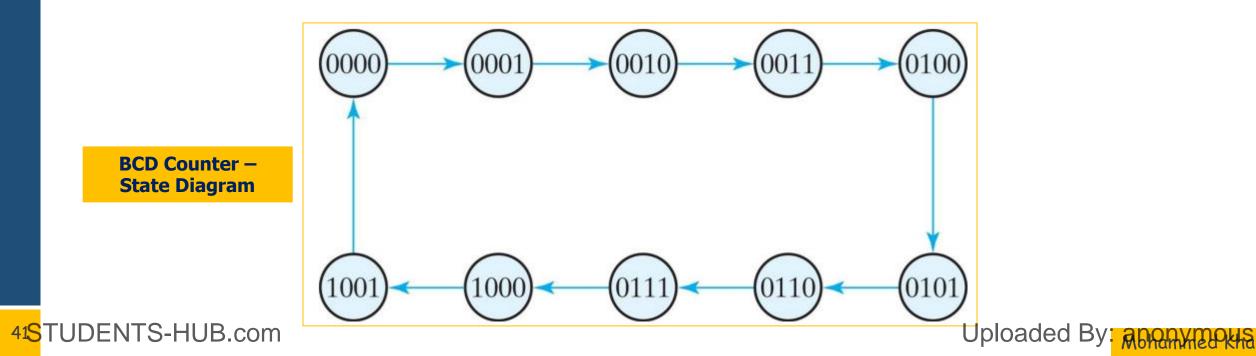

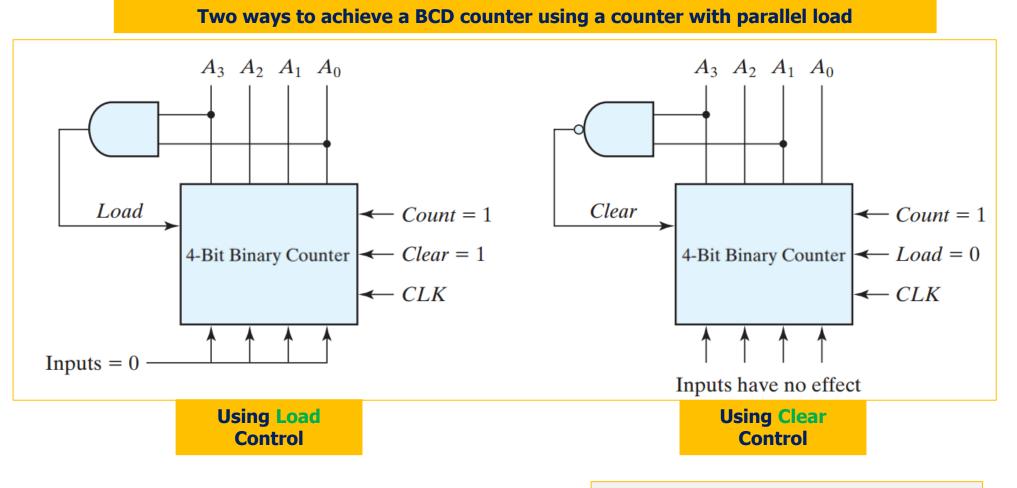

- S A decimal (BCD) counter follows a sequence of 10 states and returns to 0 after the count of 9

(Count 0→9 then restart to 0)

- ( **5 10** States → **4** FFs are needed ( $2^3 = 8$ , < 10 → 4 is needed)

- **BCD** counter sequence: **0000**  $\rightarrow$  **1001** then restart to **0000**

- Scommon Names: Decimal / BCD/ Decade

**Notice:**  $Q_8$  and  $Q_2$  FFs **reset** after the **10**<sup>th</sup> pulse In Binary Counter: 1001  $\rightarrow$  1010 (Both Q3,Q1 = 1)

Uploaded By: ADAMYROPHISIII

| No | tice:                                                                                                                 |

|----|-----------------------------------------------------------------------------------------------------------------------|

| 1) | <b>Q<sub>1</sub></b> <u>complements</u> after <b>each</b> clock pulse.                                                |

| 2) | $Q_2$ <u>complements</u> every time $Q_1$ goes from <b>1 to 0</b> , as long as $Q_8 = 0$ .                            |

| 3) | When $\mathbf{Q}_{8} = 1$ , $\mathbf{Q}_{2}$ <u>remains</u> at $0$ .                                                  |

| 4) | <b>Q</b> <sub>4</sub> <u>complements</u> every time <b>Q</b> <sub>2</sub> goes from <b>1 to 0</b> .                   |

| 5) | <b>Q<sub>8</sub></b> <u>remains</u> at <b>0</b> as long as <b>Q</b> <sub>2</sub> or <b>Q</b> <sub>4</sub> is <b>0</b> |

| 6) | When both $Q_2$ and $Q_4$ become 1, $Q_8$<br>complements when $Q_1$ goes from 1 to 0.                                 |

| 7) | ${f Q}_{8}$ is <u>cleared</u> on the next transition of ${f Q}_{1}$                                                   |

Point 3:  $\rightarrow$  Connect  $\mathbf{Q_8}'$  to **J** input of  $\mathbf{Q_2}$ Point 6:  $\rightarrow$  Connect  $\mathbf{AND}(\mathbf{Q_2}, \mathbf{Q_4})$  to **J** input of  $\mathbf{Q_8}$ Point 7:  $\rightarrow$  Connect  $\mathbf{Q_1}$  to the Clock of  $\mathbf{Q_8}$

33STUDENTS-HUB.com

Uploaded By: Anonymous

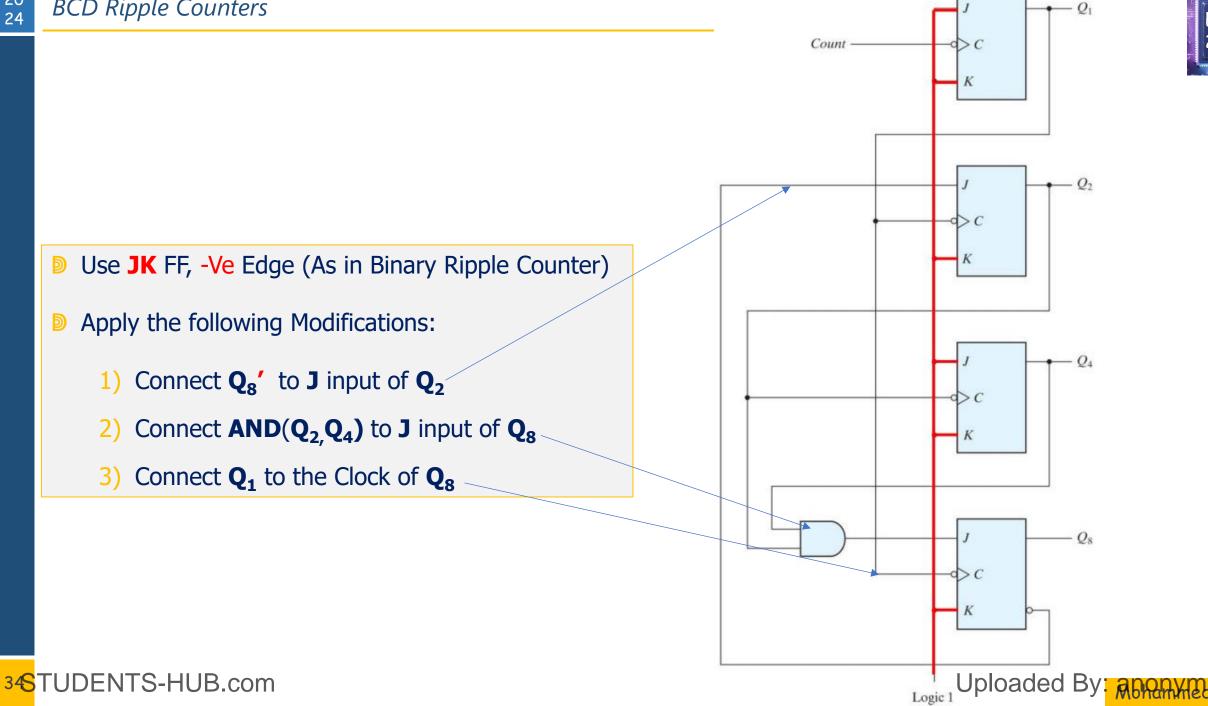

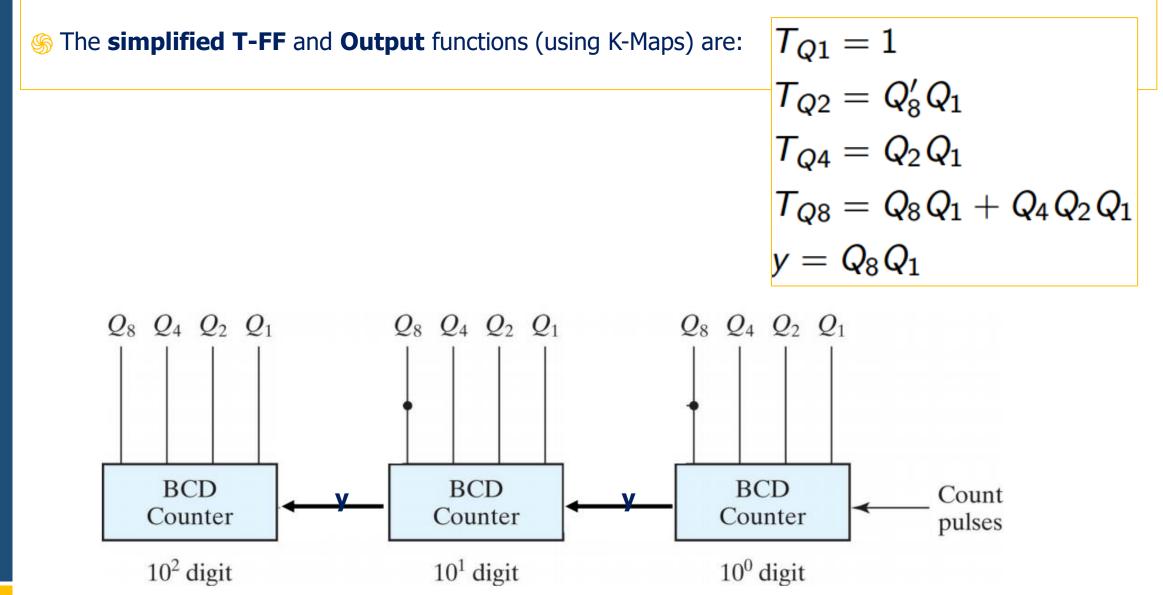

Solution We can cascade BCD counters (connect in series) to obtain multiple decimal digits counter

#### Solution 5 Sector 5 S

- **Three** BCD counters is needed (**One** for **Each** Digit)

- Constructed by connecting the BCD counters in cascade

Remember: All ripple counters are an asynchronous sequential circuits. Uploaded By: anonyme

ENCS 2340

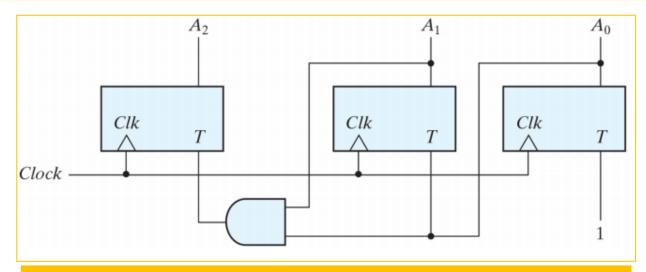

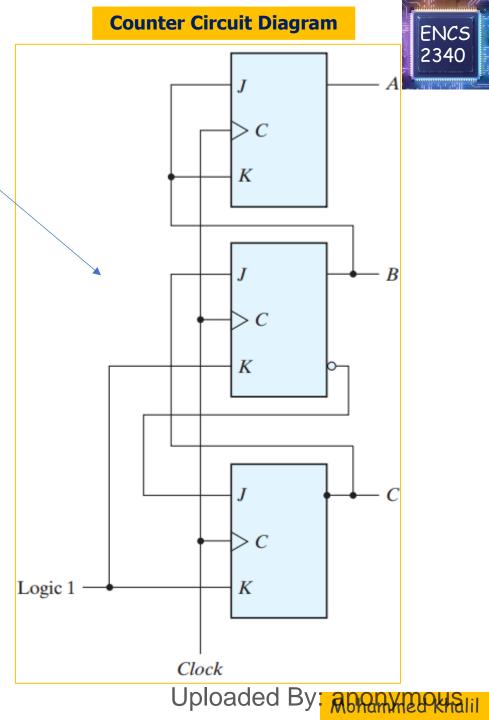

So Typically, their design procedure follows that for Sequential circuits

- Solution Stress Stre

- Solution (LSB) is complemented with every pulse

- S A flip-flop in any other position is complemented when all the bits in the lower significant positions are equal to 1

36STUDENTS bits Spickroppus Binary Up Counter using T-FF (Example in Ch-5)

| <b>Binary Co</b> |                           |                                                       |  |

|------------------|---------------------------|-------------------------------------------------------|--|

| A <sub>2</sub>   | A <sub>1</sub>            | Ao                                                    |  |

| 0                | 0                         | 0                                                     |  |

| 0                | 0                         | (1)                                                   |  |

| 0                | 1                         | 0                                                     |  |

| 0                | 1                         | D                                                     |  |

| 1                | 0                         | 0                                                     |  |

| 1                | 0                         | 1                                                     |  |

| 1                | 1                         | 0                                                     |  |

| 1                | 1                         | 1                                                     |  |

| 0                | 0                         | 0                                                     |  |

|                  | <b>A<sub>2</sub></b><br>0 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

ENCS 2340

- A<sub>0</sub> complements every time the count pulses go from 1 to 0

- A<sub>1</sub> complements only when A<sub>0</sub> is 1 and goes to 0

- A<sub>2</sub> complements only when A<sub>1</sub> and A<sub>0</sub> are 1 and going to 0

- A<sub>3</sub> complements only when A<sub>2</sub>, A<sub>1</sub> and A<sub>0</sub> are all 1 and going to 0

Uploaded By: anonymerkialil

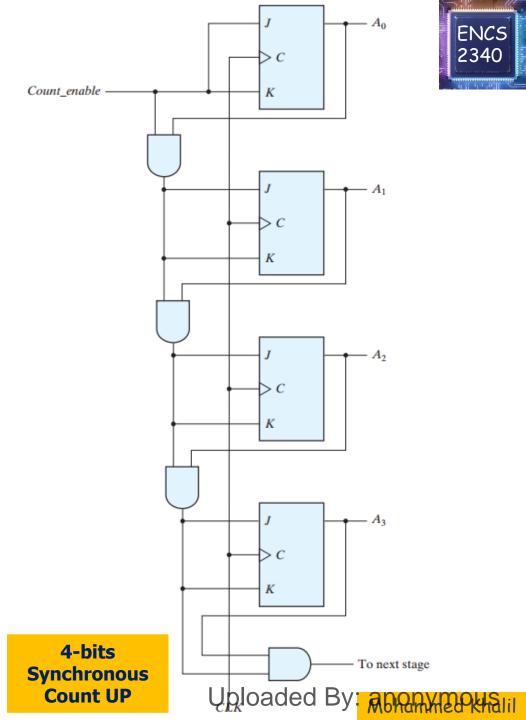

- Synchronous binary counters have a regular pattern and can be constructed with complementing flip-flops and gates

- Sount\_enables by Count\_enable

Sount\_enable = 0 → No Change

- Solution Stage Stage Stage Stages of Stages of Stages, with each stage having an additional FF and an AND gate

- Solution States of the synchronous counter can be designed with either the positive or the negative clock edge

37STUDENTS-HUB.com

S As stated earlier, Synchronous counters need to be designed with **complementing** Flip-Flops

# She **complementing** FF in can be of either the **JK** type, the **T** type, or the **D** type with **XOR** gates

#### Notice:

T-FF: is a complementing FF by its nature

**JK-FF**: can be <u>converted</u> to a **complementing** FF (T-FF), by **connecting both J,K** to **same input D-FF**: can be <u>converted</u> to a **complementing** FF (T-FF), by **XOR both** the **Present State** and the **input**

#### 38STUDENTS-HUB.com

# Uploaded By: ADAMYROCHSIII

- S A synchronous count-down binary counter goes through the binary states in reverse order, from 1111 down to 0000 and back to 1111

- Solution The bit in the least significant position(LSB) is complemented with each pulse

- S A bit in any other position is complemented if all lower significant bits are equal to 0

- S A countdown binary counter can be constructed as up counter, except that the inputs to the AND gates must come from the complemented outputs of the FF (Q')

Uploaded By: ADDAN/2004

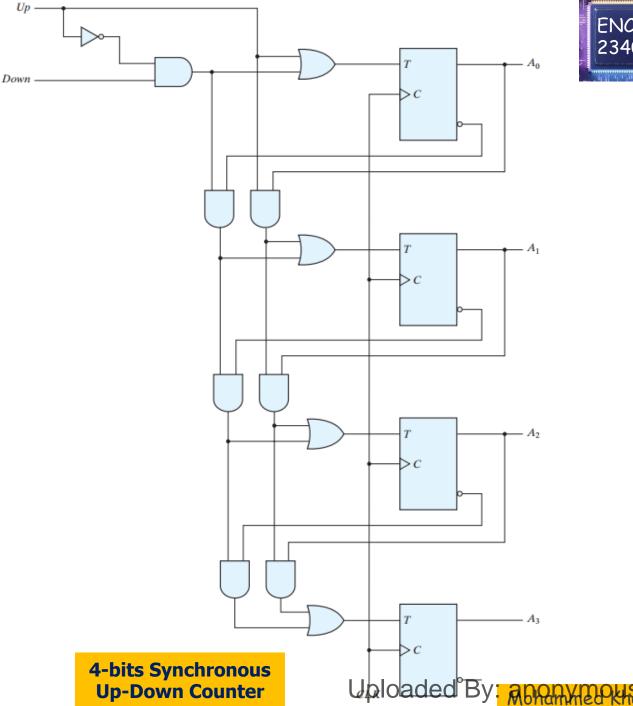

- S The two (Up & Down) counters can be combined in one circuit to form a counter capable of counting either up or down

- Solution Inputs Inputs Solution Inputs 1. Up = 0 & Down = 0  $\rightarrow$  **Don't Count** 2. Up = 0 & Down = 1  $\rightarrow$  Count **Down**

- 3. Up = 1 & Down = X  $\rightarrow$  Count **Up**

- This set of conditions ensures that only **one** S operation is **performed** at any given time

The **Up** input has **priority**

| Up | Down | Operation |

|----|------|-----------|

| 0  | 0    | Same      |

| 0  | 1    | Down      |

| 1  | x    | Up        |

40STUDENTS-HUB.com

- S A **BCD** counter counts in binary-coded decimal from 0000 to 1001 and back to 0000

- Secause of the return to 0 after a count of 9, a BCD counter does not have a regular pattern, unlike a straight binary count

- Solution for the circuit of a BCD synchronous counter, it is necessary to go through a sequential circuit design procedure

- S An **output** is defined, to **enable** the **next** decade counter (stage)

Solution for the state is 1001, to enable the count of the next-higher significant decade while the same pulse switches the present decade from 1001 to 0000

| Present State |            |                       | Next State            |                       |            |                       | Output     | Flip-Flop Inputs |                        |                        |                 |                        |

|---------------|------------|-----------------------|-----------------------|-----------------------|------------|-----------------------|------------|------------------|------------------------|------------------------|-----------------|------------------------|

| <b>Q</b> 8    | <b>Q</b> 4 | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>8</sub> | <b>Q</b> 4 | <b>Q</b> <sub>2</sub> | <b>Q</b> 1 | y                | <b>TQ</b> <sub>8</sub> | <b>TQ</b> <sub>4</sub> | TQ <sub>2</sub> | <b>TQ</b> <sub>1</sub> |

| 0             | 0          | 0                     | 0                     | 0                     | 0          | 0                     | 1          | 0                | 0                      | 0                      | 0               | 1                      |

| 0             | 0          | 0                     | 1                     | 0                     | 0          | 1                     | 0          | 0                | 0                      | 0                      | 1               | 1                      |

| 0             | 0          | 1                     | 0                     | 0                     | 0          | 1                     | 1          | 0                | 0                      | 0                      | 0               | 1                      |

| 0             | 0          | 1                     | 1                     | 0                     | 1          | 0                     | 0          | 0                | 0                      | 1                      | 1               | 1                      |

| 0             | 1          | 0                     | 0                     | 0                     | 1          | 0                     | 1          | 0                | 0                      | 0                      | 0               | 1                      |

| 0             | 1          | 0                     | 1                     | 0                     | 1          | 1                     | 0          | 0                | 0                      | 0                      | 1               | 1                      |

| 0             | 1          | 1                     | 0                     | 0                     | 1          | 1                     | 1          | 0                | 0                      | 0                      | 0               | 1                      |

| 0             | 1          | 1                     | 1                     | 1                     | 0          | 0                     | 0          | 0                | 1                      | 1                      | 1               | 1                      |

| 1             | 0          | 0                     | 0                     | 1                     | 0          | 0                     | 1          | 0                | 0                      | 0                      | 0               | 1                      |

| 1             | 0          | 0                     | 1                     | 0                     | 0          | 0                     | 0          |                  | 1                      | 0                      | 0               | 1                      |

42STUDENTS-HUB.com

**BCD** Counter – State Table (Using T-FF)

Uploaded By: ADAMYMERCHAII

43STUDENTS-HUB.com

**BCD Counter – 3 Stages**

Uploaded By: Anonymokialil

FUDENTS-HUB.com

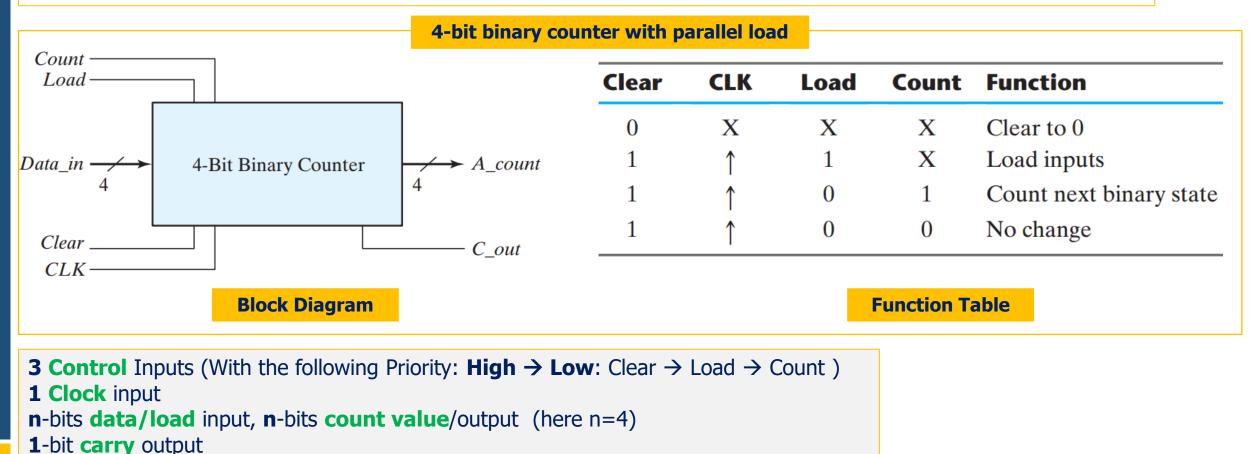

- Section 98 Section 2018 Section

- Sclear input is used to clear (reset to 0) the counter asynchronously

- Solution is set when the count reaches all 1's (saturate), to give indication to a following stage to start the count

```

Uploaded By: anonymous

```

ENCS 2340

#### S A counter with a parallel load can be used to generate any desired count sequence

Notice: **Clear** has the **highest** priority

ENCS 2340

20 24

# Binary Counter with Parallel Load

20 24

# ENCS 2340

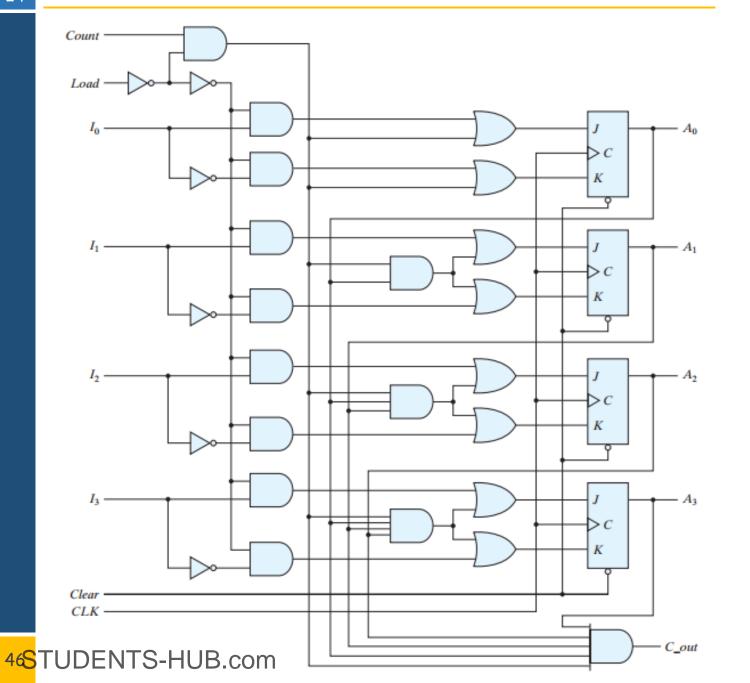

#### Circuit Diagram 4-bit binary counter with parallel load

Uploaded By: ADONY MORALII

# Binary Counter with Parallel Load

20 24

# ENCS 2340

#### Circuit Diagram 4-bit binary counter with parallel load

Uploaded By: ADOM Medeus

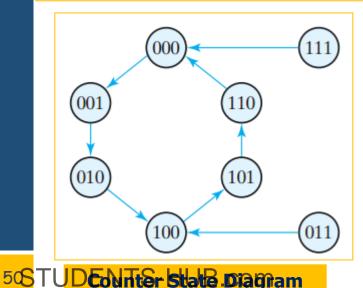

- Sounters can be designed to generate **any** desired **sequence** of states

- So The sequence may follow the **binary** count or may be any other **arbitrary** sequence

- Sounters are used to generate timing signals to control the sequence of operations in a digital system

- Sounters can also be constructed by means of shift registers

- So We will briefly discuss:

- Counter with **Unused** States

- Ring Counter

- Johnson Counter

49STUDENTS-HUB.com

20 24

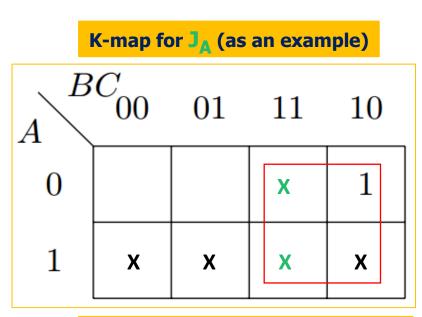

# **Example:** Design a counter that repeats (0,1,2,4,5,6) using **JK** flip-flops

#### **2 Unused** States (**011,111**). These shall be considered as **Don't Care** in the state table

| Pre                  | sent S | itate         | Ne      | Next State                               |         |       | Flip-Flop Inputs |                |                |    |    |  |  |

|----------------------|--------|---------------|---------|------------------------------------------|---------|-------|------------------|----------------|----------------|----|----|--|--|

| Α                    | B      | С             | Α       | В                                        | С       | JA    | K <sub>A</sub>   | J <sub>B</sub> | K <sub>B</sub> | Jc | Kc |  |  |

| 0                    | 0      | 0             | 0       | 0                                        | 1       | 0     | Х                | 0              | Х              | 1  | Х  |  |  |

| 0                    | 0      | 1             | 0       | 1                                        | 0       | 0     | Χ                | 1              | Χ              | Х  | 1  |  |  |

| 0                    | 1      | 0             | 1       | 0                                        | 0       | 1     | Χ                | Х              | 1              | 0  | Х  |  |  |

| 1                    | 0      | 0             | 1       | 0                                        | 1       | Х     | 0                | 0              | Х              | 1  | Х  |  |  |

| 1                    | 0      | 1             | 1       | 1                                        | 0       | Х     | 0                | 1              | Х              | Х  | 1  |  |  |

| 1                    | 1      | 0             | 0       | 0                                        | 0       | Х     | 1                | Х              | 1              | 0  | Х  |  |  |

|                      |        |               | C       | ounte                                    | r State | Table |                  |                |                |    |    |  |  |

| $J_A$                | = ]    | B             | $K_A =$ | = <i>B</i>                               |         |       |                  |                |                |    |    |  |  |

| $J_B = C$ $J_C = B'$ |        | $K_B = K_C =$ | = 1     | Simplified JK equations<br>(using k-map) |         |       | 5                |                |                |    |    |  |  |

| $J_C = B'$           |        |               | $K_C$ = | = 1                                      |         |       |                  |                |                |    |    |  |  |

X: Original from JK Excitation Table X: From Don't Care of States: 3,7

Uploaded By: ADAMYMERCHAII

Counter with Unused States

#### **Example Continue:**

Since there are **two** unused states, we **analyze** the **circuit diagram** to determine their **effect**:

- If the circuit happens to be in state **011** because of an error signal, the circuit goes to state **100** after the application of a clock pulse

(B=1 → J<sub>A</sub>= K<sub>A</sub>=1, J<sub>C</sub>=0) → A will be complemented(1→0), C=0

(C=1 → J<sub>A</sub>=1) → B will be complemented (0 → 1)

- b)  $(C=1 \rightarrow J_B=1) \rightarrow B$  will be complemented  $(0 \rightarrow 1)$

- If the circuit happens to be in state **111** because of an error signal, the circuit goes to state **000** after the application of a clock pulse

a) Same as above

**Self-Correcting Counter**

- Solution Section Se

- In a self-correcting counter, if the counter happens to be in one of the unused states, it eventually reaches the normal count sequence after one or more clock pulses

- Solution An alternative design could use additional logic to direct/enforce every unused state to a specific next state

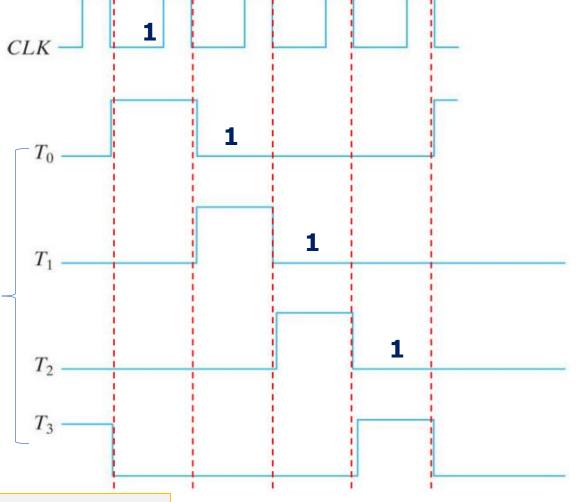

- In digital systems, we sometimes need a control signal that will trigger every 2<sup>n</sup>-1 cycles

- Such circuit is called a ring counter

- S A ring counter is a circular shift register with only one flip -flop being set at any particular time; all others are cleared

- Solution The **single** bit (which =1) is **shifted** from one flip-flop to the next to produce the sequence of timing signals

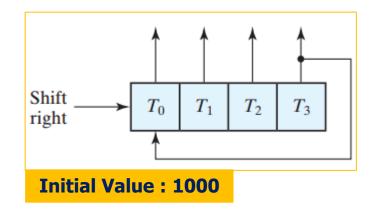

52 TUDEA Fach signal  $(T_{9} \rightarrow T_{3})$  is triggered (set to 1) after every 3 cycles (2<sup>2</sup>-1 = 3)

Uploaded By: anonymokisiii

Ring Counters

20 24

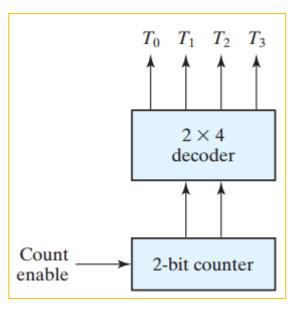

- So To generate **2**<sup>n</sup> timing signals, we can use:

- 1. A shift register with 2<sup>n</sup> flip-flops

- 2. An **n-bit** binary **counter** together with an **n-to-2<sup>n</sup> decoder**

Uploaded By: Anonymerking

- Sk-bit ring counter circulates a single bit among the flip-flops to provide k distinguishable states

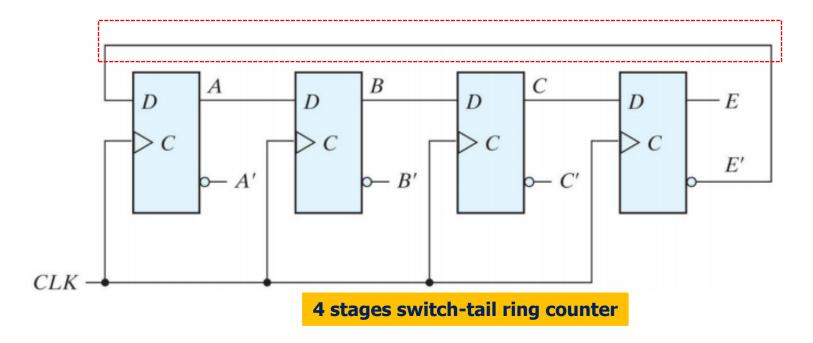

- Solution States in the shift register is connected as a switch-tail ring counter

- S A switch-tail ring counter is a circular shift register with the complemented output of the last flip-flop connected to the input of the first flip-flop

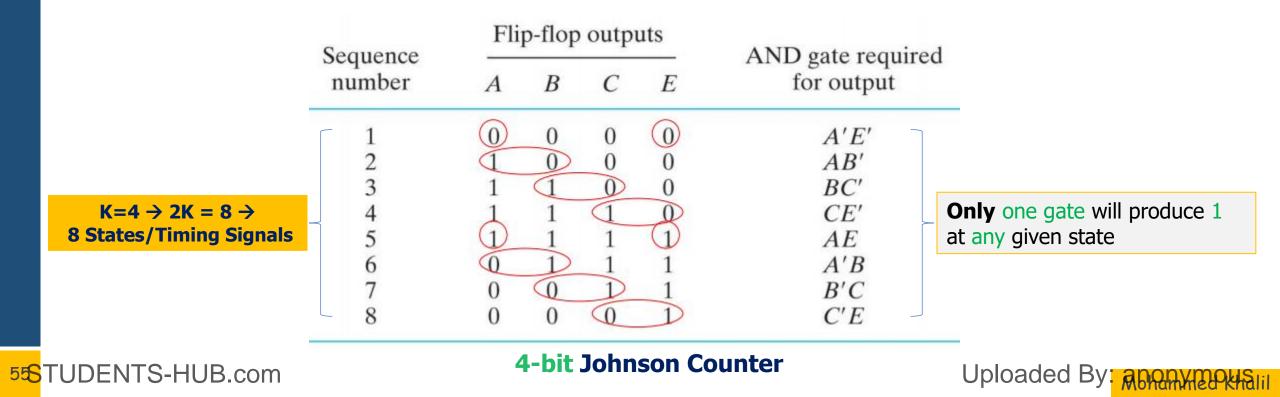

- S A Johnson counter is a k-bit switch-tail ring counter with 2k decoding gates to provide outputs for 2k timing signals

- Solution States Stat

- Section Base is enabled during one particular state sequence

The outputs of the gates generate eight timing signals in succession

- Some disadvantage of Johnson counter is that if it finds itself in an unused state, it will keep in moving from one invalid state to another and never find its way to a valid state (NOT Self-Correcting)

- Shis can be corrected by modifying the circuit to avoid this undesirable condition

- Solution One possible correction:  $D_c = (A + C)B$  (instead of  $D_c = B$ )

- Solution of timing sequences.

- 1. The number of **flip-flops** needed is **one-half** the number of **timing** signals.

- The number of decoding gates is equal to the number of timing signals, and only two-input gates are needed.