# **Experiment #8**

### Pre Lab

### Name: Mohammed Jamil Saada

Number: 1221972

## A) Build half adder on data flow.

#### Code:

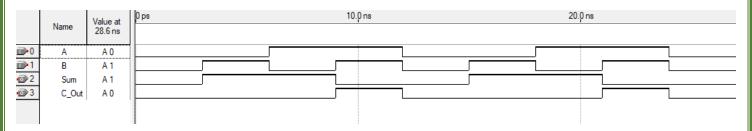

### Wave form:

## B) Build full adder using half adder structural.

## Code:

```

1  module Full_Adder(input A, B, C_in, output Sum, C_out);

2

3  //Mohammed Jamil Saada - 1221972

4  //Full Adder using Half Adder Structural

5

6  wire w1, w2, w3;

7  Half_Adder(A,B,w1,w2);

8  Half_Adder(C_in,w1,Sum,w3);

9  or gate(C_out,w2,w3);

10

11  endmodule

```

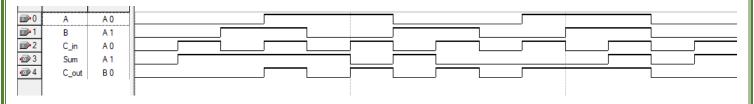

#### Wave form:

## C) Build a 2-bit counter on behavioral.

#### Code:

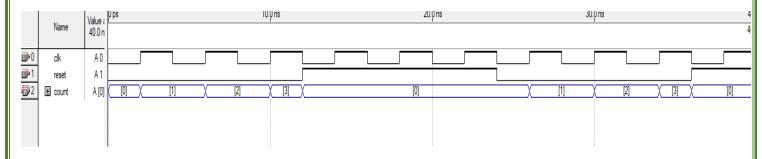

#### Wave form:

## D) Build an 8x1 Multiplexer on behavioral.

#### Code:

```

1 =module Mux 8to1(output reg F, input [7:0] I, input [2:0] selection);

//Mohammed Jamil Saada - 1221972

4 // 8x1 Multiplexer on behavioral

6 =always @(*) begin

7 = case (selection)

3'b000 : F = I[0];

3'b001 : F = I[1];

10 3'b010 : F = I[2];

11 3'b011 : F = I[3];

12 3'b100 : F = I[4];

13 3'b101 : F = I[5];

14 3'b110 : F = I[6];

15 3'b111 : F = I[7];

16 endcase

17 end

18 endmodule

```

#### Wave form:

|             |             | 680 <sub>,</sub> 0 ns |          |     | 690,0 ns |     | 700          | 700 <sub>.</sub> 0 ns |          | 710 <sub>,</sub> 0 ns |          | 720 <sub>i</sub> 0 ns |          |     |              |  |

|-------------|-------------|-----------------------|----------|-----|----------|-----|--------------|-----------------------|----------|-----------------------|----------|-----------------------|----------|-----|--------------|--|

|             | Name        |                       |          |     |          |     |              |                       |          |                       |          |                       |          |     |              |  |

| <b>™</b> 0  | H I         | X 010                 | 01010100 |     | 01010101 |     | ( 01010110 ) |                       | 01010111 |                       | 01011000 |                       | 01011001 |     | X 01011010 X |  |

| <b>™</b> 9  | ± selection | 000                   | 001      | 010 | 011      | 100 | 101          | 110                   | 111      | 000                   | 001      | 010                   | 011      | 100 | ( 101 )      |  |

| <b>⊚</b> 13 | F           |                       | 0        | 1   | ( O      | X 1 | 0            | 1                     |          | (                     | )        |                       | (        |     | ( 0 )        |  |

|             |             |                       |          |     |          |     |              |                       |          |                       |          |                       |          |     |              |  |

## E) Build a 2x4 Decoder using basic gates (structural).

#### Code:

```

1 =module Decoder 2to4(output D0, D1, D2, D3, input I0, I1);

3 //Mohammed Jamil Saada - 1221972

4 //2x4 Decoder using basic gates (stuctural)

6 wire i0, i1;

7 not gate1(i0, I0);

8 not gate2(i1,I1);

//i0 = I0' ,, i1 = I1'

9

10 and gate3(D0,i0,i1);

11 and gate4(D1, I0, i1);

and gate5(D2,i0,I1);

12

13

and gate6(D3, I0, I1);

14

15 endmodule

```

#### Wave form:

|            | Name | value at | 0 ps | 10. | Ons | Ons |   |

|------------|------|----------|------|-----|-----|-----|---|

|            |      | 30.0 ns  |      |     |     |     |   |

| <b>№</b> 0 | 11   | A1       |      | 0   |     | 1   | ) |

| <b>⊪</b> 1 | 10   | A 0      | 0    | 1   | 0   | 1   | 0 |

| <b>⊚</b> 2 | D0   | A 0      | 1    | X   | 0   |     | 1 |

| <b>⊚</b> 3 | D1   | A 0      | 0    | 1   |     | 0   |   |

| ₫ 4        | D2   | A1       |      | 0   | 1   | X   | 0 |

| <b>⊚</b> 5 | D3   | A 0      |      | 0   |     | 1   |   |

|            |      |          |      |     |     |     |   |

|            |      |          |      |     |     |     |   |

|            |      |          |      |     |     |     |   |

## F) Show the wave form for above parts.

I have attached the wave form for each part above.