# **Experiment #9**

## Pre Lab

Name: Mohammed Jamil Saada

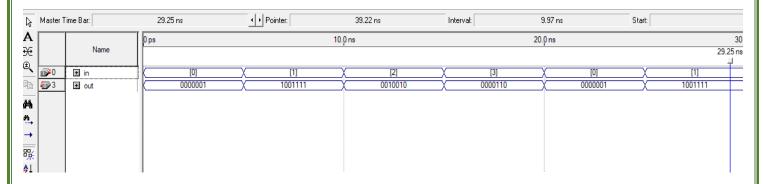

## 1) Design 4x2 priority encoder

#### Code:

```

priority_Encoder.v

Compilation Report - Flow Summary

priority_Encoder_Wave.vwf

Simulator Tool

1 //Design 4X2 priority encoder

=module priority_Encoder(output reg [1:0] out, input [3:0] in);

M

//Mohammed Jamil Saada - 1221972

{}

·

6 always @ (in)

Ē

7 if(in[3]==1) out[1:0] = 2'b11;

8 else if(in[2]==1) out[1:0] = 2'b10;

%

9 else if(in[1]==1) out[1:0] = 2'b01;

10 else if(in[0]==1) out[1:0] = 2'b00;

11 else out[1:0] = 2'b00;

12 endmodule

```

### Wave form:

Number: 1221972

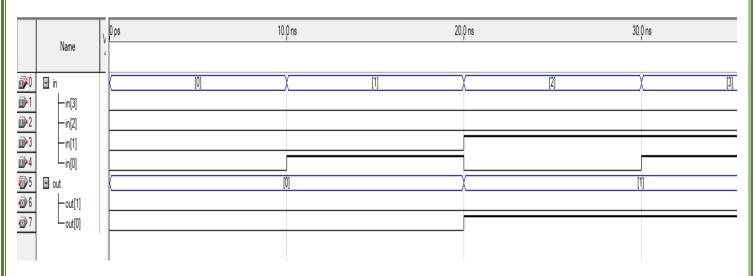

## 2) Design the 7-segment display

### Code:

```

seven_segment_display_driver.v

---

//Design the 7-segment display driver

2 module seven segment display driver(output reg [6:0]out, input [1:0] in);

åå

\mathbb{A}_{\mathbb{B}}

//Mohammed Jamil Saada - 1221972

4

5

∓≡

6 always @(in)

賃

7 =

begin

8 =

case(in)

%

9

0 : out = 7'b00000001;

1 : out = 7'b1001111;

%

10

11

2 : out = 7'b0010010;

%

3 : out = 7'b0000110;

12

0

13

endcase

\overline{Z}

14

end

V

15

endmodule

267

268

ab/

```

#### Wave form:

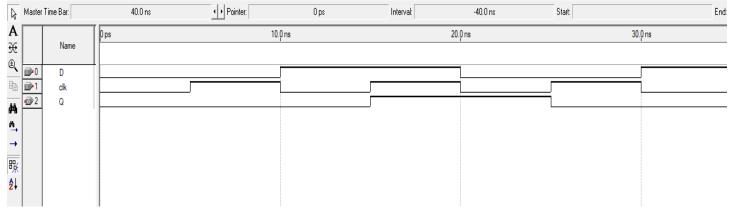

## 3) write and simulate the Verilog code of a D-Flip Flop

## Code:

```

//D-Flip Flop

1

2

■module D Flip Flop(output reg Q, input D,clk);

44

3

4

//Mohammed Jamil Saada - 1221972

7

5

•

6

always @ (posedge clk)

ŧ

7

O <= D;

endmodule

1

%

%

1/4

```

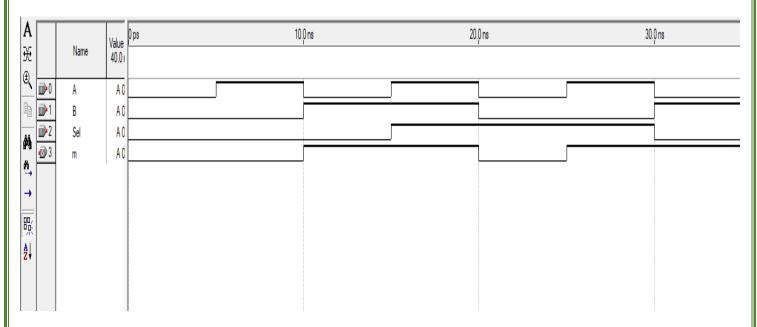

# 4) Write and simulate the Verilog code of 2x1 MUX.

### Code:

```

//2x1 MUX

1

2 module MUX_2x1(output reg m, input A, B, Sel);

3

//Mohammed Jamil Saada - 1221972

5

6

always @ (*)

7

if(Sel==0)

8

m = B;

9

else

10

m = A;

11

endmodule

```

## Wave form: