# DEPARTMENT OF COMPUTER SYSTEM ENGINEERING

Digital Integrated Circuits - ENCS333

# Dr. Khader Mohammad Lecture #1- Circuits & Layout

- Review: Basic R, L, and C

- IC Manufacturing and Design Metrics CMOS -Ch1 Sec 1.3, Ch2 Sec 2.2

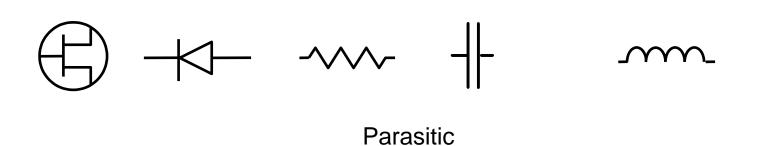

# Basic Elements of Electronic Circuits

| Transistor – is the switch                                       |             |

|------------------------------------------------------------------|-------------|

| Diode – is the rectifier                                         |             |

| Resistor - slows down electricity                                | - <b>^</b>  |

| Capacitor - stores electricity                                   | <del></del> |

| Inductor - determines the magnitude of the electromagnetic force |             |

| Connecting them with interconnects, an IC is obtained.           |             |

<sup>\*</sup>The elements, being prepared by discrete technology, are shown.

### Types of IC Elements

#### Useful

**Bipolar Transistors**

Resistances

Capacitances

Inductances

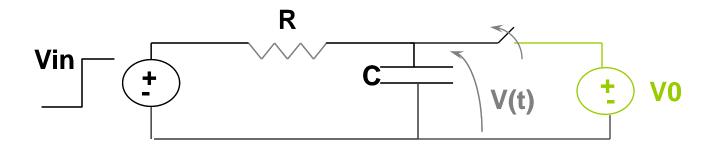

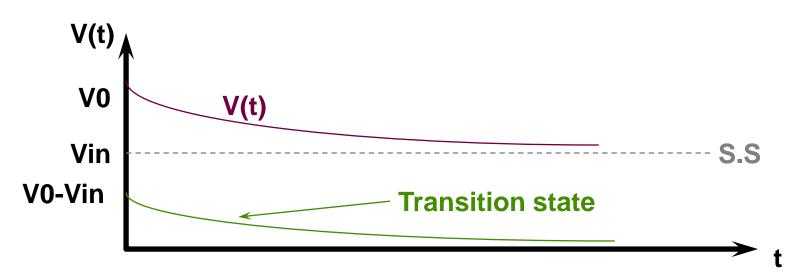

# Line model (RC Model)

•  $V(t) = V0 e^{-t/rc} + Vin (1 - e^{-t/rc})$

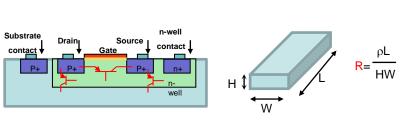

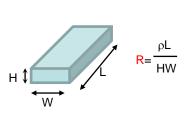

#### Interconnect Parasitics

- Parasitic = unwanted natural electrical elements

- Metal Resistance

- metals have a linear resistance and obey Ohm's law

- V = IR

- generate parasitic interconnect resistance, Rline

•

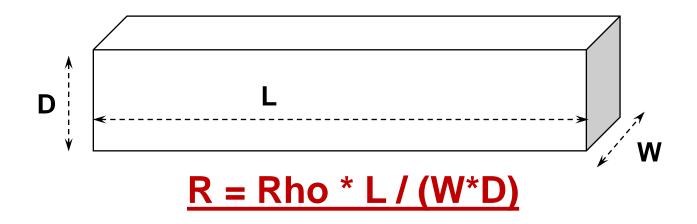

$$R_{line} = \frac{1}{\sigma A} = \frac{\rho 1}{A}$$

$$- A = wt$$

- $\rho$  = resistivity,  $\sigma$  = conductivity

- defined by sheet resistance

• Rs =

$$\frac{1}{\sigma t} = \frac{\rho}{t}$$

, resistance per unit square [ohms,  $\Omega$ ]

• Rline = Rs  $\frac{1}{w}$ , Rs determined by process,  $1 \le w$  by designer

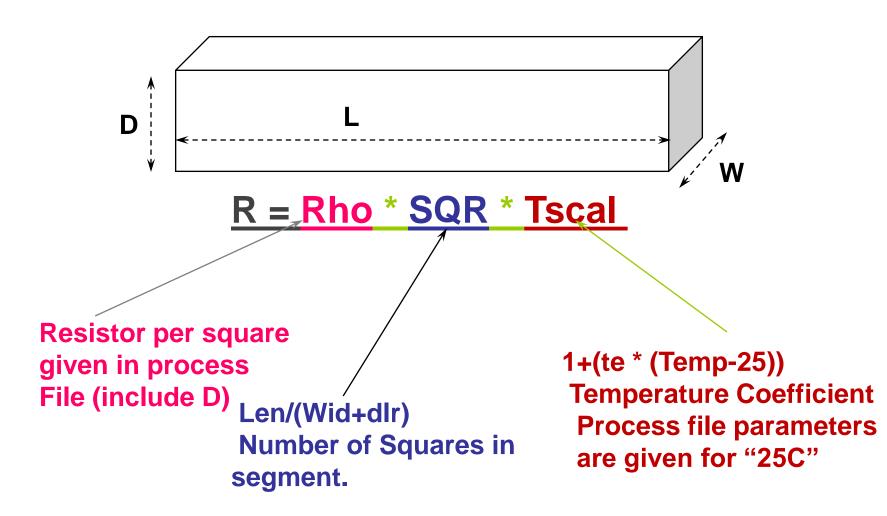

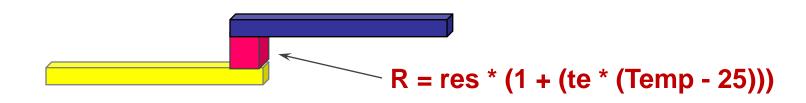

## Line Resistance Simple Model

- "D" is a process fixed number per layer

- We can set the Length <u>"L"</u>, and Width "<u>W"</u> of each segment

- This model does not include any temperature effect !!!

## Segment Resistance Model

# Segment Resistance Model Example

- The process files has two models for each metal layer

- Undegraded: A model for normal operation mode

- Degraded: A model of the line after 100,000 Hours of work under the Worst RV conditions

| Metal layer          | Rho         | t <sub>e</sub> | dlr          |

|----------------------|-------------|----------------|--------------|

|                      |             |                |              |

| Metal 6 over Metal 5 | 4.22000e-05 | 5.53000e-01    | -1.46800e-01 |

| Metal 4 over Metal 3 | 8.35000e-05 | 3.64000e-01    | -1.03000e-01 |

| Metal 2 over Metal 1 | 1.08200e-04 | 2.92000e-01    | -6.48000e-02 |

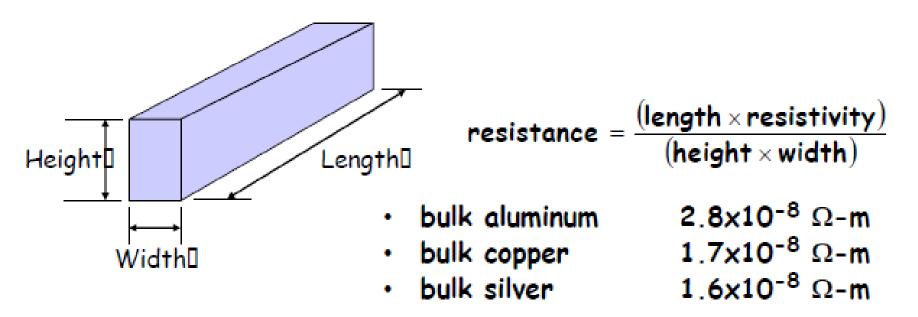

### Wire Resistance

- Height (Thickness) fixed in given manufacturing process

- Resistances quoted as  $\Omega$ /square

- TSMC 0.18μm 6 Aluminum metal layers

- M1-5 0.08  $\Omega$ /square (0.5  $\mu$ m x 1mm wire = 160  $\Omega$ )

- M6 0.03  $\Omega$ /square (0.5  $\mu$ m x 1mm wire = 60  $\Omega$ )

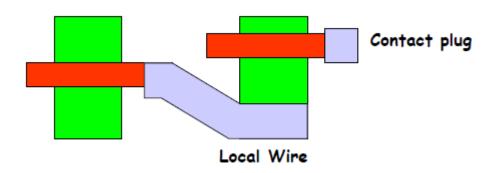

#### **Local Interconnect**

- Use contact material (tungsten) to provide extra layer of connectivity below metal 1

- Can also play same trick with silicided poly to connect gates to diffusion directly in RAMs

- Typically used to shrink memory cells or standard cells

- Contacts directly to poly gate or diffusion

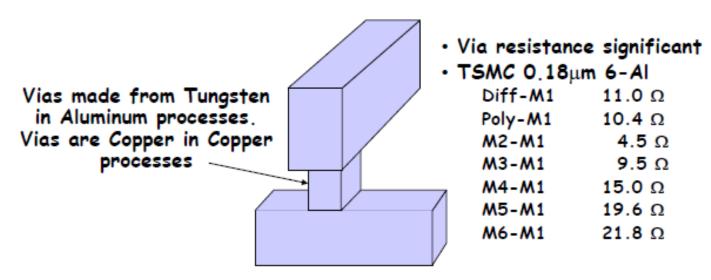

#### Via Resistance

- Resistance of two via stacks at each end of M1 wire equivalent to about 0.1 mm wire (~20  $\Omega$ )

- Resistance of two via stacks at each end of M6 wire about the same as 1 mm narrow M6 wire (~60  $\Omega$ )!!!

- Use multiple vias in parallel to reduce effective contact resistance

- Copper processes have lower via resistance

#### Via Resistance Model

te,res: Are process file parameters given for a specified Via model

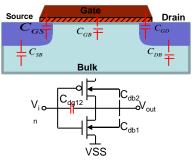

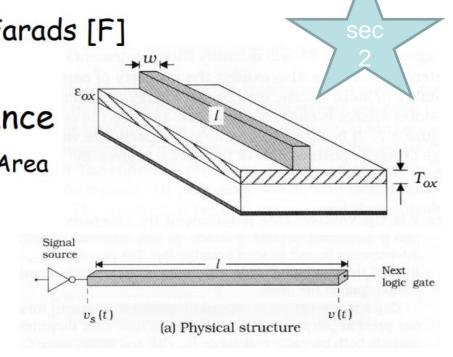

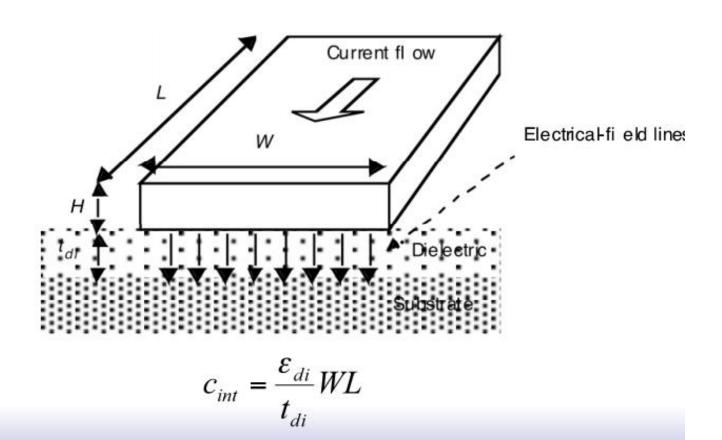

# Parasitic Line Capacitances

Capacitor Basics

- Q = CV, C in units of Farads [F]

- I = C aV/at

- Parallel plate capacitance

$$-C_{line} = \frac{\varepsilon_{ox} w / [F], w l = Area}{t_{ox}}$$

- $\varepsilon_{ox}$  = permittivity of oxide

- RC time constant of an interconnect line

$$-\tau = R_{line} C_{line}$$

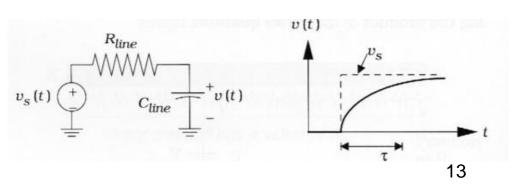

# Capacitance Scaling

parallel plate capacitance  $\infty \frac{\text{width}}{\text{spacing}} \times \text{length}$

- Capacitance/unit length ~constant with feature size scaling (width and spacing scale together)

- Isolated wire sees approx. 100 fF/mm

- With close neighbors about 160 fF/mm

- Need to use capacitance extractor to get accurate values

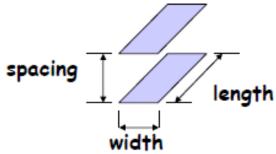

### Capacitance: The Parallel Plate Model

### **RC Delay Estimates**

#### Penfield-Rubenstein model estimates:

Delay =

$$\sum_{i} \left( \sum_{j=1}^{j=i} R_{j} \right) C_{i}$$

#### Capacitance

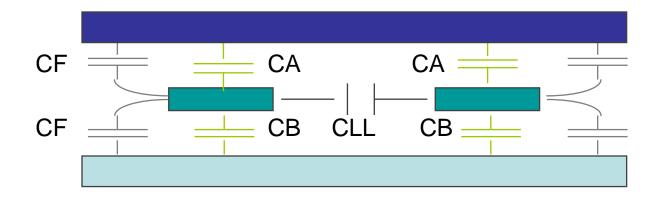

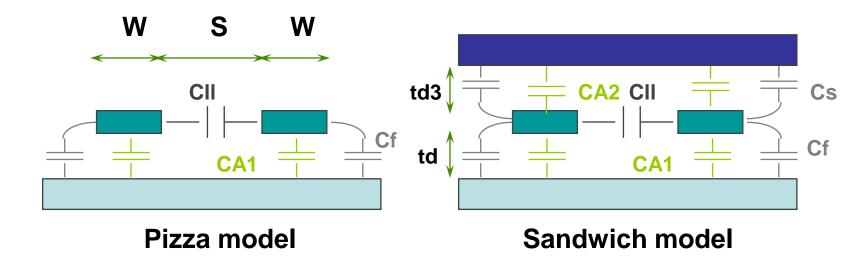

#### Interconnect Capacitance

CLL Line to Line Capacitance.

CA, CB Capacitance to Other Plane.

CF Fringing Capacitance.

#### Solving a speed path.

What happened to R?

What happened to C?

# Fringe Capacitance

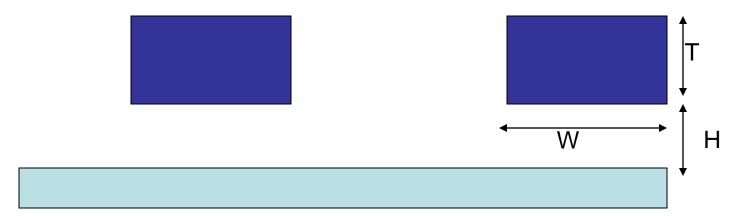

As the process dimensions get smaller, the interconnect ratio (T/W) and (T/H) increases, since T has to increase to get a better resistance. Therefore <u>Fringe</u> capacitance becomes more and more significant.

#### Line Capacitance Calculation

Ctotal = Ca1 + Ca2 + 2\*CII + 2\*Cf + 2\*Cs

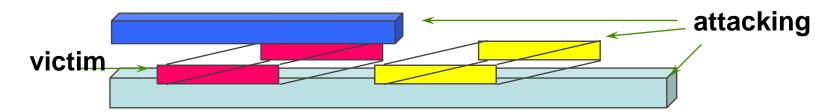

### Cross Capacitance

- Cross Capacitance is any capacitance between nets, which are non DC nets.

- In the worst case all the capacitance between nets can be cross capacitance.

- We call the signal that we are analyzing the victim, and all the signals that have cross capacitance to it we will call them attacking signals.

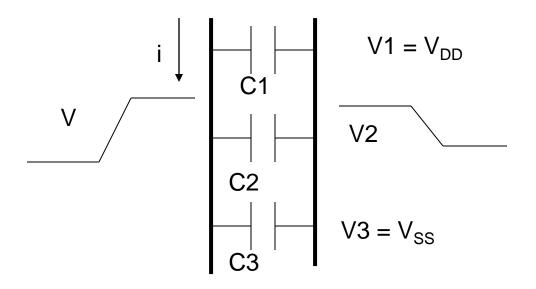

# Cross Capacitance & Miller Effect

- Remembering the current-voltage equation for a capacitor

i(t) = C \* dv(t)/dt

- In case that the attacking signal is also switching, then the dv(t)/dt is actually bigger or smaller than the DC case, depending on the switching directions of the victim and attacking signals.

- In verification tools we always calculate the voltage referenced to the Ground "Vss" which is a DC signal.

- We can see this effect as if the effective capacitance between the line and the Ground changes, this is called the Miller Effect.

- Miller Coefficient is the factor that we use to multiply the Xcap in order to model the Miller Effect.

## Miller Coupling Mathematics

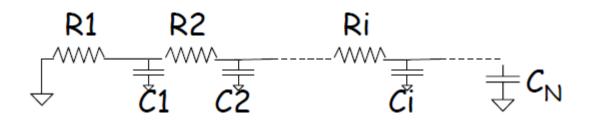

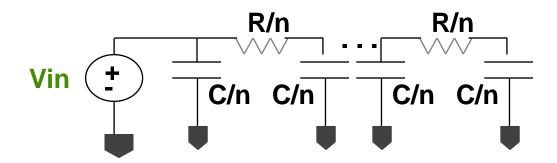

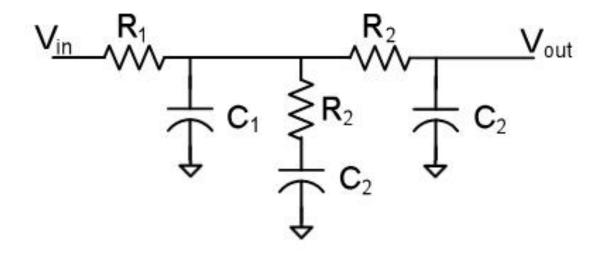

### Distributed Line Model

- The distributed line model is a more accurate model which assumes that the line is built out of many segments, when each segment is modeled as a lumped RC model.

- For calculating the RC delay using the distributed model a simulation is needed

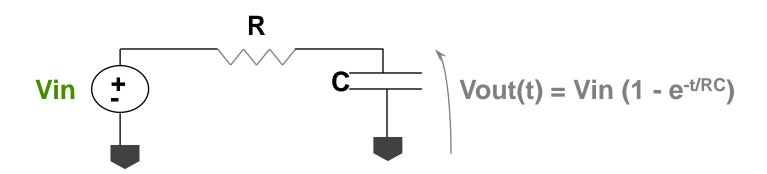

### Lumped Line Model

- A lumped model is a pessimistic one, which assumes that all the capacitance, line and load, is located at the end of the line, in other words that the driver "sees" the total load through the total line resistance.

- As the RC delay increases the lumped RC model is less and less accurate.

#### Impact of Interconnect Parasitics

#### **Classes of Parasitics**

- Capacitive

- Resistive

- Inductive

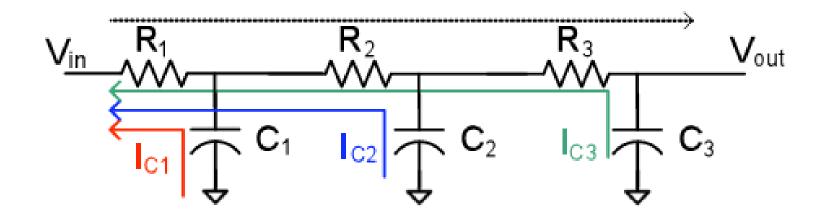

# Simplified Model: Elmore Delay

$$\tau_{Elmore} = R_1 C_1 + (R_1 + R_2) C_2 + (R_1 + R_2 + R_3) C_3$$

### Wire Delay Example

- In 0.18μm TSMC, 5x minimum inverter with effective resistance of 3 kΩ, driving FO4 load (25fF)

- Delay = Rdriver x Cload = 75 ps

- Now add 1mm M1 wire, 0.25µm wide

- Rw = 320 $\Omega$  wire + 22 $\Omega$  vias = 344 $\Omega$

- Cw = 160fF

$$\begin{split} \text{Delay} &= \text{Rdriver} \times \frac{\textit{Cw}}{2} + \left( \text{Rdriver} + \text{Rw} \right) \times \left( \frac{\textit{Cw}}{2} + \textit{Cload} \right) \\ &= 3k\Omega \times 80 fF + \left( 3k\Omega + 344\Omega \right) \times \left( 80 fF + 25 fF \right) \\ &= 591 ps \end{split}$$

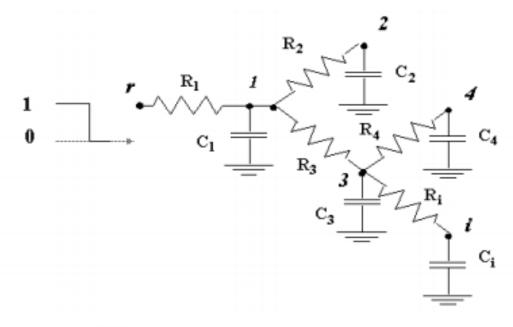

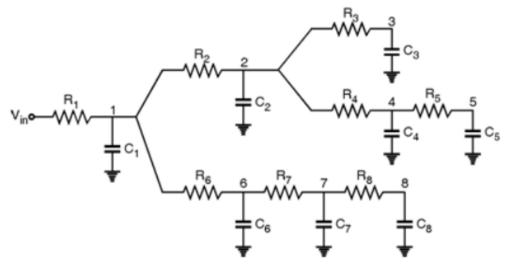

# Elmore Delay - Extended

$$R_{ik} = \sum R_j \Rightarrow (R_j \in [path(s \rightarrow i) \cap path(s \rightarrow k)])$$

$$\tau_{Di} = \sum_{k=1}^{N} C_k R_{ik}$$

# Another Elmore Delay Example

$$au_{Elmore} =$$

Consider RC network shown in Figure below connected in the form of RC segments.

RC tree network

Now, here the Elmore delay at node 7 is calculated as,

$$\square D7 = R1 C1 + R1 C2 + R1 C3 + R1 C4 + R1 C5 + (R1 + R6) C6 + (R1 + R6 + R7) C7 + (R1 + R6 + R7) C8$$

In the same manner, the Elmore delay at node 5 is calculated as,

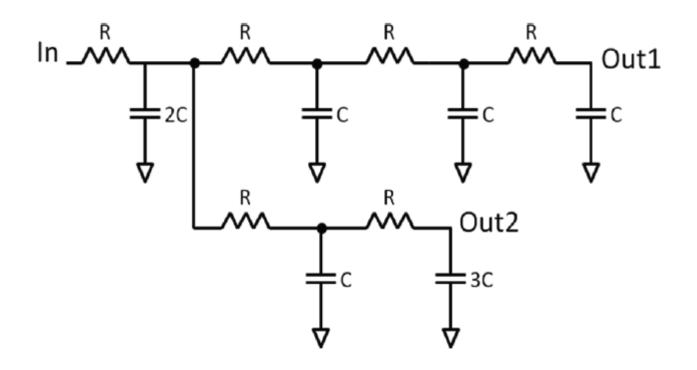

#### Calculate Elmore delay from In to out1 and from In to out2?

Solution:

Elmore to out1 is 15RC

Elmore to out2 is 16RC

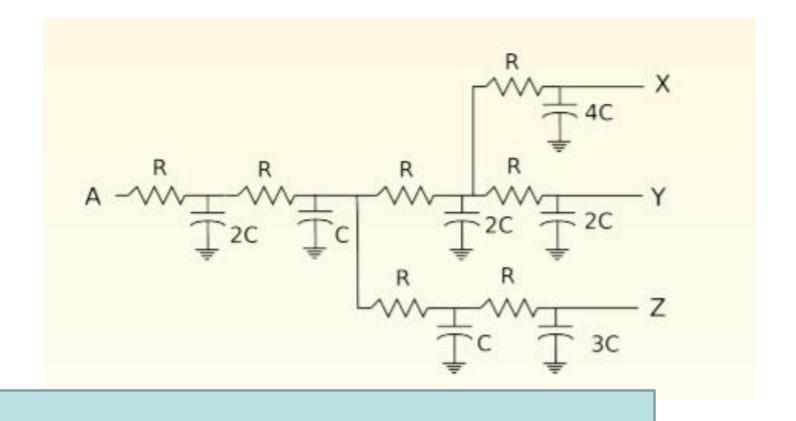

#### Delay from A to Y

33

Uploaded By: anonymous

### Resistance, Capacitance & Inductance

#### RESISTOR

$$V(t) = R *i(t)$$

,  $R = V / I = V / A = \Omega$

$$P(t) = I^{2}R = V^{2}/R$$

,  $W(t0,t1) = R \int_{t0}^{t} I^{2} dt = \frac{1}{R} \int_{t0}^{t} V^{2} dt$

#### **CAPACITOR**

$$Q(t)=CV$$

,  $C=Q/V=A*Sec/V=FARAD$

$$I(t) = \partial Q / \partial t = \partial (CV(t)) / \partial t = C\partial V / \partial t$$

$$V(t) = V(t0) + 1/c * \int_{t0}^{t} I(t) \partial t \quad P(t) = CV(t) \partial V / \partial t$$

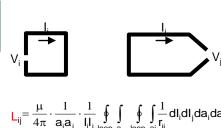

#### **INDUCTOR**

$$\Phi(t) = L * I(t)$$

,  $L = \Phi / I = webber / A = V * Sec / A = Henry$

$$V(t) = \partial \Phi / \partial t = \partial (LI) / \partial t = L * \partial I / \partial t$$

$$I(t) = I(t0) + \frac{1}{L} \int_{t0}^{t} V(t) \partial t$$

,  $P(t) = L *I*\partial I / \partial t$