# Computer Organization And Microprocessors ENCS2380

# **Mohammed Saada**

STUDENTS-HUB.com

Uploaded By: anonymous

Performance

Performance = Excution time

Cpu Excution time = cpu cycles x cyck time = cpu cycles Clock rafe clock cycle = clock period clock rate = clock frequency = \_\_\_\_\_\_\_\_ CPI = Lotal Number of Cycles Eotal Number of instructions CPI: Average cycles per instruction CPU Cycles = CPI x instructions Count CPU Excution time = CPI x inst. Count x sycle time

MIPS : Millions instructions per Second.

MIPS = Instructions Count = clockrate Excution time x 10<sup>6</sup> CPIX 10<sup>6</sup>

Excution time = Inst. Count = Inst. Count x CPI MIPS X 10<sup>6</sup> Clock note

O Doesn't take into account the capability of instructions (e.g. Instructions count) @ MIPS Varies between programs on the same computer. (3) MIPS Can Vary inversely with performance (e.g. a higher MIPS rating does not always mean better performance)

Chapter 10: Instruction Set Architecture (ISA) Instruction Format, like: Destination Source 1 Source 2 Opcode

3

⇒ µumber of addresses (operands) :

$\bigcirc$ 4 - addresses : operand 1, operand 2. Result, next instruction - very long instruction - not Common.

(2) 3-addresses : operand 1, operand 2. Result. ADD A, B, C ; A = B+C

3 2-addresses: operand 1 and Result are same, operand 2. - ADD A,B ; A=A+B - Reduce the length of instruction. - Some extra work (to hold some results if needed)

(4) 1- address implicit second address (accumulator) - ADD B ; AC = AC+B - Common on early machine.

(5) 0-address -using Stack. - the operands are the top two elements in the Stack, and the Result stored in the stack. STUDENTS-HUB.com

Uploaded By: anonymous

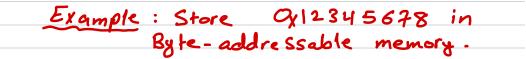

⇒ Byte Order:

D Little - Endian : The least significant Byte in the lowest address.

Big \_ Endian : The most significant Byte in the lowest address. Q

| ٥ | 0,78         | 0 | Ox 12 |  |

|---|--------------|---|-------|--|

| 1 | 0x 56        | 1 | 0r 34 |  |

| 2 | 0x34<br>0x12 | 2 | 0256  |  |

| 3 | 0x12         | 3 | 0778  |  |

| Ч |              | 4 |       |  |

Little Endian Big Endian

Chapter 11: Addressing Mode

1) Immediate (Constant) - operand = Address field. - No need to access memory or Registers - Fast - Limited - Leads to poor programming practice Direct Addressing (Direct memory) - Effective address (EA) = address field - himited address space ADD A, [5] (3) Indirect Addressing (Indirect memory) - Effective address (EA) = the content of the memory cell which addressed in the instruction ADD A. [5] - Large address space. - Very Slow. (4) Register Addressing (Direct) - Effective address (EA) = R Limited number of Registers very small address field needed ; \* shorter instructions # Faster Petch. No memory access. very fast excution. STUDENTS-HUB.com Uploaded By: anonymous

(5) Register Indirect Addressing \_ Effective address (EA) = the content of the Register. operand in memory, it's address in the Register. - Large address space (2") n: Register width. - one fewer memory access than indirect addressing (memory indirect) (6) Displacement (indexed) Addressing -EA = A + (R)A: base Value R: Register that holds displacement or vice versa. EA = A+(PC) PC Relative (7) Stack Addressing - operand is implicitly on top of Stack.

# Chapter 3: CPU Organization

> The major components of CPU:

Register set (Register File)

Arithmetic and Logic Unit (ALU)

Control Unit (CU)

→ Special purpose Registers in CPU:

PC: Program Counter. IR: Instruction Register. MAR: Memory address Register. MBR/MDR: Memory buffer(data) Register. INAR: Input/output address Register I/OBR: Input/output buffer Register.

\* RTL Statements (Register Transper Language) Micro-operation:

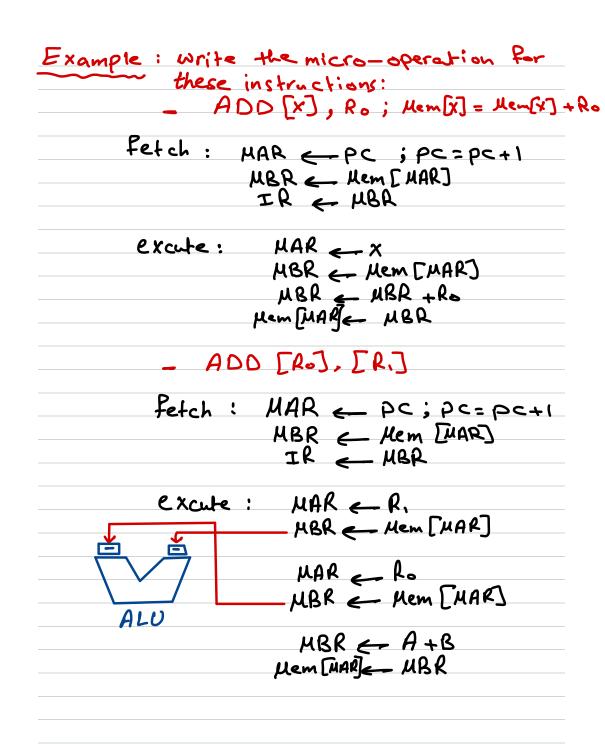

-> Fetch instruction : MAR \_ PC; PC=PC+1 HBR - Mem [MAR] IR - MBR > excute the instruction (ADD R2, R1, Ro) the same steps for fetch. excute :  $R_2 \leftarrow R_1 + R_0$

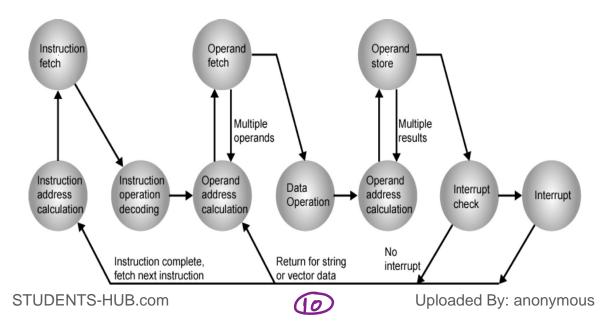

→ Interrupts : Mechanism by Which other modules (e.g. I/O) my interrupt normal sequence of processing. Improves process efficiency Classes of interrupts:

\_ program : Arithmetic over flow, division by zero

- Timer : Generated by internal processor timer used in pre-emptive multi-tasking - I/O (from I/O controller): to signal normal Completion or error Hardware failure : memory parity error, Dower failure.

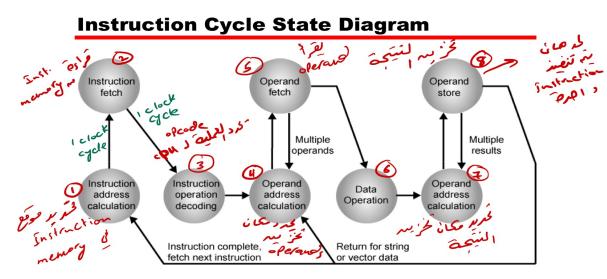

## Instruction Cycle (with Interrupts) -State Diagram

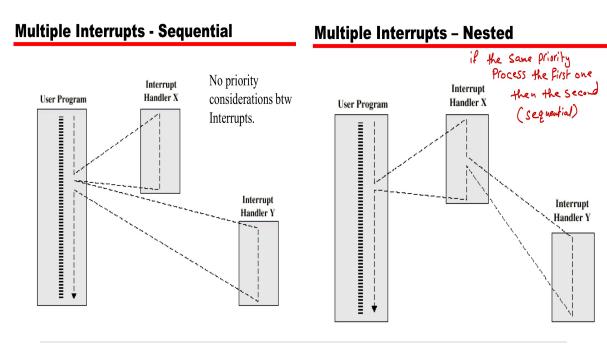

#### **Multiple Interrupts**

- Disable interrupts

- Processor will ignore further interrupts whilst processing one interrupt

- Interrupts remain pending and are checked after first interrupt has been processed

- -Interrupts handled in sequence as they occur Queue (First in - First ont)

- Define priorities

- —Low priority interrupts can be interrupted by higher priority interrupts

- -When higher priority interrupt has been processed, processor returns to previous interrupt

Uploaded By: anonymous

| ⇒ Bus Types:                                     |

|--------------------------------------------------|

| Dedicated : separate data 8 address              |

| (ines,<br>1) Hultiplexed: - Shared lines.        |

| Address Valid or data<br>Valid Control line.     |

| - advantage : Fewer lines.<br>- disadvantage :   |

| - Nore complex control<br>- Ultimate performance |

| ⇒ CPU Local (internal) Bus Organization:         |

| One-Bus Organization                             |

CPU registers and ALU, use single Bus to move outgoing and incoming data.

Single data movement withen one clock cycle.

Additional registers may be needed to buffer data for the ALU.

Simplest and least expensive.

Limits the amount of data transfer that Can be done in the Same clock cycle.

Slow down the overall performance.

Two-Bus Organization - two different Data (operands) can transfered at the Same clock cycle. - an additional buffer register may be needed to hold the output of the ALU when the STUDENTS-HUB.tomo buses are busy (carrying the apperands)

-or, one of the buses may be dedicated for moving data into registers (in-bas), While the other is dedicated for transfering data out of the register (out-bus) Three-Bus Organization - Two buses used as source buses, while the third is used as destination. - Source buses move data out of the registers (out-bus) - destination bus move data into a register (in-bus) - each of the two out-buses is connected to an ALU input. - The output of the ALU is connected directly to the in-bus.

\* More buses -> More data can be moved withen a single clock cycle.

\* More buses \_> More complexity in hardware.

→ Bus Arbitration \_ More than one module controlling the bus (e.g. CPU, Direct Memory Access DMA) \_ Arbitration Can be: Centralized: only one module may control bus at one time. Distributed: More than one module controlling the STUDENTS-HUB.com(e.g. CPU and DMA controller) (3)

## **Control Unit**

- The control unit is the main component that directs the system operations by sending control signals to the datapath.

- **Datapath:** The data section, which contains the registers and the ALU.

- These signals control the flow of data within the CPU and between the CPU and external units such as memory and I/O.

- Control buses generally carry signals between the control unit and other computer components in a clock-driven manner.

- The system clock produces a continuous sequence of pulses (timing signals) in a specified duration and frequency.

#### **Control Unit**

- A sequence of steps t0 , t1 , t2 , . . . , (t0 < t1 < t2 , . . .) are used to execute a certain instruction.</li>

- The op-code field of a fetched instruction is decoded to provide the control signal generator with information about the instruction to be executed.

- Step information generated by a **logic circuit module** is used with other inputs to generate control signals.

- The signal generator can be specified simply by a set of Boolean equations for its output in terms

- There are mainly two different types of control units:

- Microprogrammed

- The control signals associated with operations are stored in special memory units inaccessible by the programmer as control words.

- Hardwired

- Fixed logic circuits that correspond directly to the Boolean expressions are used to generate the control signals.

# **Hardwired Implementation**

- In hardwired control, a direct implementation is accomplished using logic circuits.

- For each control line, one must find the Boolean expression in terms of the input to the control signal generator

#### **Microprogrammed Control Unit**

- Microprogramming was motivated by the desire to **reduce the complexities** involved with hardwired control.

- An instruction is implemented using a set of microoperations.

- Associated with each **micro-operation** is a **set of control lines** that must be **activated** to carry out the corresponding microoperation.

- The idea of microprogrammed control is to **store** the **control signals** associated with the implementation of a certain instruction as a microprogram in a **special memory** called a control memory (CM).

- A microprogram consists of a sequence of microinstructions.

- A microinstruction is a vector of bits, where each bit is a control signal, condition code, or the address of the next microinstruction.

- —Microinstructions are fetched from CM the same way program instructions are fetched from main memory

- When an instruction is fetched from memory, the **opcode** field of the instruction will **determine which microprogram** is to be executed.

Chapter 10: Computer Arithmetic

⇒ Signed Integers: 1) Signed Magnitude Range :  $-(2^{n-1}) \rightarrow +(2^{n-1}-1)$ two representations of zero (+0, -9) 2 Biased Bias = 2\_1 Range :  $-Bias \rightarrow + (Bias + i)$ Binary to Decimal : Binary Value - Bias. Decimal to Binary; Decimal + Bias then convert to Binary. 1'S Complement (3) Range:  $(2^{n-1}) \longrightarrow (2^{n-1})$ two representations of Zero (e.g. +0, -0) 2's complement Range:  $-2^{n-1} \rightarrow +(2^{n-1})$

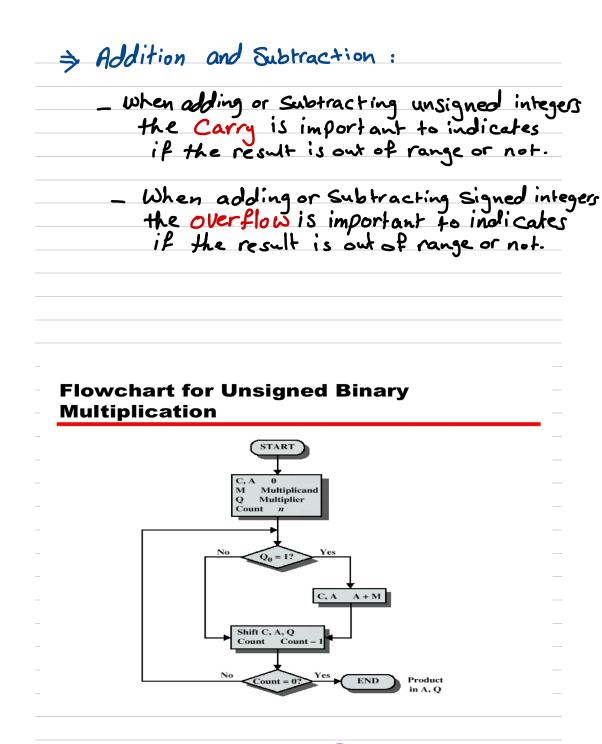

### **Execution of Example**

| C<br>0 | A<br>0000 | Q<br>1101 | M<br>1011 | Initial | Values          |

|--------|-----------|-----------|-----------|---------|-----------------|

| 0      | 1011      | 1101      | 1011      | Add     | First           |

| 0      | 0101      | 1110      | 1011      | Shift } | Cycle           |

| 0      | 0010      | 1111      | 1011      | Shift } | Second<br>Cycle |

| 0      | 1101      | 1111      | 1011      | Add }   | Third           |

| 0      | 0110      | 1111      | 1011      |         | Cycle           |

| 1      | 0001      | 1111      | 1011      | Add }   | Fourth          |

| 0      | 1000      | 1111      | 1011      |         | Cycle           |

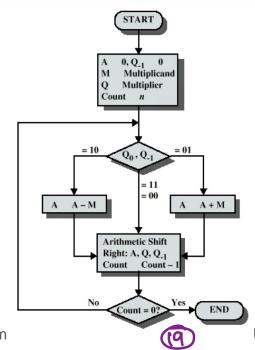

#### **Booth's Algorithm**

Uploaded By: anonymous

#### **Example of Booth's Algorithm**

| A<br>0000    | Q<br>0011    | Q <sub>-1</sub><br>0 | M<br>0111    | Initial Valu     | es              |

|--------------|--------------|----------------------|--------------|------------------|-----------------|

| 1001<br>1100 | 0011<br>1001 | 0<br>1               | 0111<br>0111 | A A-M<br>Shift   | First<br>Cycle  |

| 1110         | 0100         | 1                    | 0111         | shift }          | Second<br>Cycle |

| 0101<br>0010 | 0100<br>1010 | 1<br>0               | 0111<br>0111 | A A + M<br>Shift | Third<br>Cycle  |

| 0001         | 0101         | 0                    | 0111         | shift }          | Fourth<br>Cycle |

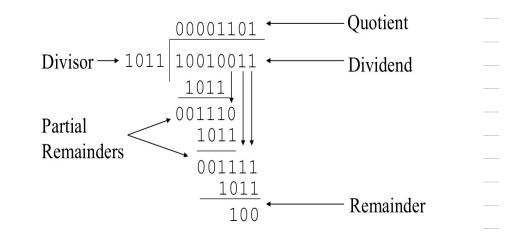

#### **Division of Unsigned Binary Integers**

STUDENTS-HUB.com

Uploaded By: anonymous

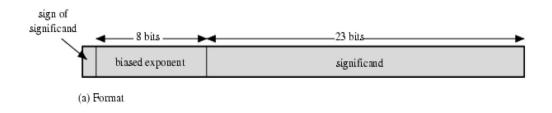

#### **Floating Point Examples**

#### **Converting <u>from</u> Floating Point**

E.g., What decimal value is represented by the following 32-bit floating point number?

C17B0000<sub>16</sub>

#### **Converting to Floating Point**

E.g., Express 36.5625<sub>10</sub> as a 32-bit floating point number (in hexadecimal)