## ANSWER BOOKLET

| Student: | Digital     | Number      | 13   |

|----------|-------------|-------------|------|

| Course:  | Department: | Number:     |      |

|          | Division:   | Instructor: |      |

| Date:    | Day         | Month       | Year |

## For Instructor's Use

| FOR Instructor's Use |       |  |  |

|----------------------|-------|--|--|

| Question             | Grade |  |  |

| 1                    |       |  |  |

| 2                    |       |  |  |

| 3                    |       |  |  |

| 4                    |       |  |  |

| 5                    |       |  |  |

| 6                    |       |  |  |

| 7                    |       |  |  |

| 8                    |       |  |  |

| 9                    |       |  |  |

| 10                   |       |  |  |

| 11                   |       |  |  |

| 12                   |       |  |  |

| Total                |       |  |  |

|                      | -     |  |  |

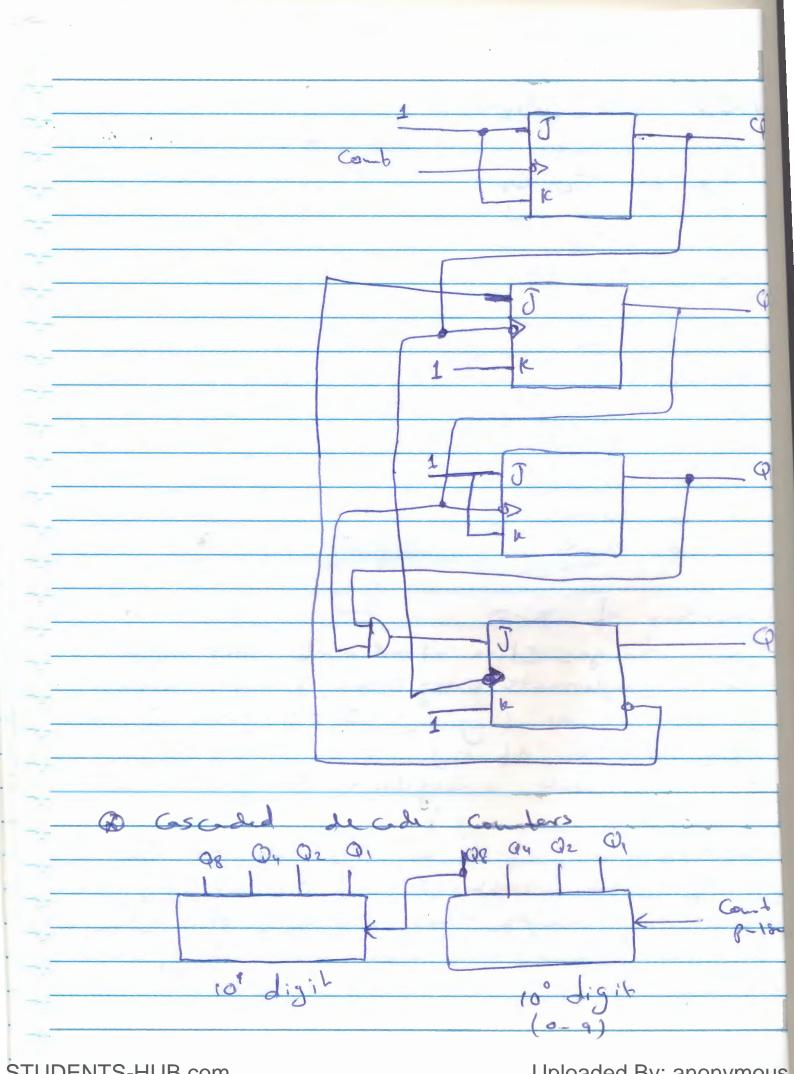

- All unused states for minterm 10 to 15 102 = Og Q1 080, + Q4 O2 Q1 = 08 0, @ Binary Counter with perallel - This Counter good of we was

- @ Counter with unused state.

- unused states may be treated as don't - or may be assigned specific next in this example we assign force the invested states to go to a specific state in order to word lock case for some failurge goes to unused State, and for some design (not all of them) the unused state will go to another unused state, and so on (11) or (11) gent an Uploaded By: anonymous STUDENTS-HUB.GOM 🗴

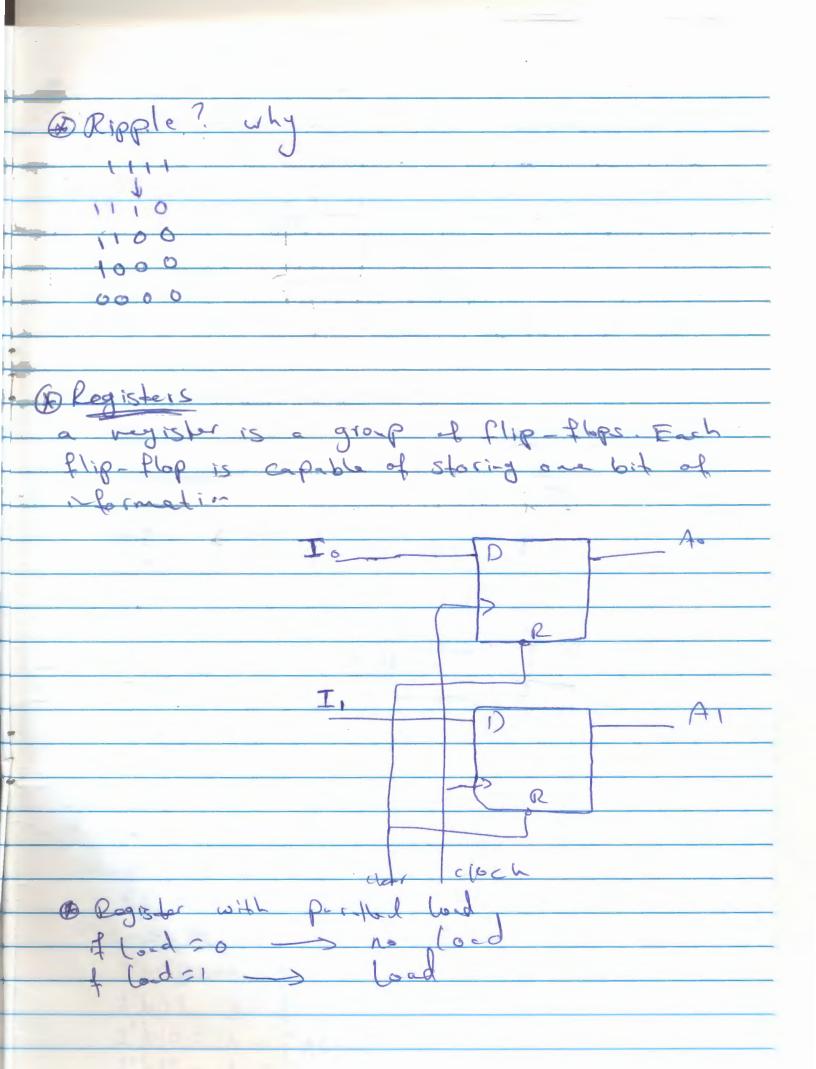

@ Ripple Counters The flip-flop output transition serves as a source for triggering other flip-flops.

(i.e. the CIK input of some flip-flops to are not triggered by the common clock). @ Binary Ripple conter Ex. Design a 3-bit birary ripple com-Ao (LSB) Az (MSB) STUDENTS-HUB.com Uploaded By: anonymous @ Design a 3-bit Counter Reset the edge triggered (sam as previous Of it we adje trijgend is aded I connect the complement to trigger the next FF

@ BCD Ripple Counter - we need 4 bits (4 flip-flops) Behaviour of BCD Q, changes State after each - Q2 complements cevery sime Q, remains 0 as long as On or Oy is O. when both Or and Oy become I Q8 Complements when Q, goes from

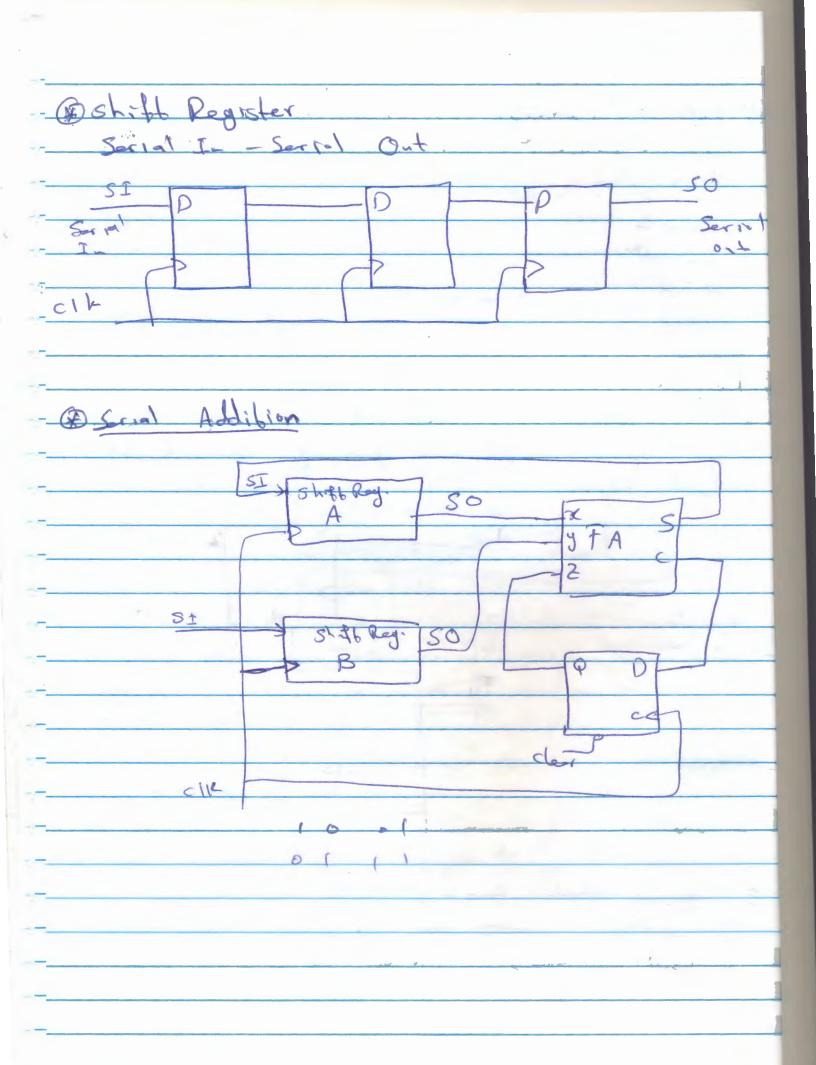

@Universal Shift Register universal: functional complete to (the function is controlled via some control impats) In Corneral, a universal shift negister an Shif date right, left, and has a parallel load capabilities Example 4-bit universal shift negister 5,50=00 => The present value of the negister is applied to the Disputs of the Plip-Plops. 3 5,50 =00 No charge 5,50=01 => Shift right with Serial input 5,50=10 => Shift leth !! "," SiSo = 11 -> Parallel locd. @ Behavioral Description of Universal Shift Reg. module universal (SI, So, I, A, left, right, clk, clr); input Si, So, left, right, cik, cir, oupput [3:0]A; ry [3:03 A) always @ (posedge CLK or negedge dr) 17 (cir == 0) A = 4 60000; Case ( (5,50}) 2600: A - A 2'bol: Ac fright, A[3:1]} 2 610: A = f A(2,03, left }; STUDENTS-HUB.com 7 Uploaded By: anonymous