Threshold voltage in CMOS Defined as: The Threshold voltage, VT for a MOS transistor can be defined as the voltage applied between the gate and the source of the MOS transistor below which the drain to source current, IDS effectively drops to zero.

| Threshold voltage in CMOS Defined as: The Threshold voltage, VT MOS transistor can be defined as the voltage applied between the and the source of the MOS transistor below which the drain to so current, IDS effectively drops to zero. | he gate |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| ● True                                                                                                                                                                                                                                    |         |

| O False                                                                                                                                                                                                                                   |         |

|                                                                                                                                                                                                                                           |         |

\_\_\_\_\_

• Fringe Capacitance for wire becomes less important as process goes low

\_\_\_\_\_\_

• The minimum width and minimum spacing provided by:

The minimum width and minimum spacing provided by:

A. process file

B. Layout Engineer

C. only by design owner

D. Logic designer

| •    | What are the operation regions for a MOS transistor?                                                          |

|------|---------------------------------------------------------------------------------------------------------------|

|      | What are the operation regions foe a MOS transistor?                                                          |

|      | A. Cutoff region                                                                                              |

|      | B. Linear region                                                                                              |

|      | □ C. None                                                                                                     |

|      | D. Saturation Region                                                                                          |

|      | ☐ E. MOS device has only one region only                                                                      |

| ===  | =======================================                                                                       |

| •    | Choose the option below that is regarded as a step in the process of preparing various Silicon wafers process |

|      | Choose the option below that is regarded as a step in the process of preparing various Silicon wafers process |

|      | A. Etching and Wafer cleaning.                                                                                |

|      | □ B. Verilog code preparation                                                                                 |

|      | ☑ C. Crystal growth & doping                                                                                  |

|      | D. Wafer polishing                                                                                            |

| ===  |                                                                                                               |

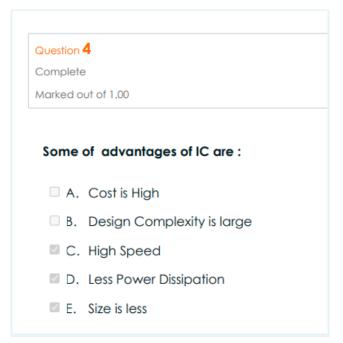

| Som  | e of advantages of IC are :                                                                                   |

|      | Some of advantages of IC are :                                                                                |

|      | ☐ A. Design Complexity is large                                                                               |

|      | ☐ B. Cost is High                                                                                             |

|      | C. Size is less                                                                                               |

|      | D. Less Power Dissipation                                                                                     |

|      | E. High Speed                                                                                                 |

| ===: |                                                                                                               |

STUDENTS-HUB.com

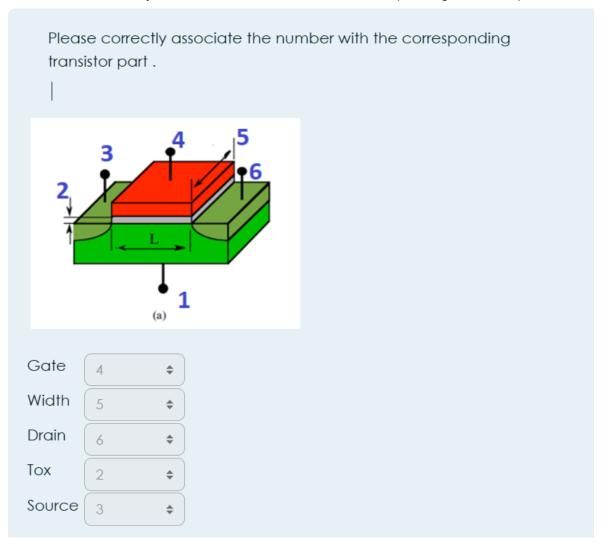

Please correctly associate the number with the corresponding transistor part.

• ----- connects between 2 segments of metal layers

For constraints, the clock period has to be \_\_\_\_\_ than the data path delay

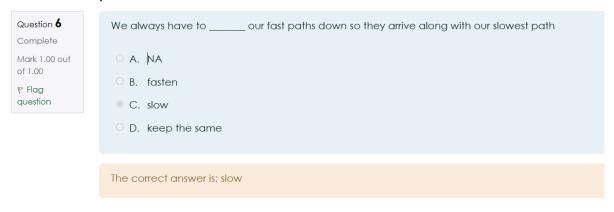

We always have to \_\_\_\_\_ our fast paths down so they arrive along with our slowest path

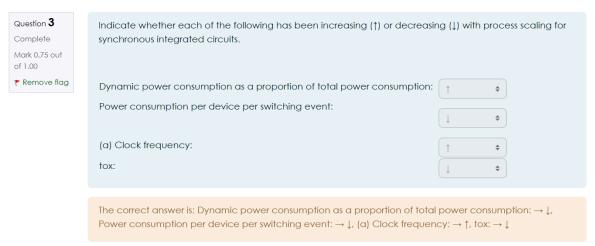

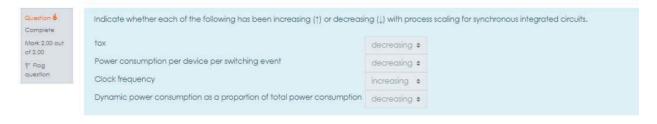

Indicate whether each of the following has been increasing (↑) or decreasing (↓) with process scaling for synchronous integrated circuits.

\_\_\_\_\_\_\_

• Dynamic power consumption as a proportion of total power consumption:

\_\_\_\_\_\_\_\_

Which of these is considered a process for IC fabrication?

\_\_\_\_\_\_\_

• Temperature does not affect RC of the wire ?

\_\_\_\_\_\_

• If we could make all paths have equal delays, we wouldn't need sequential logic

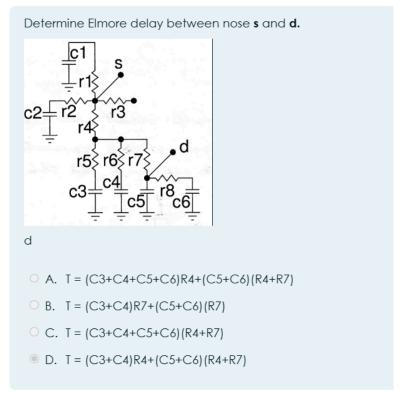

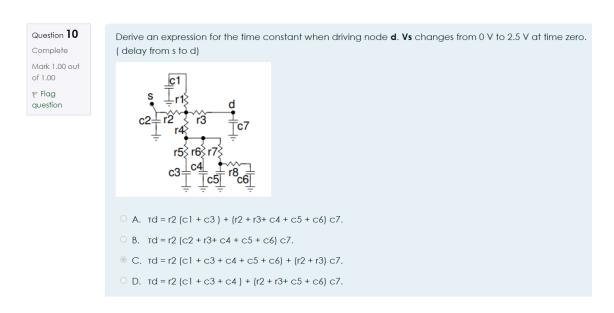

Determine Elmore delay between nose s and d.

\_\_\_\_\_

• ----- The data path is so short that it passes through several registers during the same clock cycle.

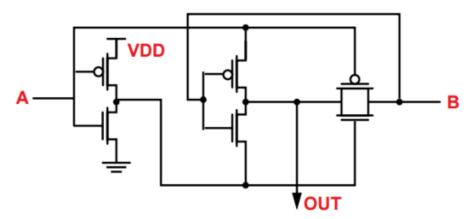

what function this circuit represent

\_\_\_\_\_

• \_\_\_\_\_ occur due to the logic changing before thold has passed.

This is not a function of cycle time – it is relative to a single clock edge

• ----- The data path is so short that it passes through several registers during the same clock cycle.

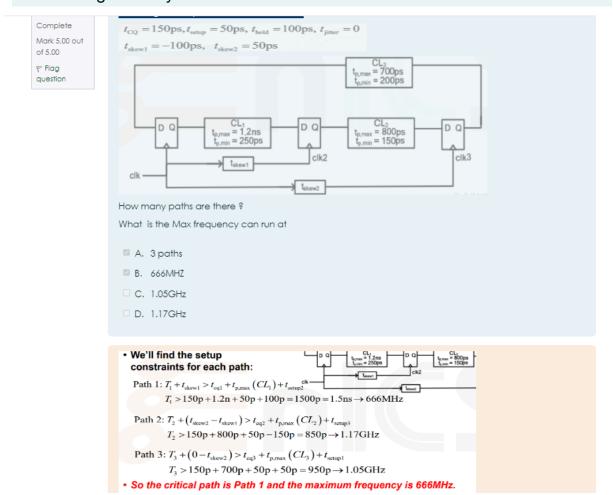

### We are given a synchronous network with:

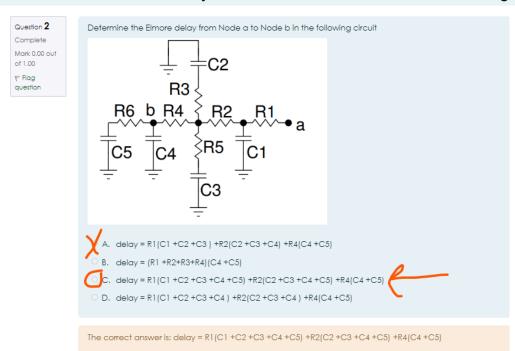

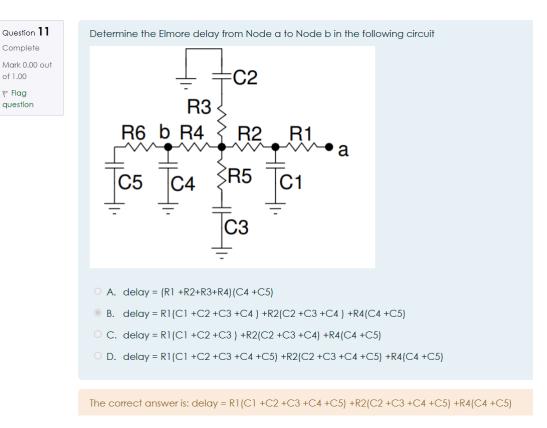

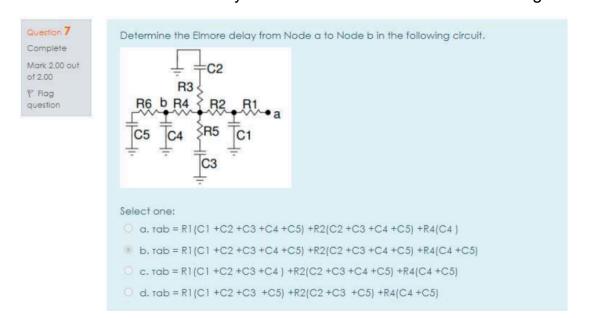

# Determine the Elmore delay from Node a to Node b in the following circuit

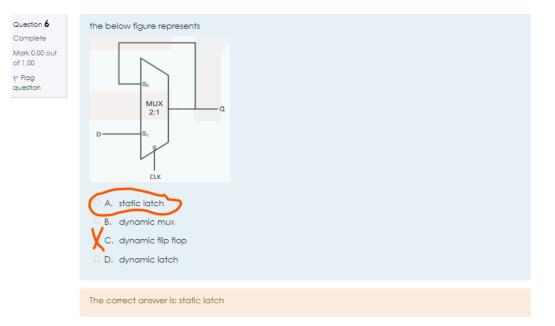

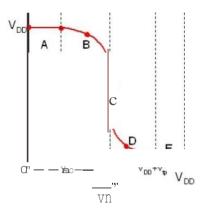

## • the below figure represents

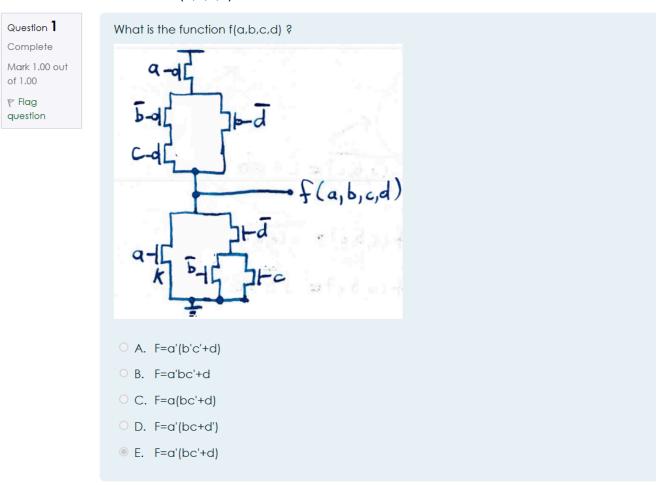

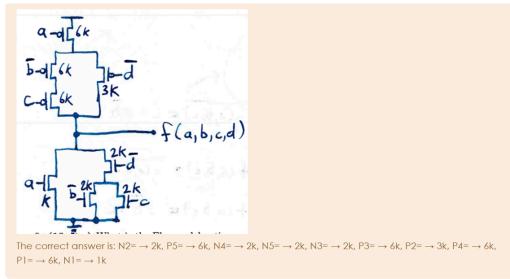

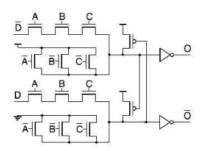

#### What is the function f(a,b,c,d)?

Threshold voltage increases for narrow NMOSFETs.

\_\_\_\_\_

• Threshold voltage decreases for very short NMOSFETs

\_\_\_\_\_

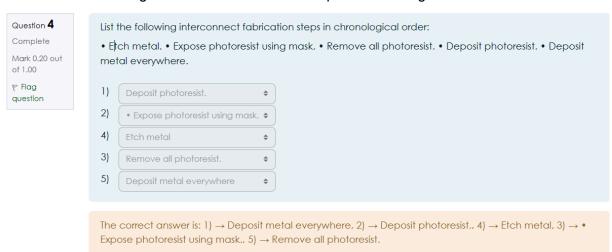

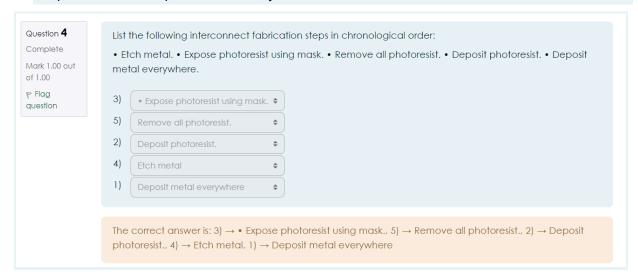

List the following interconnect fabrication steps in chronological order:

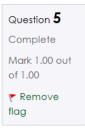

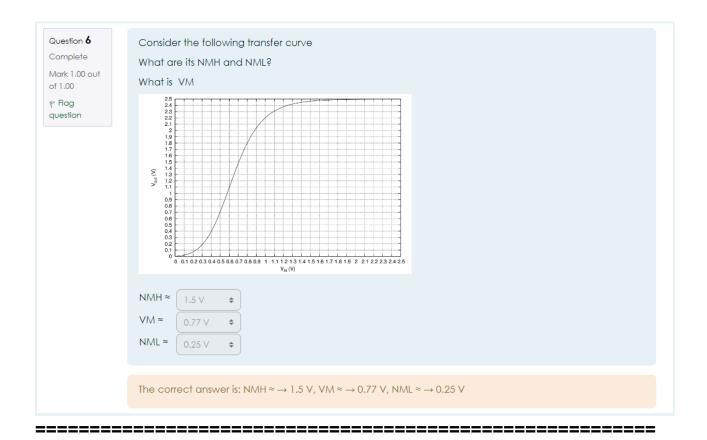

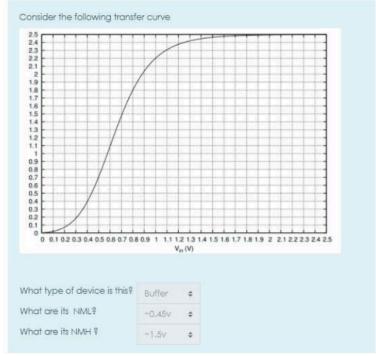

- Consider the following transfer curve

- What are its NMH and NML?

- What is VM

\_\_\_\_\_\_

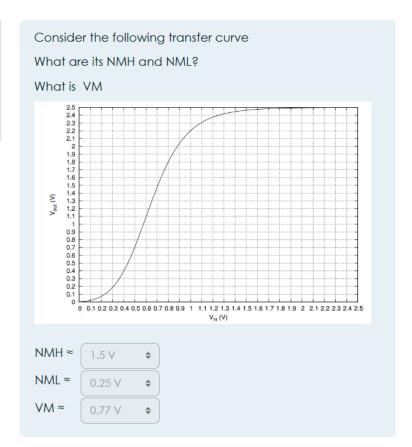

Report /Estimate NML and NMH for this technology. Consider the transfer function shown in the following figure.

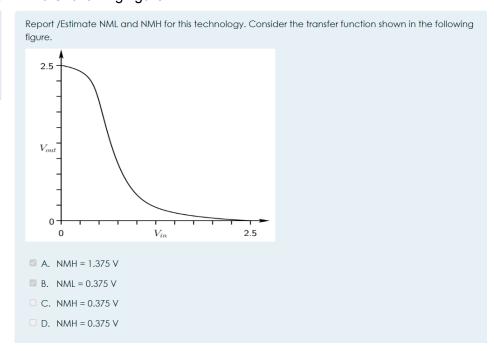

Match each transistor size based on an invertor of 1k for NMOS and 2k for PMOS

Question 7

Complete

Mark 0.20 out

of 1.00

P Flag

question

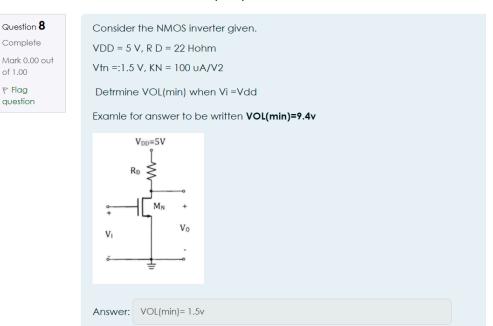

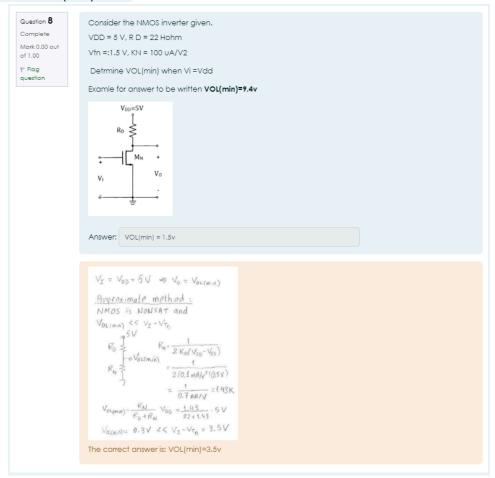

- Consider the NMOS inverter given.

- VDD = 5 V, R D = 22 Hohm

- Vtn =:1.5 V, KN = 100 uA/V2

- Detrmine VOL(min) when Vi =Vdd

- Examle for answer to be written VOL(min)=9.4v

$$V_{I} = V_{DD} = 5 \text{ V} \Rightarrow V_{O} = V_{OL(m,n)}$$

$$\frac{Approximate \ method:}{NMOS \ is \ NONSAT \ and}$$

$$V_{OL(m,n)} << V_{I} - V_{T_{I}}$$

$$V_{OL(m,n)} << V_{I} - V_{T_{I}}$$

$$= \frac{1}{2(0.1 \text{ mA/V}^{2})(3.5 \text{ V})}$$

$$= \frac{1}{0.7 \text{ mA/V}} = 1.43 \text{ K}$$

$$V_{OL(m,n)} = \frac{R_{N}}{R_{D} + R_{N}} V_{DD} = \frac{1.43}{22 + 1.43} \cdot 5 \text{ V}$$

$$V_{OL(m,n)} = 0.3 \text{ V} << V_{I} - V_{T_{I}} = 3.5 \text{ V}$$

The correct answer is: VOL(min)=3.5 v

\_\_\_\_\_\_\_\_\_\_\_

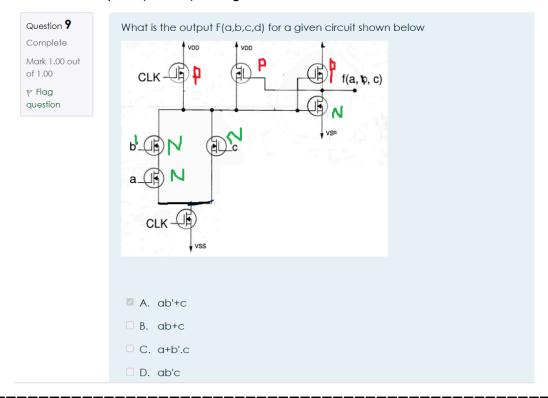

• What is the output F(a,b,c,d) for a given circuit shown below

Derive an expression for the time constant when driving node d. Vs changes from 0 V to 2.5 V at time zero. (delay from s to d)

STUDENTS-HUB.com

Determine the Elmore delay from Node a to Node b in the following circuit

•

\_\_\_\_\_\_

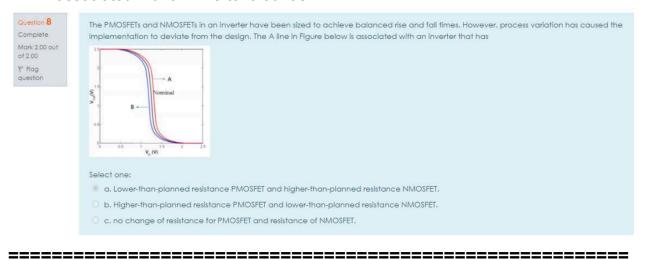

The PMOSFETs and NMOSFETs in an inverter have been sized to achieve balanced rise and fall times by making the NMOS larger than the PMOS.

- List the following interconnect fabrication steps in chronological order:

- Etch metal. Expose photoresist using mask. Remove all photoresist. Deposit photoresist. • Deposit metal everywhere

- Consider the following transfer curve

- What are its NMH and NML?

- What is VM

STUDENTS-HUB.com

- Consider the NMOS inverter given.

- VDD = 5 V, R D = 22 Hohm

- Vtn =:1.5 V, KN = 100 uA/V2 Detrmine VOL(min) when Vi =VddExamle for answer to be written VOL(min)=9.4v

holes generally travel more slowly than electrons in IC semiconductors.

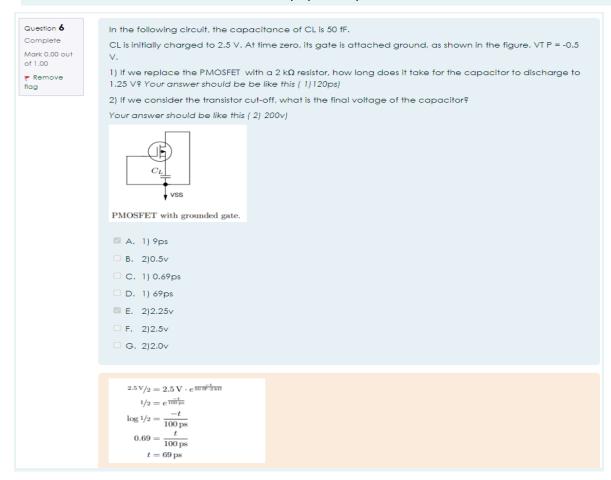

- In the following circuit, the capacitance of CL is 50 fF.

- CL is initially charged to 2.5 V. At time zero, its gate is attached ground, as shown in the figure. VT P = -0.5 V.

- 1) If we replace the PMOSFET with a 2 kΩ resistor, how long does it take for the capacitor to discharge to 1.25 V? Your answer should be be like this (1)120ps)

- 2) If we consider the transistor cut-off, what is the final voltage of the capacitor?

- Your answer should be like this (2) 200v)

\_\_\_\_\_\_

• Temperature does not affect RC of the wire ?

• ----- The data doesn't have enough time to pass from one register to the next before the next clock edge.

| The data doesn't have enough time to pass from one register to the next before the next clock edge. |

|-----------------------------------------------------------------------------------------------------|

| O A. NA                                                                                             |

| O B. Min Delay                                                                                      |

| C. Max Delay                                                                                        |

| O. Buffer delay                                                                                     |

| The correct answer is: Max Delay                                                                    |

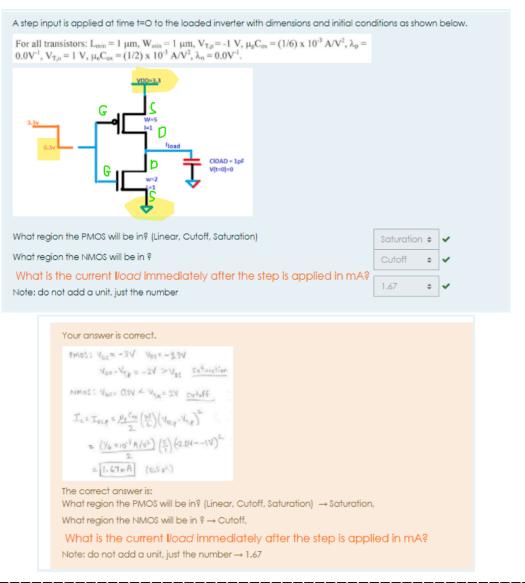

A step input is applied at time t=O to the loaded inverter with dimensions and initial conditions as shown below.

Some of advantages of IC are :

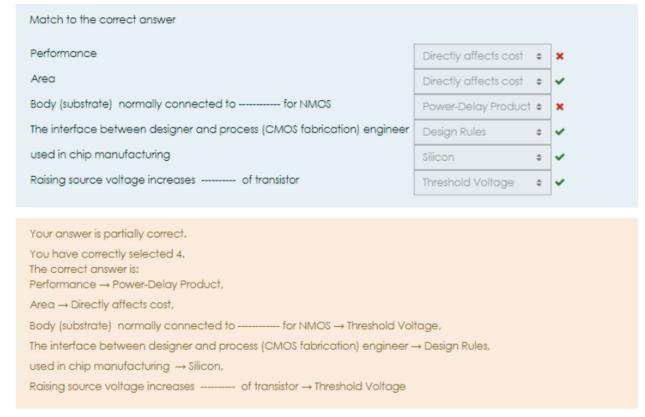

- Match to the correct answer

- Performance

- Area

- Body (substrate) normally connected

Which is faster Holes or Electrons?

\_\_\_\_\_\_

• Increasing fan-out, NCREASE OR DECREASES the propagation delay

For the simulation Image shown below match the number to the right answer

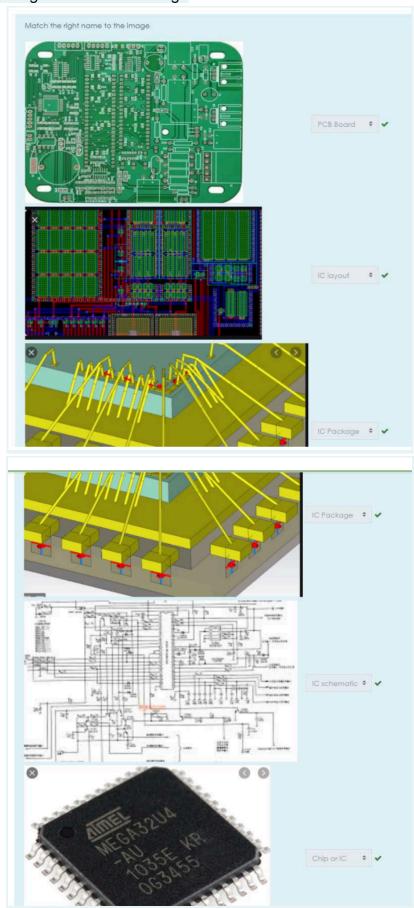

Match the right name to the image

\_\_\_\_\_\_\_\_

• Threshold voltage is negative for

\_\_\_\_\_

• ID and threshold voltag

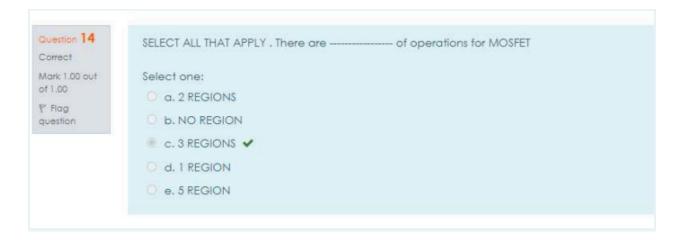

• There are \_\_\_\_\_ of operations for MOSFET

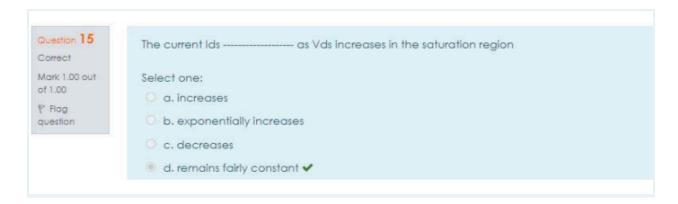

The current Ids \_\_\_\_\_ as Vds increases in the saturation region

\_\_\_\_\_

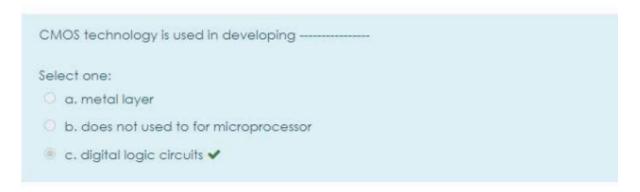

CMOS technology is used in developing

\_\_\_\_\_\_\_

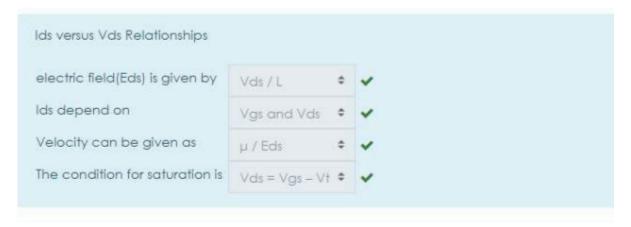

• Ids versus Vds Relationships

In CMOS fabrication, the photoresist layer is exposed to \_\_\_\_

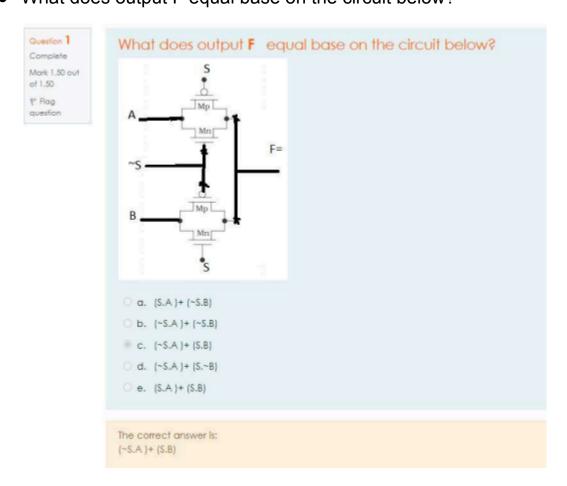

• What does output F equal base on the circuit below?

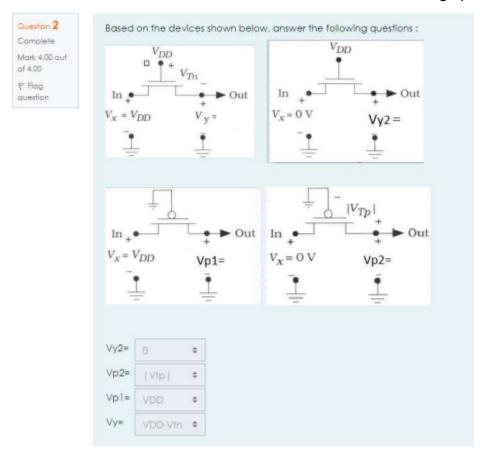

• Based on the devices shown below, answer the following questions

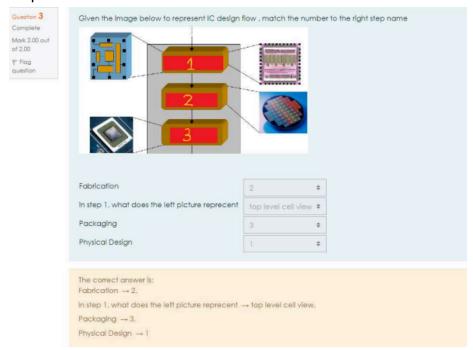

• Given the Image below to represent IC design flow , match the number to the right step name

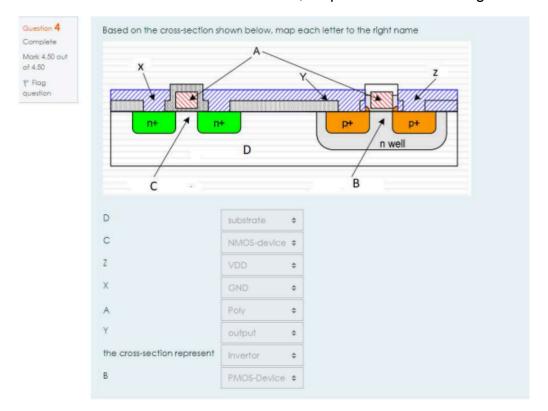

• Based on the cross-section shown below, map each letter to the right name

\_\_\_\_\_\_

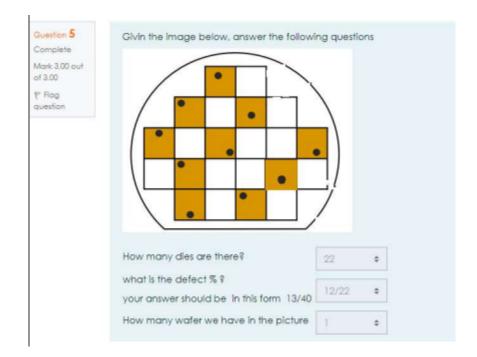

• Givin the image below, answer the following questions

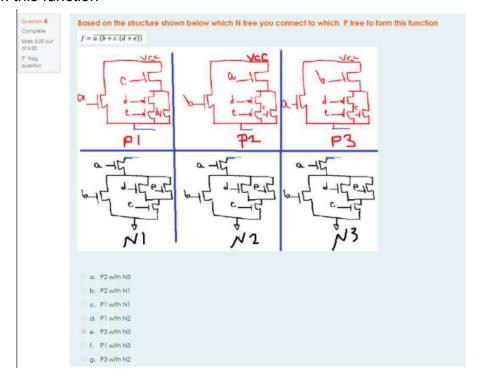

Based on the structure shown below which N tree you connect to which P tree to form this function

\_\_\_\_\_

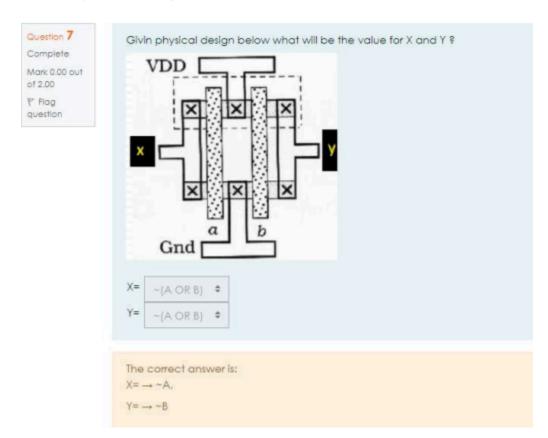

• Givin physical design below what will be the value for X and Y?

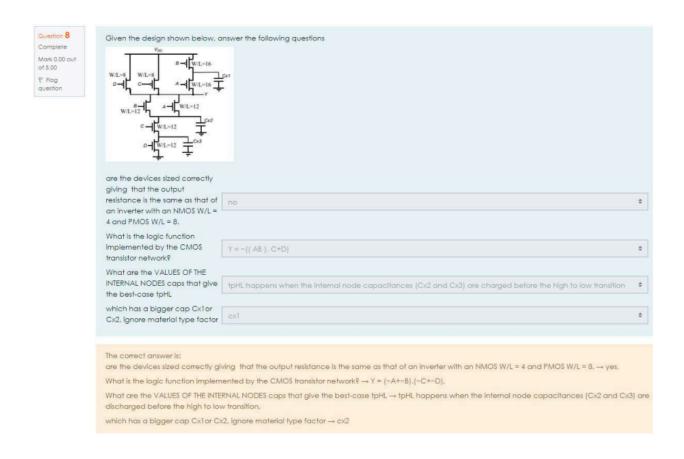

Given the design shown below, answer the following questions

\_\_\_\_\_\_\_\_

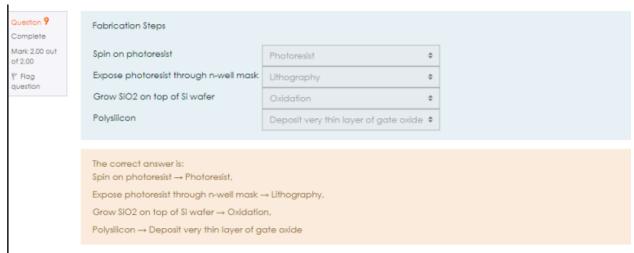

# • Fabrication Steps

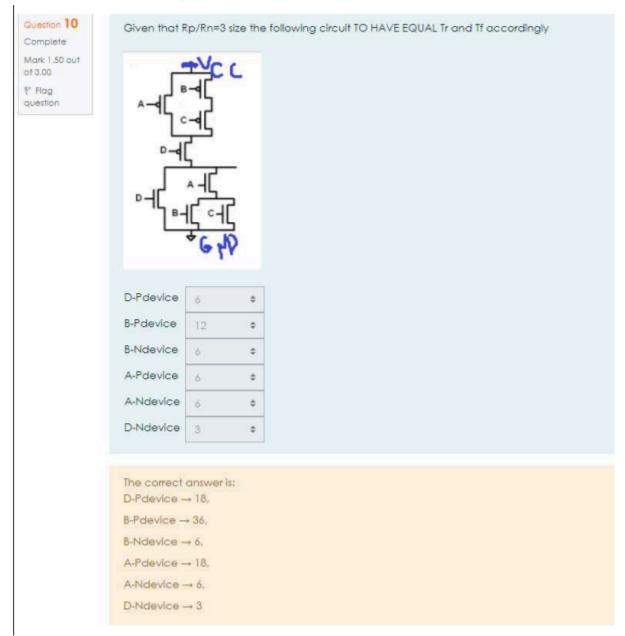

Given that Rp/Rn=3 size the following circuit TO HAVE EQUAL Tr and Tf accordingly

\_\_\_\_\_\_

• When the channel pinches off?

Match the number to the right IC design step/process

\_\_\_\_\_\_\_

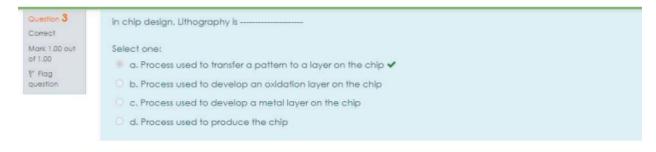

• in chip design. Lithography is

\_\_\_\_\_\_

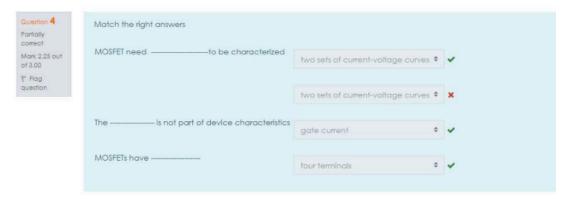

- Match the right answers

- MOSFET need \_\_\_\_\_ to be characterized

- o The \_\_\_\_\_ is not part of device characteristics

- MOSFETs have

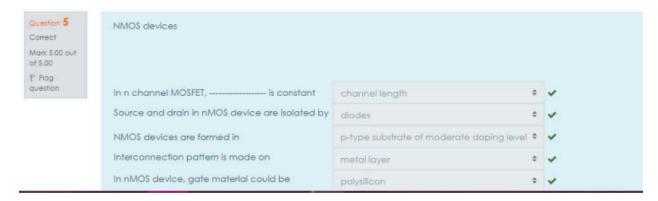

## NMOS devices

\_\_\_\_\_\_\_

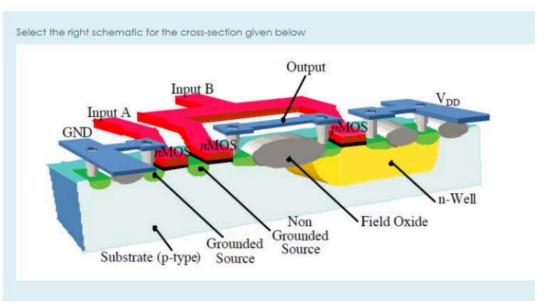

Select the right schematic for the cross-section given below

In CMOS fabrication, nMOS and pMOS are integrated in the same substrate

• Goal of library cell Characterization:

\_\_\_\_\_

• System on chip means

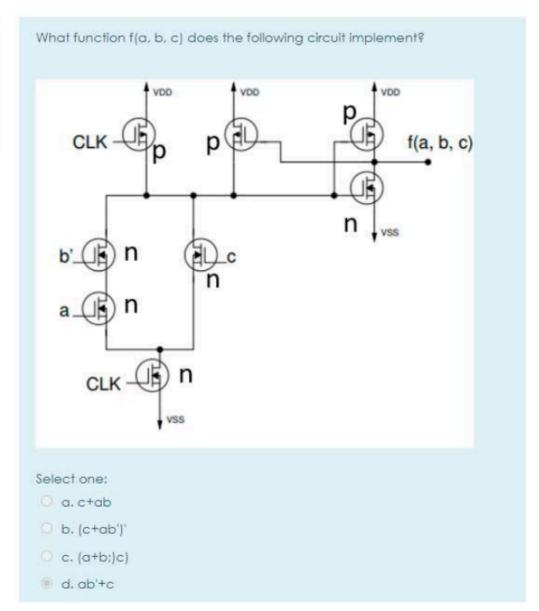

• What function f(a, b, c) does the following circuit implement?

Optical masking is used in IC design for

| Optical masking is used in IC design for |  |

|------------------------------------------|--|

| Select one:                              |  |

| a, Protection of layer                   |  |

| b. Pattern transfer                      |  |

| c. Cleaning unwanted materials           |  |

| O d. none of them                        |  |

n-type semiconductors are

\_\_\_\_\_\_

The packaging is used in IC for

| Question 5 Complete                            | The packaging is used in IC for                                                                              |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Mark 1.00 out<br>of 1.00<br>P Flag<br>question | Select one:  a. safety and protection b. power delivery to each circuit c. none of them d. wire local blocks |

\_\_\_\_\_\_

• Indicate whether each of the following has been increasing or decreasing with process scaling for synchronous integrated circuits.

\_\_\_\_\_\_

Determine the Elmore delay from Node a to Node b in the following circuit.

The PMOSFETs and NMOSFETs in an inverter have been sized to achieve balanced rise and fall times. However, process variation has caused the implementation to deviate from the design. The A line in Figure below is associated with an inverter that has

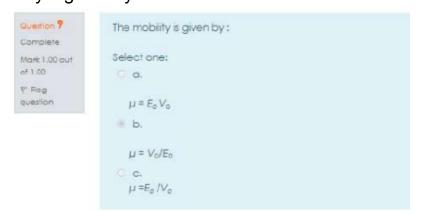

• The mobility s given by:

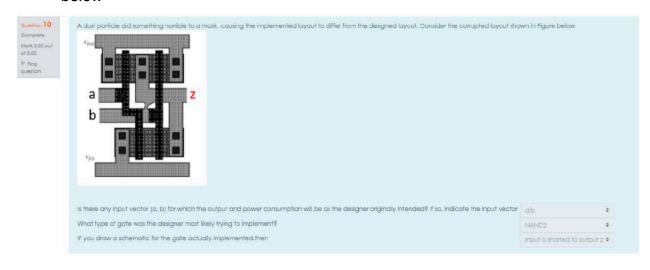

A dust particle did something horible to a mask, causing the implemented layout to differ from the desgned layout. Consider the corrupted layout shown in Figure below

\_\_\_\_\_\_\_

Stick diagrams are those which convey layer information through?

\_\_\_\_\_

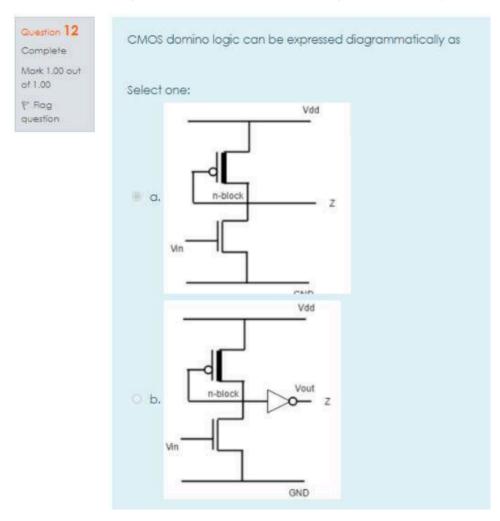

CMOS domino logic can be expressed diagrammafically as

\_\_\_\_\_\_

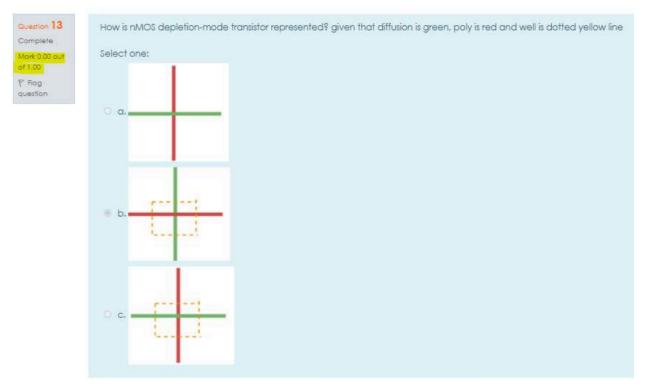

How is nMOS depletion-mode transistor represented? given that diffusion is green, poly is red and well is dotted yellow line

Which contributes to the wiring capacitance?

\_\_\_\_\_\_

• Which has a high voltage drop?

\_\_\_\_\_\_

Consider the following transfer curve

- Match to the correct answer

- Threshold voltage is negative for

- Two metal layers can be joined by using

- When polysilicon crosses a diffusion

- o will be formed

| Match to the correct answer                         |            |           |

|-----------------------------------------------------|------------|-----------|

| Threshold voltage is negative for                   | pmos       | 0         |

| Two metal layers can be joined by using             | via        | <b>\$</b> |

| When polysilicon crosses a diffusion will be formed | transistor | <b>\$</b> |

The overall delay is \_\_\_ to the relative resistance r.

| tion 19    | The overall delay is to the relative resistance r. |

|------------|----------------------------------------------------|

| 1.00 out   | Selectione:                                        |

| 00         | a. exponentially proportional                      |

| ig<br>tion | b. inversely proportional                          |

|            | c. directly proportional                           |

|            |                                                    |

\_\_\_\_\_\_\_

\_\_\_\_\_\_

- Match to correct answer

- In resistive (linear) region

- When the threshold voltage is more, leakage current will be?

- When the channel pinches off?

- Match to the correct answer/choice

- In CMOS logic circuit the n-MOS transistor acts as:

- Register cell consists of

- The size of a transistor is usually defined in terms of its process based on

\_\_\_\_\_\_

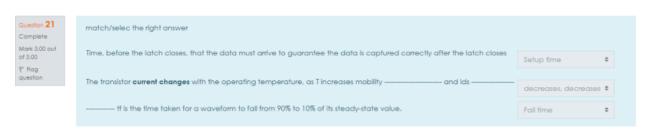

- match/selec the right answer

- Time, before the latch closes, that the data must arrive to guarantee the data is captured correctly after the latch closes

- The transistor current changes with the operating temperature, as T increases mobility

- ff is the fime taken for a waveform to fall from 90% to 10% of its steady-state value.

\_\_\_\_\_\_

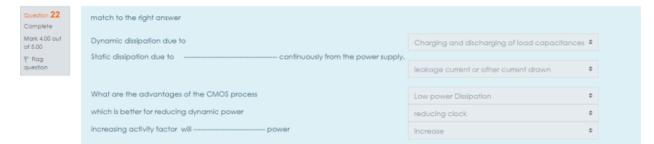

- match to the right answer

- Dynamic dissipation due to

- Static dissipation due to continuously from the power supply.

- What are the advantages of the CMOS process

- which is better for reducing dynamic power

- increasing activity factor will \_\_\_\_\_ power

\_\_\_\_\_\_

• Main Issues In Dynamic Design

\_\_\_\_\_\_

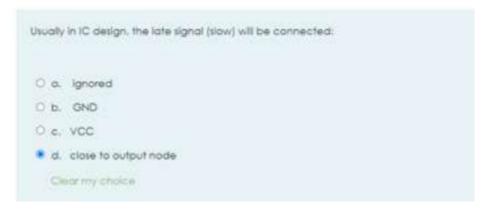

• Usually in IC design, the late signal (slow) will be connected:

\_\_\_\_\_\_\_

\_\_\_\_\_

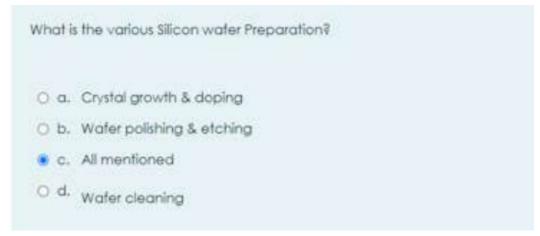

What is the various Silicon wafer Preparation?

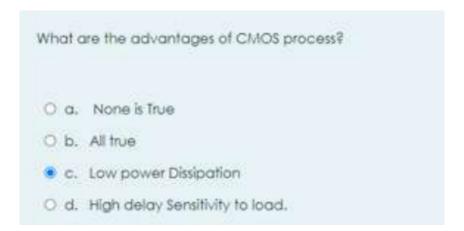

What are the advantages of CMOS process?

\_\_\_\_\_\_\_

Which MOS can pass logic1 and logic 0 stongly?

\_\_\_\_\_\_\_

Ids depends on lds depends on\_ O a. Vss O b. Vdd O c. Vg d. Vds Design rules does not specify Design rules does not specify\_ a. color of each layer O b. Line widths O c. Separations/spaces O d. extensions In basic inverter circuit \_\_\_\_\_ is connected to ground In basic inverter circuit \_\_\_\_\_\_ is connected to ground O a. gate b. source O c. drain • Which among the following is a process of transforming design entry information of the circuit into a set of logic equations? Which among the following is a process of transforming design entry information of the circuit into a set of logic equations? O a. Verification O b. Simulation O c. Optimization d. Synthesis

which process deals with the determination of resistance & capacitance of interconnections? which process deals with the determination of resistance & capacitance of interconnections? O a. Placement b. Extraction O c. Floorplanning O d. Routing \_\_\_\_\_\_\_ Which type of digital systems exhibit the necessity for the existence of at least one teedback path from output to input? Which type of digital systems exhibit the necessity for the existence of at least one feedback path from output to input? a. Sequential system O b. none O c. Combinational System \_\_\_\_\_\_ The time required for an Input data for settie \_\_\_\_\_ the friggering edge of clock is known as 'Setup Time". The time required for an input data to settle \_\_\_\_\_ the triggering edge of clock is known as 'Setup Time'. O a. ALL are correct O b. After O c. During d. Before

Hold fime is defined as the time required for the data to triggering edge of clock. Hold fime is defined as the time required for the data to \_\_\_\_\_ after the triggering edge of clock. a. Remain stable Ob. Increase C. c. Decrease ICs are generally made of ICs are generally made of ..... a. Silicon Ob. None O c. Germanium O.d. Copper • Dynomic power: Dynamic power: O a. change linearly with voltage b. depends on the load capacitance O c. Is not affected by frequency d. all mentioned

\_\_\_\_\_

| <ul> <li>For Standard Cell Physical Structure layout</li> </ul>                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| For Standard Cell Physical Structure layout                                                                                                         |

| O a none                                                                                                                                            |

| b. All the cells in the library are designed to be multiple to unit tile                                                                            |

| O.c. only first row of cell library are designed to be multiple to unit tile                                                                        |

| O d. Placement uses vertical grid only in which cells are placed                                                                                    |

|                                                                                                                                                     |

| <ul> <li>The design flow of IC design system is: 1. architecture design 2. market<br/>requirement 3.Layout 4. HDL coding 5. logic design</li> </ul> |

| The design flow of IC design system is:                                                                                                             |

| 1. architecture design 2. market requirement 3.Layout 4. HDL coding 5. logic design                                                                 |

| A. 5-1-2-4-3                                                                                                                                        |

| B. 2-1-5-3-4<br>C. 2-1-5-4-3                                                                                                                        |

| D. 4-1-3-2-5                                                                                                                                        |

| E. 5-3-2-1-4                                                                                                                                        |

|                                                                                                                                                     |

|                                                                                                                                                     |

| <ul> <li>CMOS NANS gate is better than CMOS NOR gates because</li> </ul>                                                                            |

| CMOS NANS gate is better than CMOS NOR gates because                                                                                                |

| A. CMOS nor takes more space than NAND                                                                                                              |

| B. CMOS NOR uses P channel transistor in parallel.                                                                                                  |

| C. CMOS NAND uses P channel transistor in parallel.                                                                                                 |

| D. Only A and C is correct.                                                                                                                         |

| E. All (A and B and C) are correct                                                                                                                  |

|                                                                                                                                                     |

|                                                                                                                                                     |

| <ul> <li>How many transistors are required to implement a four-input OR using CMOS</li> </ul>                                                       |

| design style?                                                                                                                                       |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?                                              |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?  A. 6                                        |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?  A. 6  B. 8                                  |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?  A. 6  B. 8  C. 10                           |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?  A. 6  B. 8  C. 10  D. 12                    |

| design style?  How many transistors are required to implement a four-input OR using CMOS design style?  A. 6  B. 8  C. 10                           |

\_\_\_\_\_

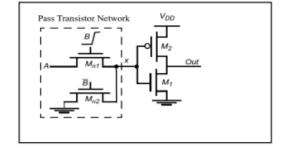

In order to have "pass" logic gate We need

In order to have "pass" logic gate We need

- A. An N-channel and P-Channel transistor in series

- B. We need only p-channel so it will pass good one.

- C. We need only N-channel so it will pass good zero.

- D. An N-channel and P-Channel transistor in parallel

- E. None

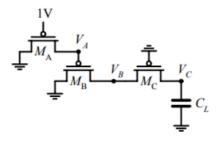

For the circuit in Fig. below, determine the final value of VA, VB, VC, assuming initial condition at each of the nodes is 3V and VTP = -0.5V (ignore body effect).

For the circuit in Fig. below, determine the final value of VA, VB, VC, assuming initial condition at each of the nodes is 3V and VTP = -0.5V (ignore body effect).

- **A.** VA = 3V VB = 2V VC = 1.5V

- **B.** VA = 1.5V VB = 1.5V VC = 1.5V

- **C.** VA = 2V VB = 2V VC = 2V

- **D.** VA = 1.5V VB = 2V VC = 2V

- E. None

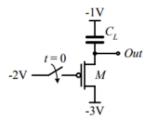

- Assuming that switch as shown in figure below closes at time t = 0, what is the output voltage at t = 0+ and t = oo? CL was initially discharged, VTP = -0.5V.

- 6. Assuming that switch as shown in figure below closes at time t = 0, what is the output voltage at t = 0+ and  $t = \infty$ ? CL was initially discharged, VTP = -0.5V.

- **A.** Vout (t = 0+) = +1V Vout  $(t = \infty) = -1.5V$

- **B.** Vout (t = 0+) = -1V Vout  $(t = \infty) = +1.5V$

- **C.** Vout (t = 0+) = -1V Vout  $(t = \infty) = -1.5V$

- **D.** Vout (t = 0+) = +1V Vout  $(t = \infty) = +1.5V$

- E. None

\_\_\_\_\_\_

\_\_\_\_\_

The delay of a static CMOS inverter is minimized if(W/L)p/ (W/L)n=μη /μρ.

7. The delay of a static CMOS inverter is minimized if  $(W/L)p / (W/L)n = \mu n / \mu p$ .

- A. True

- B. False

- C. None

The load capacitance of a static CMOS gate has no effect on its VTC

8. The load capacitance of a static CMOS gate has no effect on its VTC

- A. False

- B. True

- C. None

\_\_\_\_\_\_

CMOS Transmission (Pass) Gates, capable of passing both '1' and '0'

10. CMOS Transmission (Pass) Gates, capable of passing both '1' and '0'

- A. Good "1"

- B. Good "0"

- C. Poor "1"

- D. Poor "0"

- E. Both A and B only

What is the logic function performed by this circuit?

11. What is the logic function performed by this circuit?

- A. The circuit is a NOR gate.

- B. The circuit is a XOR gate.

- C. The circuit is a NAND gate.

- D. The circuit is a NOT gate.

- E. None

\_\_\_\_\_\_

| <ul> <li>Increasing power supply voltage, VDD, will</li> </ul> |

|----------------------------------------------------------------|

| 12. Increasing power supply voltage, VDD, will                 |

- **A.** Does not change the speed performance of CMOS gates.

- **B.** Increase the speed performance of CMOS gates.

- C. Decrease the speed performance of CMOS gates.

- D. None

\_\_\_\_\_\_

- The IN and OUT bus lines in IC design should be in

- 13. The IN and OUT bus lines in IC design should be in

- A. Metal

- B. Contact

- C. Polysilicon

- D. Diffusion

- E. Silicon

- F. None

\_\_\_\_\_\_

- If an NMOSFET gate's dielectric were changed from SiO2 to a low-k material with half the permittivity of SiO2, what would happen to its ID? You may assume that VGS ≥ VTN

- 14. If an NMOSFET gate's dielectric were changed from SiO2 to a low-κ material with half the permittivity of SiO2, what would happen to its ID? You may assume that VGS ≥ VTN

- A. Id does not change.

- B. ID being halved.

- C. ID doubled.

- D. Id does not change.

- E. None

\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_

- Which one is the right order for the following the following interconnect fabrication steps: . Etch metal. · Expose photoresist using mask. · Remove all photoresist. · Deposit photoresist. . Deposit metal everywhere.

- 15. Which one is the right order for the following the following interconnect fabrication steps:

- Etch metal. Expose photoresist using mask. Remove all photoresist.

- Deposit photoresist.

Deposit metal everywhere.

- A. 1)Deposit metal everywhere. 2) Expose photoresist using mask. 3). Deposit photoresist 4) Etch metal. 5) Remove all photoresist

- B. 1) ) Deposit photoresist 2) Deposit metal everywhere 3) Expose photoresist using mask. 4)

Etch metal. 5) Remove all photoresist

- C. 1)Deposit metal everywhere. 2) Deposit photoresist. 3) Expose photoresist using mask. 4) Etch metal. 5) Remove all photoresist

- D. 1)Deposit metal everywhere. 2) Expose photoresist using mask. 3) Deposit photoresist. 4)

Etch metal. 5) Remove all photoresist

- E. None

\_\_\_\_\_\_\_

CMOS stands for: CMOS stands for: A. complementary material oxide semiconductor B. complementary metal oxide semiconductor C. complex metal oxide semiconductor complex material oxide semiconductor \_\_\_\_\_\_ Chip Yield refers : Chip Yield refers: A. Yield drops as chip area increases B. low yield means high cost C. Yield depends on process parameters D. All of the above Which of the following metal layer has Maximum resistance? Which of the following metal layer has Maximum resistance? A. Metal1 B. Metal2 C. Metal3 D. Metal4 \_\_\_\_\_\_\_ How do you size NMOS and PMOS transistors to increase the threshold voltage? How do you size NMOS and PMOS transistors to increase the threshold voltage? Increase voltage on gate B. Increase voltage on the bias(substrate) C. Lower drain voltage D. Lower drain current \_\_\_\_\_\_

\_\_\_\_\_

What happens to delay if you increase load capacitance?

What happens to delay if you increase load capacitance?

- A. Increase if driver size stay the same

- B. Decrease if driver size stay the same

- C. Has no effect if we make driver smaller

- D. Delay stay the same

\_\_\_\_\_\_\_\_\_\_\_

What are the limitations in increasing the voltage (power supply) to reduce delay?

What are the limitations in increasing the voltage (power supply) to reduce delay?

- A. Delay limits: Increasing voltage increases delay

- B. Power limits: Increasing voltage will result in more power

- C. Area limits: increasing voltage will affect chip area significantly

- D. A and B

What happens if we increase the number of contacts or via from one metal layer to the next?

What happens if we increase the number of contacts or via from one metal layer to the next?

- A. Power dissipation decreased

- B. Increases resistance and power dissipation

- C. Overall resistance decrease

- D. A and C

\_\_\_\_\_\_\_

What is the difference between LVS and DRC FOR LAYOUT?

What is the difference between LVS and DRC FOR LAYOUT?

- The layout must be drawn according to certain strict design rules DRC

- B. Both used in layout to verify delay

- C. None of the above

- D. LVS compares the netlist extracted from the layout with the schematic to ensure that the layout is an identical match to the cell schematic

- E. A and D

| <ul> <li>What are pros/cons of using low Vt, high Vt cells?</li> </ul>                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| What are pros/cons of using low Vt, high Vt cells?                                                                                              |

| A. low Vt cell violates design rules DRC     B. high Vt cells affect delay of the cell so we should not use in speed path                       |

| C. high Vt cells affect leakage power     D. None of the above                                                                                  |

| E. B and C                                                                                                                                      |

|                                                                                                                                                 |

| <ul> <li>The main variables/parasitic that affects power dissipations</li> </ul>                                                                |

| .The main variables/parasitic that affects power dissipations                                                                                   |

| <ul><li>A. low Vt cell violates design rules DRC</li><li>B. high Vt cells affect delay of the cell so we should not use in speed path</li></ul> |

| C. high Vt cells affect leakage power     D. None of the above                                                                                  |

| E. B and C                                                                                                                                      |

|                                                                                                                                                 |

|                                                                                                                                                 |

| In MOS transistors is used for their gate                                                                                                       |

| 7. In MOS transistors, is used for their gate a) metal b) silicon-di-oxide c) polysilicon d) gallium                                            |

| In MOS transistors, polycrystalline silicon is used for their gate region instead of metal. Polysilicon gates                                   |

| have replaced all other older devices.                                                                                                          |

|                                                                                                                                                 |

| <ul> <li>In N channel MOSFET which is the more negative of the elements?</li> </ul>                                                             |

| 10. In N channel MOSFET which is the more negative of the elements?                                                                             |

| a) source b) gate c) drain In N channel MOSFET, source is the more negative of the elements and in the case of P channel                        |

| MOSFET, it is the more positive of the elements.                                                                                                |

|                                                                                                                                                 |

|                                                                                                                                                 |

| <ul><li>MOS transistors consists of what layers ?</li></ul>                                                                                     |

| 6. MOS transistors consists of what layers?                                                                                                     |

| Metal layer, oxide layer and a semiconductor layer.                                                                                             |

|                                                                                                                                                 |

|                                                                                                                                                 |

|                                                                                                                                                 |

|   | <ul> <li>Sllicon-di-oxide is WHAT TYPE OF MATERIALS?</li> <li>Sllicon-di-oxide is WHAT TYPE OF MATERIALS?</li> </ul>                                                                                 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Oxide Material.                                                                                                                                                                                      |

| = | =======================================                                                                                                                                                              |

|   |                                                                                                                                                                                                      |

|   | <ul> <li>In CMOS fabrication, nMOS and pMOS are integrated in the same substrate. IS<br/>THAT TRUE?</li> </ul>                                                                                       |

|   | 4. In CMOS fabrication, nMOS and pMOS are integrated in the same substrate. IS                                                                                                                       |

|   | THAT TRUE?                                                                                                                                                                                           |

|   | n CMOS fabrication, nMOS and pMOS are integrated in the same chip substrate. n-type and p-ty<br>levices are formed in the same structure.                                                            |

| = |                                                                                                                                                                                                      |

|   | NA/II: 1 ( CONTOO : 1/                                                                                                                                                                               |

|   | <ul> <li>Which type of CMOS circuits are good and better?</li> </ul>                                                                                                                                 |

|   | 16. Which type of CMOS circuits are good and better?                                                                                                                                                 |

|   | <ul><li>a) p well b) n well c) all of the mentioned d) none of the mentioned</li><li>N-well CMOS circuits are better than p-well CMOS circuits because of lower substrate bias effectives.</li></ul> |

| _ | ·<br>====================================                                                                                                                                                            |

| _ |                                                                                                                                                                                                      |

|   | <ul><li>Which layer has high capacitance value? metal or diffusion?</li></ul>                                                                                                                        |

| 1 | 25. Which layer has high capacitance value? metal or diffusion?                                                                                                                                      |

| ] | Diffusion or active layer has high capacitance value due to which it has low or moderate IR drop                                                                                                     |

| = |                                                                                                                                                                                                      |

|   |                                                                                                                                                                                                      |

|   | <ul><li>Which layer has high resistance value? polysilicon or metal?</li></ul>                                                                                                                       |

| 2 | 26. Which layer has high resistance value? polysilicon or metal?                                                                                                                                     |

| ] | Polysilicon layer has high resistance value and due to this it has high IR drop                                                                                                                      |

| = |                                                                                                                                                                                                      |

|   |                                                                                                                                                                                                      |

|   | <ul> <li>Overall delay increases as n where n is the number of pass</li> </ul>                                                                                                                       |

|   | transistors connected in series. increases or decreases?                                                                                                                                             |

|   | 30. Overall delay increases as n where n is the number of pass transistors connected                                                                                                                 |

|   | ·                                                                                                                                                                                                    |

|   | series. increases or decreases?  Overall delay increases as n increases where n is the number of pass transistors connected in series                                                                |

STUDENTS-HUB.com

Uploaded By: Amr Halahla

\_\_\_\_\_\_

- What is the logic function of the following gate?

- 1. What is the logic function of the following gate?

O=ABCD

\_\_\_\_\_

- What is the output function of the following circuit?

- 6. What is the output function of the following circuit?

**XOR**

\_\_\_\_\_\_

### **True or False**

- (T) Transmission gates are needed to pass both 0 and 1

- (T) nMOS pass transistors pull no higher than VDD-Vtn

- (T) Process can be defined as a sequence of steps used to form circuits on a wafer

- (T) Field Oxide used for Isolation between devices

- (T) Transistor's current saturates at high Vds values

- (T) Nwell and Substrate must be connected to the power supply within each cell

- (T) If we now want to create an n-type channel below the Si-SiO2 surface we need to

- increase VGS. As VGS is increased the Si close to the surface first becomes depleted of holes and only then (at higher VGS) electrons start to build the channel.

- (T) We can define the 'threshold voltage' as the VGS that below it the transistor's current (IDS) effectively drops to zero

- (T) Poly or gate materials have a high-resistance conductor (can be used for short routing)

- (T) We have Design Rules because the fabrication process has minimum/maximum feature sizes that can be produced for each layer

- (F) To set the switching threshold (midpoint) voltage, Vm, to VDD/2 in a CMOS inverter, the nMOS transistor must be wider than the pMOS.

- (T) Increasing power supply voltage, VDD, will increase the speed performance of CMOS gates.

- (F) The best way to improve the speed performance of a CMOS circuit is to decrease the channel

- (T) CMOS = Complementary MOS use of both nMOS and pMOS to form a circuit with lowest power consumption.

- (T) Electric Fields: vertical field through gate oxide determines charge induced in channel while horizontal field across channel determines source-to-drain current flow

- (F) pMOS switching behavior device will be on = closed, when Vin > VDD |Vtp| and will be off = open, when Vin < VDD - |Vtp|</li>

- (T) 'source' is at lowest potential for nMOS and highest potential for pMOS

- (F) Logic gates are created by using sets of controlled switches. nMOS acts like an assert-low switch and pMOS acts like an assert-high switch

- (T) CMOS is inherently Inverting logic,

- (T) CMOS Transmission Gates, capable of passing both '1' and '0'

- (T) Speed power product is measured as the product of switching delay and gate power dissipation is that true?

- (T) Lithography is Process used to transfer a pattern to a layer on the chip , IS THAT TRUE

- (F) CMOS inverter has 2 regions of operation, is that true?

- (F) Polysilicon is suitable for connecting to VDD or vss grid, is that true?

- (T) During the floor planning step the overall cell is defined, including: cell size, supply network, etc

- (T) If a designer wants a perfectly balanced rise time and fall time for a CMOS inverter driving a capacitive load, Since the mobility of electrons is normally twice the mobility of holes, we need to make the width of PMOS twice as large as the width of NMOS.

- (T) Does the IC have a good chance of implementing the desired logic functions

Select the correct statement regarding pipeline concept in sequential circuit

| Question 7                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Complete                                                                                                                                                                                                                                                                                                                 |

| Mark 1.00 out of 1.00                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                          |

| Select the correct statement regarding pipeline concept in sequential circuit                                                                                                                                                                                                                                            |

| <ul> <li>A. using a pipeline, we can make our fastest path shorter and therefore increase the delay<br/>between actions.</li> </ul>                                                                                                                                                                                      |

| □ B. NA                                                                                                                                                                                                                                                                                                                  |

| C. using a pipeline, we can make our slowest path shorter and therefore reduce the delay<br>between actions.                                                                                                                                                                                                             |

| D. some stages may be faster than others, so we need to hold the input to each stage constant<br>until the previous stage is done. We achieve this by adding a register in between the stages                                                                                                                            |

| The correct answers are: some stages may be faster than others, so we need to hold the input to each stage constant until the previous stage is done. We achieve this by adding a register in between the stages, using a pipeline, we can make our slowest path shorter and therefore reduce the delay between actions. |

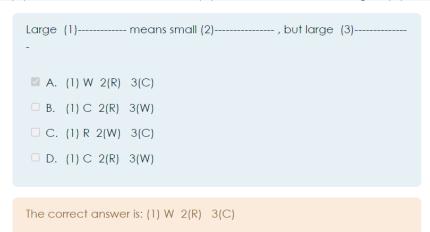

• Large (1)----- means small (2)-----, but large (3)-----

\_\_\_\_\_\_

> Back-to-School savings now on! Purchase before September 30th, and get 25% off Socrative Pro.

> Enter coupon code "BTS20" at checkout. Learn More

Remind me later

KH1STSEM2021

Save and Exit

## ENCS333\_SEC1\_QZ2

#### Align Quiz to Standard

**Enable Sharing** SOC-51204796

- 1. Define Threshold voltage in CMOS ? SELECT ALL RIGHT ANSWER

- The Threshold voltage, VT for a MOS transistor can be defined as the voltage applied between the gate and the drain of the MOS transistor below which the gate to source current, IGS effectively drops to zero

The Threshold voltage, VT for a MOS transistor can be defined as the voltage applied between the gate and the bulk of the MOS transistor below which the drain to source current, IDS effectively reach maximum value

- The Threshold voltage, VT for a MOS transistor can be defined as the voltage applied between the gate and the source of the MOS transistor below which the drain to source current, IDS effectively drops to zero

- All are true

- 2. a MOS transistor can be considered as ----- ( select all that apply)

A resistive load in leaner region

10/12/2020 Socrative current source in saturation region C short circuit in cutt off ۲⊕ D open circuit all the time 3. If a large ----- is applied this voltage with deplete the Inversion layer .This Voltage effectively pinches off the channel near the 뻬 source VGS **VDS** VSB ſĤ **D** VGB 4. There are four main different layers in MOS transistors which are Drain, Source, Gate, bulk 뻬 B capacitance, resistance, inductance, voltage C waver, package, diod, voltage ſψ 5. The transistor current changes with the operating temperature but is not affected by mobility 뻬 **False** ۲⊕

| <ul> <li>6. As the channel length decreases, the depletion region below gate can no longer be approximated as a rectangular region. S as L</li> <li>A does not change</li> <li>B increases</li> <li>C decreases</li> </ul> |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>7. As Vd is higher, the drain depletion region increases, causing a in Vt.</li> <li>A decrease</li> <li>B increase</li> </ul>                                                                                     | a  □     |

| <ul> <li>8. For MOS devices, leakage current occurs in what region</li> <li>A Linear</li> <li>B Saturation</li> <li>C cutt off</li> </ul>                                                                                  | 1 ↑ ↓    |

| <ul><li>9. For the same VDS, as VGS increases, The IDS will</li><li>A increase</li><li>B decrease</li></ul>                                                                                                                | <b>□</b> |

C does not change

ſŧ

10. Hot-e degradation will occure when: When,

A a MOS transistor is in Linear region, , the electric field across the pinch-off region may be high enough that carriers gain there enough energy to excite electron-hole pairs.

**B** a MOS transistor is in cutt off region, the electric field across the pinch-off region may be high enough that carriers gain there enough energy to excite electron-hole pairs.

- a MOS transistor is in saturation, the electric field across the pinchoff region may be high enough that carriers gain there enough energy to excite electron-hole pairs.

- **D** In all regions

Add a Question

**Multiple Choice**

True / False

**Short Answer**

Socrative Get PRO! Learn More

| Name |  |

|------|--|

| Date |  |

# ENCS333 QZ1 MARCH 24

Score \_\_\_\_\_

| 1. What are the different operating regions foe a MOS transistor?                                           |

|-------------------------------------------------------------------------------------------------------------|

| A Cutoff region                                                                                             |

| B Non- Saturated Region                                                                                     |

| © Saturated Region                                                                                          |

| D All are correct                                                                                           |

|                                                                                                             |

| 2. What are the different MOS layers?                                                                       |

| A n-diffusion                                                                                               |

| B p-diffusion                                                                                               |

| © Polysilicon                                                                                               |

| (D) Metal                                                                                                   |

| E all of the above                                                                                          |

|                                                                                                             |

| 3. What are the various Silicon wafer Preparation?                                                          |

| (A) Crystal growth & doping                                                                                 |

| B Ingot trimming & grinding                                                                                 |

| C Verilog code preparation                                                                                  |

| D Wafer polishing & etching and Wafer cleaning.                                                             |

| E all of the above are correct except Verilog code preparation                                              |

|                                                                                                             |

| <b>4.</b> If a large Vds is applied this voltage with deplete the Inversion layer .This Voltage effectively |

| pinches off the channel near the source.  (T) True                                                          |

| (F False                                                                                                    |

|                                                                                                             |

| 5. There are only three different layers in MOS transistors which are Drain, Source & Gate                  |

| (T) True                                                                                                    |

| F False                                                                                                     |

|                                                                                                             |

|                   | be defined as the voltage applied between the gate and the source of the MOS transistor below which the drain to source current, IDS effectively drops to zero.                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T                 | True                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F                 | False                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.                | The Channel-length modulatio, the The current between <u>drain and source terminals is</u> <u>constant and</u> independent of the applied voltage over the terminals. This is not entirely correct. The effective length of the conductive channel is actually modulated by the applied VDS, increasing VDS causes the depletion region at the drain junction to grow, reducing the length of the effective channel. |

| T                 | True                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F                 | False                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.                | Define Rise time ? which device nMOS or PMOS determines the Rise time?                                                                                                                                                                                                                                                                                                                                               |

| In slide          | es rise related to p device size, we mesure 20-80% of the rise signal                                                                                                                                                                                                                                                                                                                                                |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.                | Define Fall time? which device nMOS or PMOS determines the fall time?                                                                                                                                                                                                                                                                                                                                                |

| In slid           | es fall related to ndevice, same we mesure 20-80% of fall time                                                                                                                                                                                                                                                                                                                                                       |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10                |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   | Define Delay time ?                                                                                                                                                                                                                                                                                                                                                                                                  |

| In slide<br>Betwe | es<br>een two signal or input and output measured at 50%                                                                                                                                                                                                                                                                                                                                                             |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |

**6.** Threshold voltage in CMOS Defined as: The Threshold voltage, VT for a MOS transistor can

11. What are the different operating regions for an NMOS transistor IN EACH REGION AS SHOWN IN THE FIGURE?

In slides

| 11 5110 | ues .  |      |      |

|---------|--------|------|------|

|         | REGION | nMos | pMOS |

|         | A      |      |      |

|         | 5      |      |      |

|         | В      |      |      |

|         | c      |      |      |

|         |        |      |      |

|         | D      |      |      |

|         | F      |      |      |

|         | E      |      |      |

Back-to-School savings now on! Purchase before September 30th, and get 25% off Socrative Pro.

Remind me later

Enter coupon code "BTS20" at checkout. Learn More

KH1STSEM2021

**You're back online!** Missing some results? Try <u>refreshing</u>.

#### **Save and Exit**

### ENCS333\_SEC2\_SEP22

### Align Quiz to Standard

**Enable Sharing** SOC-50727200

- 1. To have a complement CMOS we do not need

- A n-type transistors

**B** p-type transistors

C package

(<del>†</del>

- 2. What are the different parts of MOS transistors?

- A Drain , Source & Gate and bulk

**B** Source & Gate

C Drain, Source

D Drain, Source & Gate

**(**

E bulk, Drain, Source

3. we can classify IC according to Signal Type 凬 Signal Name Analog or digital **(** The first transistor was created in 뻬 Bell Labs China C circuit design ۲₽ 5. Moore's law stated that the number of transistors in ICs doubles every ----- months 凬 2 years 17 months 16 months ۲₽ 18 months 6. Technology shrinks or scaling, refers to which parameter of the transistor 뻬 Drain

| C Gate length                                | <b>\</b>       |

|----------------------------------------------|----------------|

| <b>D</b> bulk                                | <del>(+</del>  |

|                                              |                |

| <b>7.</b> We need a to run spice simulations |                |

|                                              | <del>- D</del> |

| A device model                               | <del>iii</del> |

| <b>B</b> power                               | <b>↑</b>       |

| <b>C</b> ground                              | $\downarrow$   |

| <b>D</b> netlist                             | <del>(</del>   |

| E all mentioned                              |                |

|                                              |                |

| 8. in chip design, Wafer made of             |                |

| The only design, water made of               |                |

| A silicon                                    |                |

| <b>B</b> Germanium                           | <b>^</b>       |

| <b>C</b> copper                              | J              |

| D None of mentioned                          | •              |

|                                              | <b>⊕</b>       |

|                                              |                |

| 9. Die is larger than a waver                |                |

| False                                        |                |

| raise                                        |                |

|                                              | <b>^</b>       |

|                                              | $\downarrow$   |

|                                              | <del>(</del>   |

|                                              | _              |

10. package is technology used to interface between die and outside word 凬 True ۲₽ 11. CMOS stands for -----凬 complementary material oxide state commuter material or silicon commuter metal organization states C complementary metal oxide silicon ſΨ Non of above Ε 12. which sentences is true a bout Ntype and Ptype transistor 뻬 they both made of silicon they both use as switch Ntype is slow ptype is faster than ntype ۲₽ Both use to build CMOS logic

### Add a Question

Multiple Choice True / False Short Answer

Back-to-School savings now on! Purchase before September 30th, and get 25% off Socrative Pro.

Enter coupon code "BTS20" at checkout. Learn More

Remind me later

KH1STSEM2021

**You're back online!** Missing some results? Try <u>refreshing</u>.

Save and Exit

### ENCS333\_SEC1\_SEP22

### Align Quiz to Standard

**Enable Sharing** SOC-50660792

- 1. What is the transistors CMOS technology provides?

- A n-type transistors only

**B** p-type transistors only

c n-type transistors and p-type transistors

D non of the above

- 2. What are the different layers in MOS transistors?

- **A** Drain

**B** Source & Gate

C Drain, Source

**D** Drain , Source & Gate

- E bulk, Drain, Source

- F Drain, Source & Gate and bulk

3. IC Classified according to 뻬 Signal Type Signal Name Number of devices used ſΨ 4. 1948, The first ----- was created in Bell Labs 凬 computer transistor high performance computer ۲₽ 5. Moore's law was discovered, according to which the number of transistors in ICs doubles every ----- months 凬 3 years Α 24 months 18 months ſψ 6 months **6.** Technology shrinks or scaling, refers to which parameter of the transistor

圃

| <ul><li>10. package is technology used to interface between disword</li><li>True</li></ul> | ie and outside                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |