# **Combinational Logic**

#### ENCS2340 - Digital Systems

### Dr. Ahmed I. A. Shawahna Electrical and Computer Engineering Department Birzeit University

STUDENTS-HUB.com

### **Presentation Outline**

#### Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

### **Combinational Circuits**

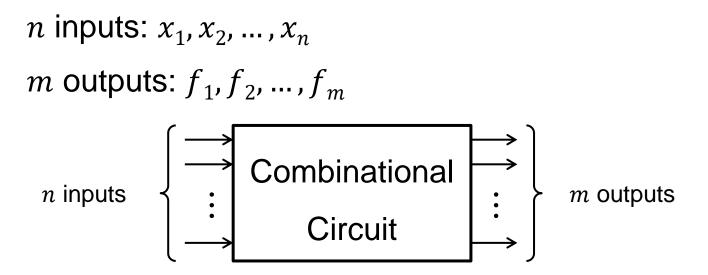

✤ A combinational circuit is a block of logic gates having:

- Each output is a function of the input variables

- Each output is determined from present combination of inputs

- Combination circuit performs operation specified by logic gates

The logic diagram has no feedback paths or memory elements

STUDENTS-HUB.com

Uploaded By: Malak Dar Obaid

ENCS2340 - Digital Systems

Uploaded By: Malak Dar Obaid

### **Combinational Circuits**

- ✤ Analysis:

- ♦ Given a circuit (a logic diagram), find out its function

- $\diamond$  Function may be expressed as:

- Boolean function

- Truth table

- Design:

- ♦ Given a desired function, determine its circuit (logic diagram)

- $\diamond$  Function may be expressed as:

- Boolean function

- Truth table

STUDENTS-HUB.com

Uploaded By: Malak Dar Obaid A Shawahna - slide 4

# Functional Blocks

- ✤ A functional block is a combinational circuit

- We will study blocks, such as decoders and multiplexers

- Functional blocks are very common and useful in design

- In the past, functional blocks were integrated circuits

SSI: Small Scale Integration = tens of gates

MSI: Medium Scale Integration = hundreds of gates

LSI: Large Scale Integration = thousands of gates

VLSI: Very Large Scale Integration = millions of gates

- Today, functional blocks are part of a design library

- Tested for correctness and reused in many projects

STUDENTS-HUB.com

### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

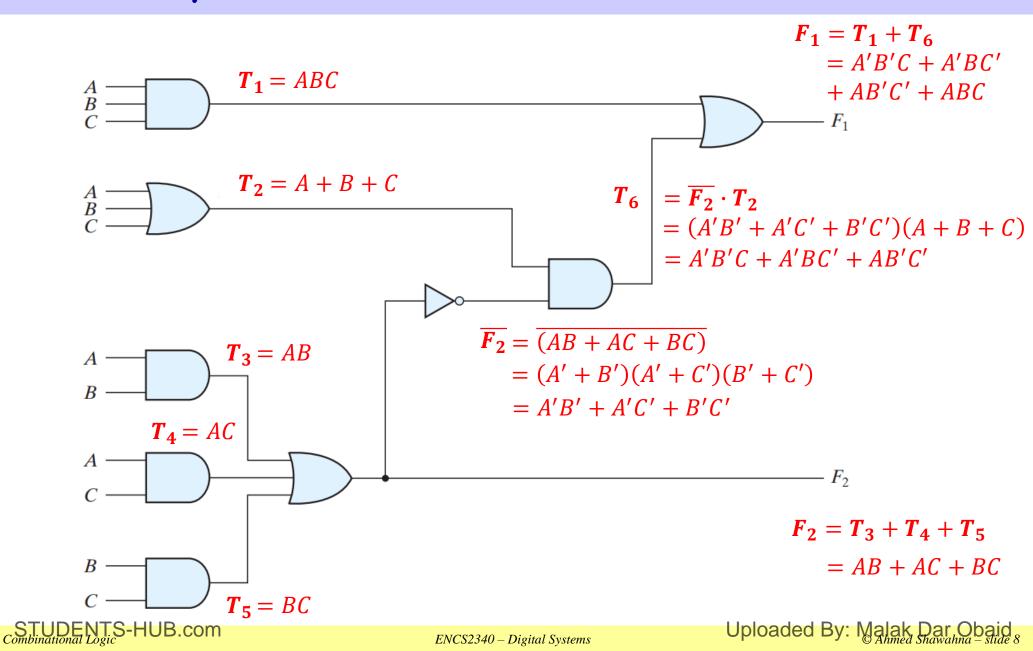

### Analysis Procedure - Boolean Function

- 1. Label all gate outputs that are a function of input variables with symbols. Determine the Boolean function for each gate output.

- Label the gates that are a function of input variables and previously labeled gates with other symbols. Find the Boolean functions for these gates.

- 3. Repeat step 2 until output of circuits are obtained.

- 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

### Analysis Procedure - Boolean Function

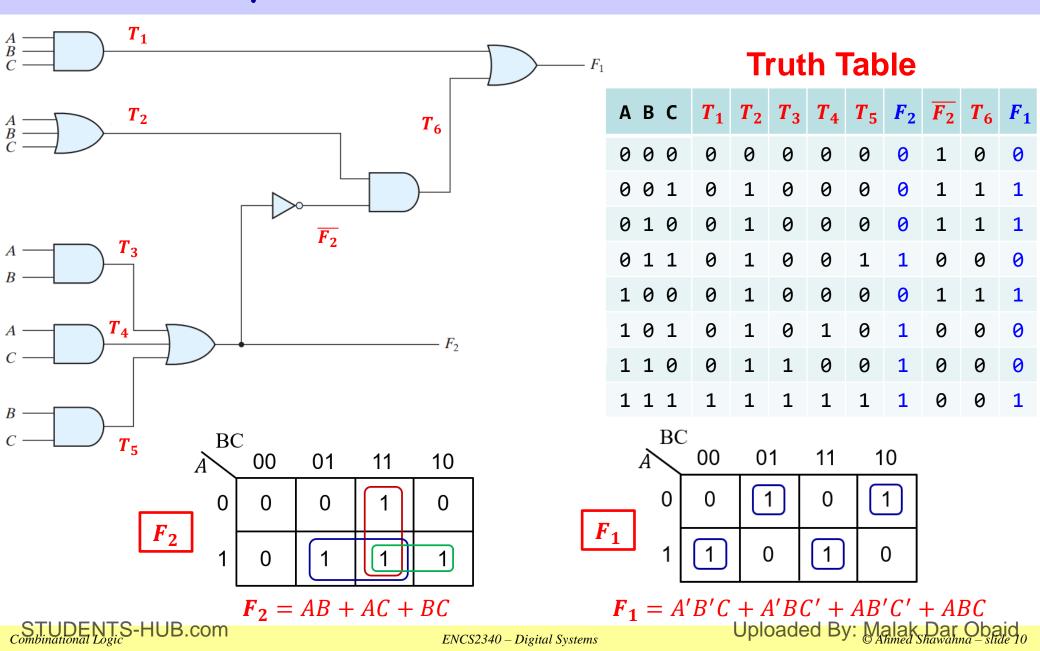

### Analysis Procedure - Truth Table

- 1. Determine the number of input variables in the circuit. For n inputs, form the  $2^n$  possible input combinations and list the binary numbers from 0 to  $(2^n 1)$  in a table.

- 2. Label the outputs of selected gates with arbitrary symbols.

- 3. Obtain the truth table for the outputs of those gates which are a function of the input variables only.

- Proceed to obtain the truth table for the outputs of those gates which are a function of previously defined values until the columns for all outputs are determined.

### Analysis Procedure - Truth Table

### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- ♦ Designing a BCD to Excess-3 Code Converter

- ♦ Designing a BCD to 7-Segment Decoder

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

STUDENTS-HUB.com

# How to Design a Combinational Circuit

#### 1. Specification

♦ Specify the inputs, outputs, and what the circuit should do

#### 2. Formulation

♦ Convert the specification into truth tables or logic expressions for outputs

#### 3. Logic Minimization

♦ Minimize the output functions using K-map or Boolean algebra

#### 4. Technology Mapping

- ♦ Draw a logic diagram using ANDs, ORs, and inverters

- ♦ Map the logic diagram into the selected technology

- ♦ Considerations: cost, delays, fan-in, fan-out

#### 5. Verification

$\diamond$  Verify the correctness of the design, either manually or using simulation

### Verification Methods

- Manual Logic Analysis

- ♦ Find the logic expressions and truth table of the final circuit

- ♦ Compare the final circuit truth table against the specified truth table

- ♦ Compare the circuit output expressions against the specified expressions

- ♦ Tedious for large designs + Human Errors

- Simulation

- ♦ Simulate the final circuit, possibly written in HDL (such as Verilog)

- $\diamond$  Write a test bench that automates the verification process

- ♦ Generate test cases for ALL possible inputs (exhaustive testing)

- $\diamond$  Verify the output correctness for ALL input test cases

- ♦ Exhaustive testing can be very time consuming for many inputs

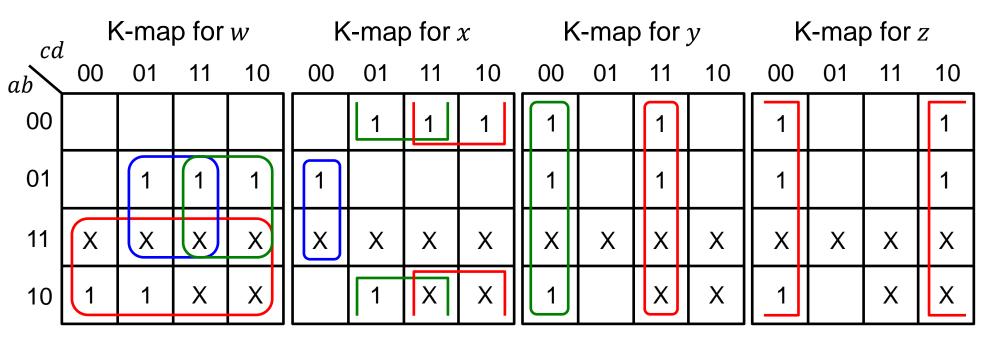

#### 1. Specification:

- ♦ Input: BCD code for decimal digits 0 to 9

- ♦ Output: Excess-3 code for digits 0 to 9

- ♦ Convert BCD code to Excess-3 code

#### 2. Formulation:

Combinational Logic

- $\diamond$  Done easily with a truth table

- $\diamond$  BCD input: *a*, *b*, *c*, *d*

- $\diamond$  Excess-3 output: *w*, *x*, *y*, *z*

- ♦ Output is don't care for 1010 to 1111

| BCD  |     |      | Excess-3 |   |   | s-3 |

|------|-----|------|----------|---|---|-----|

| a b  | o c | d    | W        | Х | у | z   |

| 00   | 9 0 | 0    | 0        | 0 | 1 | 1   |

| 0 0  | 90  | 1    | 0        | 1 | 0 | 0   |

| 00   | 91  | 0    | 0        | 1 | 0 | 1   |

| 0 0  | 91  | 1    | 0        | 1 | 1 | 0   |

| 0 1  | 10  | 0    | 0        | 1 | 1 | 1   |

| 0 1  | 10  | 1    | 1        | 0 | 0 | 0   |

| 0 1  | 1 1 | 0    | 1        | 0 | 0 | 1   |

| 0 1  | 1 1 | 1    | 1        | 0 | 1 | 0   |

| 1 0  | 9 0 | 0    | 1        | 0 | 1 | 1   |

| 1 (  | 9 0 | 1    | 1        | 1 | 0 | 0   |

| 1010 | to  | 1111 | X        | Х | Х | Х   |

#### **3. Logic Minimization using K-maps:**

Minimal Sum-of-Products expressions:

w = a + bc + bd, x = b'c + b'd + bc'd', y = cd + c'd', z = d'

Additional 3-Level Optimizations: extract common term (c + d)

$$w = a + b(c + d)$$

,  $x = b'(c + d) + b(c + d)'$ ,  $y = cd + (c + d)'$

STUDENTS-HUB.com

Uploaded By: Malak Dar Obaid, CAnmed Shawahna - slide 15

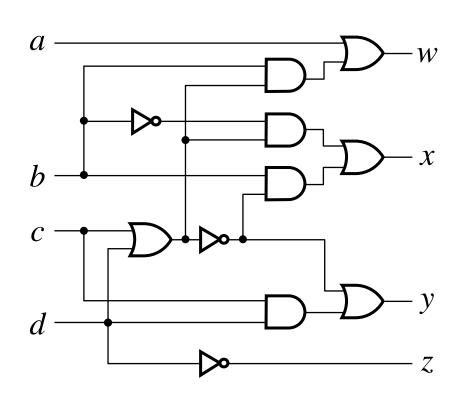

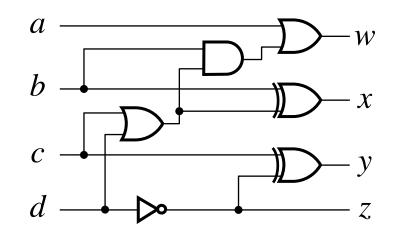

#### 4. Technology Mapping:

Draw a logic diagram using ANDs, ORs, and inverters

Other gates can be used, such as NAND, NOR, and XOR

Combinational Logic

### Using XOR gates $x = b'(c+d) + b(c+d)' = b \oplus (c+d)$ $y = cd + c'd' = (c \oplus d)' = c \oplus d'$

ENCS2340 – Digital Systems

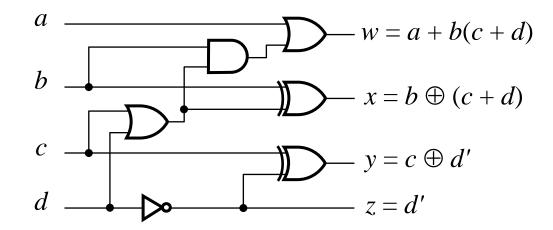

#### 5. Verification:

Combinational Logic

Can be done manually

Extract output functions from circuit diagram Find the truth table of the circuit diagram Match it against the specification truth table Verification process can be automated Using a simulator for complex designs

#### Truth Table of the Circuit Diagram

| BCD     |     |        | Ex | Ce | ess | s-3 |

|---------|-----|--------|----|----|-----|-----|

| a b c d | c+d | b(c+d) | W  | X  | у   | z   |

| 0000    | 0   | 0      | 0  | 0  | 1   | 1   |

| 0001    | 1   | 0      | 0  | 1  | 0   | 0   |

| 0010    | 1   | 0      | 0  | 1  | 0   | 1   |

| 0011    | 1   | 0      | 0  | 1  | 1   | 0   |

| 0100    | 0   | 0      | 0  | 1  | 1   | 1   |

| 0101    | 1   | 1      | 1  | 0  | 0   | 0   |

| 0110    | 1   | 1      | 1  | 0  | 0   | 1   |

| 0111    | 1   | 1      | 1  | 0  | 1   | 0   |

| 1000    | 0   | 0      | 1  | 0  | 1   | 1   |

| 1001    | 1   | 0      | 1  | 1  | 0   | 0   |

Uploaded By: Malak Dar Obaid

ENCS2340 – Digital Systems

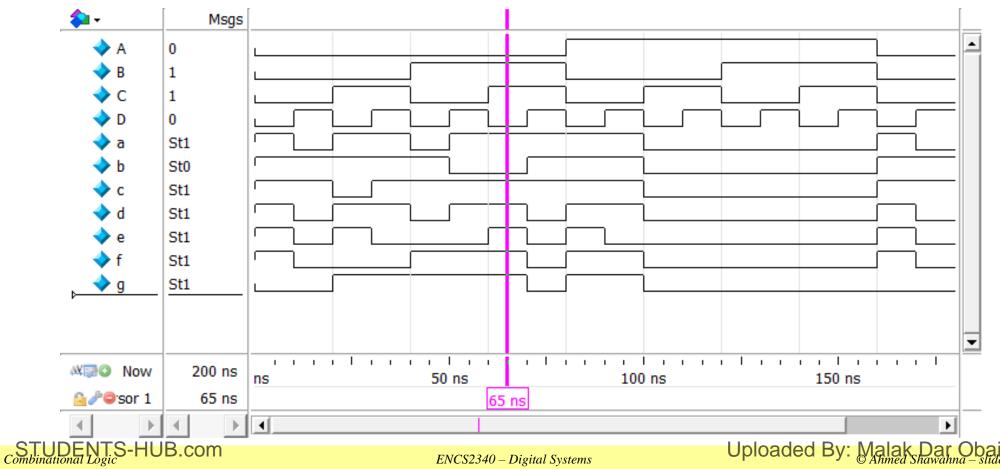

#### 5. Verification:

Run the simulation of the circuit

Do the simulation output combinations match the original specification truth table?

STUDENTS-HUB.com

ENCS2340 – Digital Systems

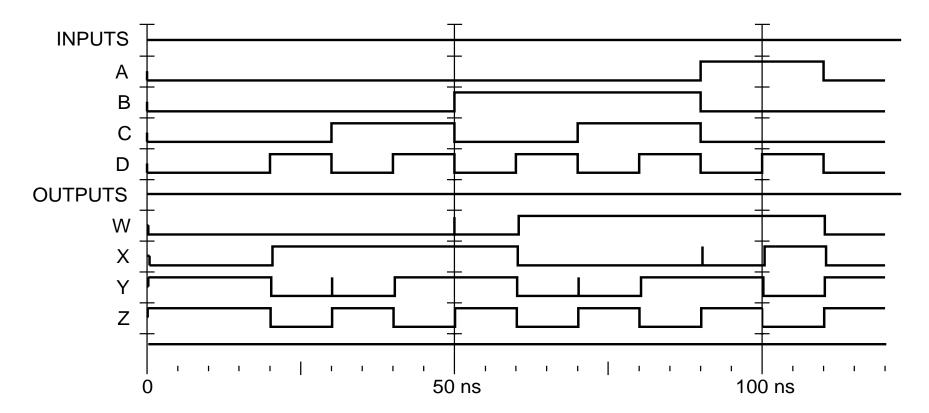

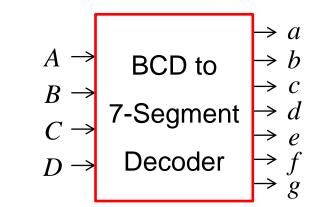

# BCD to 7-Segment Decoder

- Seven-Segment Display:

- ♦ Made of Seven segments: light-emitting diodes (LED)

- ♦ Found in electronic devices: such as clocks, calculators, etc.

0 123456789

- BCD to 7-Segment Decoder

- ♦ Accepts as input a BCD decimal digit (0 to 9)

- $\diamond\,$  Generates output to the seven LED segments to display the BCD digit

- $\diamond$  Each segment can be turned on or off separately

#### 1. Specification:

- $\diamond$  Input: 4-bit BCD (A, B, C, D)

- $\diamond$  Output: 7-bit (*a*, *b*, *c*, *d*, *e*, *f*, *g*)

- Display should be OFF for

Non-BCD input codes

#### 2. Formulation:

- $\diamond$  Done with a truth table

- $\diamond$  Output is zero for 1010 to 1111

Combinational Logic

# 0 823456789

#### **Truth Table**

| BCD input    | 7-Segment decoder |

|--------------|-------------------|

| ABCD         | abcdefg           |

| 0000         | 1 1 1 1 1 1 0     |

| 0001         | 0110000           |

| 0010         | 1 1 0 1 1 0 1     |

| 0011         | 1 1 1 1 0 0 1     |

| 0100         | 0110011           |

| 0101         | 1011011           |

| 0110         | 1011111           |

| 0111         | 1110000           |

| 1000         | 1 1 1 1 1 1 1     |

| 1001         | 1 1 1 1 0 1 1     |

| 1010 to 1111 | 0000000           |

Uploaded By: Malak Dar Obaid © Ahmed Shawahna - slide 20

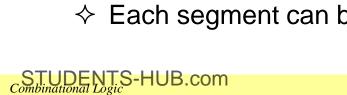

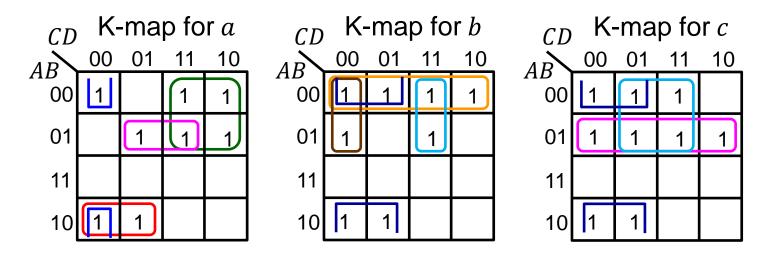

#### 3. Logic Minimization Using K-Maps:

a = A'C + A'BD + AB'C' + B'C'D' b = A'B' + B'C' + A'C'D' + A'CDc = A'B + B'C' + A'D

Extracting common terms

Combinational Logic

Let

$$T_1 = A'B$$

,  $T_2 = B'C'$ ,  $T_3 = A'D$

Optimized Logic Expressions  $a = A'C + T_1 D + T_2 A + T_2 D'$   $b = A'B' + T_2 + A'C'D' + T_3C$   $c = T_1 + T_2 + T_3$  $T_1, T_2, T_3$  are shared gates

#### 3. Logic Minimization Using K-Maps

STUDENTS-HUB.com

#### 4. Technology Mapping:

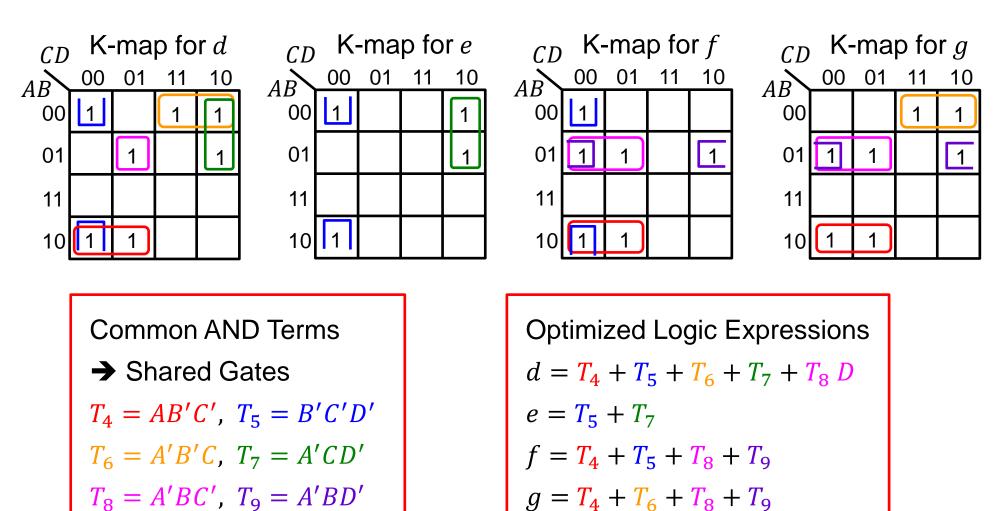

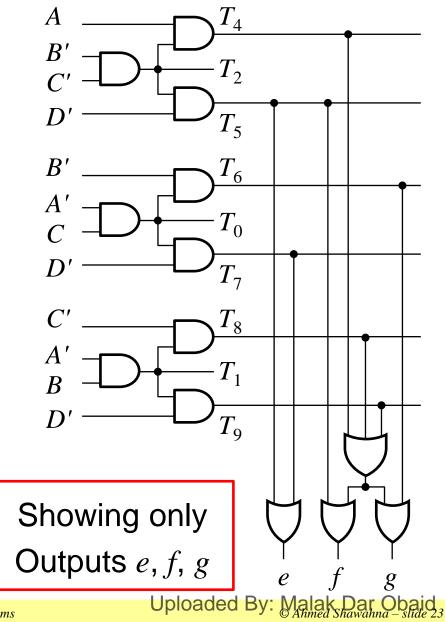

Many Common AND terms:  $T_0$  thru  $T_9$  $T_0 = A'C, T_1 = A'B, T_2 = B'C'$  $T_3 = A'D, T_4 = AB'C', T_5 = B'C'D'$  $T_6 = A'B'C$ ,  $T_7 = A'CD'$  $T_8 = A'BC', T_9 = A'BD'$ **Optimized Logic Expressions**  $a = T_0 + T_1 D + T_4 + T_5$  $b = A'B' + T_2 + A'C'D' + T_3C$  $c = T_1 + T_2 + T_3$  $d = T_4 + T_5 + T_6 + T_7 + T_8 D$  $e = T_{5} + T_{7}$  $f = T_4 + T_5 + T_8 + T_9$  $g = T_4 + T_6 + T_8 + T_9$

Combinational Logic

ENCS2340 – Digital Systems

#### 5. Verification:

Run the simulation of the circuit. All sixteen input test cases of A, B, C, D are generated between t=0 and t=160ns. Verify that outputs a to g match the truth table.

### Next . . .

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- ♦ Half Adder and Full Adder

- Sinary Adder (Ripple Carry Adder and Carry Lookahead Adder)

- ♦ Incrementor

- ♦ Binary Subtractor

- ♦ Adder/Subtractor Design Examples

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

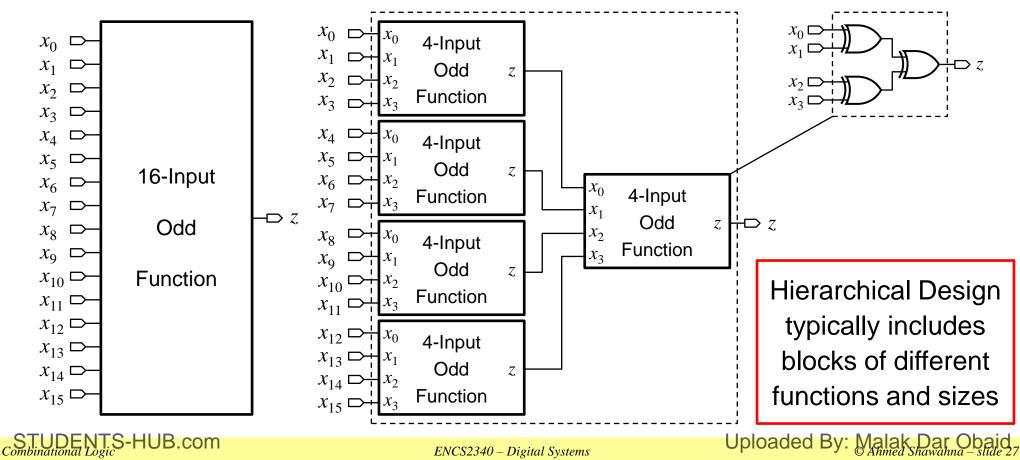

# Hierarchical Design

Why Hierarchical Design?

To simplify the implementation of a complex circuit

What is Hierarchical Design?

Decompose a complex circuit into smaller pieces called blocks

Decompose each block into even smaller blocks

Repeat as necessary until the blocks are small enough

Any block not decomposed is called a primitive block

The hierarchy is a tree of blocks at different levels

- The blocks are verified and well-document

- They are placed in a library for future use

# Example of Hierarchical Design

Top Level: 16-input odd function: 16 inputs, one output

♦ Implemented using Five 4-input odd functions

Second Level: 4-input odd function that uses three XOR gates

ENCS2340 – Digital Systems

# Testing Hierarchical Design

- Exhaustive testing can be very time consuming (or impossible)

- $\Rightarrow$  For a 16-bit input, there are  $2^{16} = 65,536$  test cases (combinations)

- $\diamond$  For a 32-bit input, there are  $2^{32} = 4,294,967,296$  test cases

- $\Rightarrow$  For a 64-bit input, there are  $2^{64} = 18,446,744,073,709,551,616$  test cases!

- Testing a hierarchical design requires a different strategy

- Test each block in the hierarchy separately

- $\diamond$  For smaller blocks, exhaustive testing can be done

- ♦ It is easier to detect errors in smaller blocks before testing complete circuit

- Test the top-level design by applying selected test inputs

- Make sure that the test inputs exercise all parts of the circuit

### Top-Down versus Bottom-Up Design

- A top-down design proceeds from a high-level specification to a more and more detailed design by decomposition and successive refinement

- A bottom-up design starts with detailed primitive blocks and combines them into larger and more complex functional blocks

- Design usually proceeds top-down to a known set of building blocks, ranging from complete processors to primitive logic gates

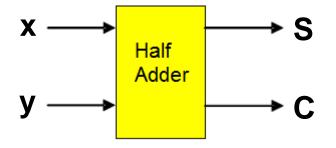

### Half Adder

X

- ✤ Half-adder adds <u>2 bits</u>: x and y

- Two output bits:

- 1. Carry bit: C

+ y

2. Sum bit: S

C S

- Sum bit is 1 if the number of 1's in the input is odd (odd function)

- $S = x'y + xy' = x \oplus y$

- Carry bit is 1 only when both inputs are 1

$$C = x y$$

Combinational Logic

**Truth Table**

| X | у | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

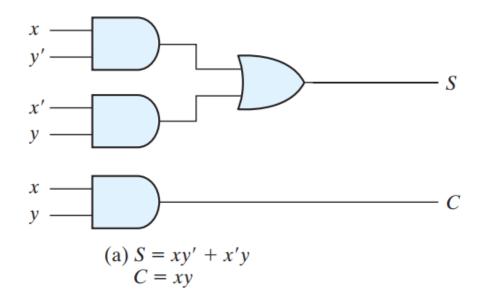

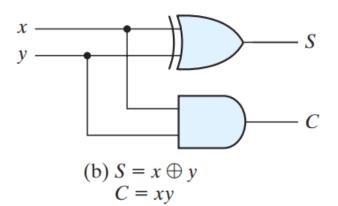

### Half Adder

The logic diagram of the half adder implemented in sum-ofproducts is shown in (a). It can be also implemented with an exclusive-OR and an AND gate as shown in (b):

Combinational Logic

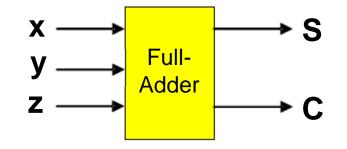

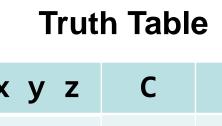

# Full Adder

- ✤ Full adder adds <u>3 bits</u>: x, y, and z

- Two output bits:

- 1. Carry bit: C

- 2. Sum bit: **s**

- Sum bit is 1 if the number of 1's in the input is odd (odd function) S = xy'z' + x'yz' + x'y'z + xyz

- Carry bit is 1 if the number of 1's in the input is 2 or 3

- C = xy + xz + yz

Combinational Logic

| хуг | C | S |

|-----|---|---|

| 000 | 0 | 0 |

| 001 | 0 | 1 |

| 010 | 0 | 1 |

| 011 | 1 | 0 |

| 100 | 0 | 1 |

| 101 | 1 | 0 |

| 110 | 1 | 0 |

| 111 | 1 | 1 |

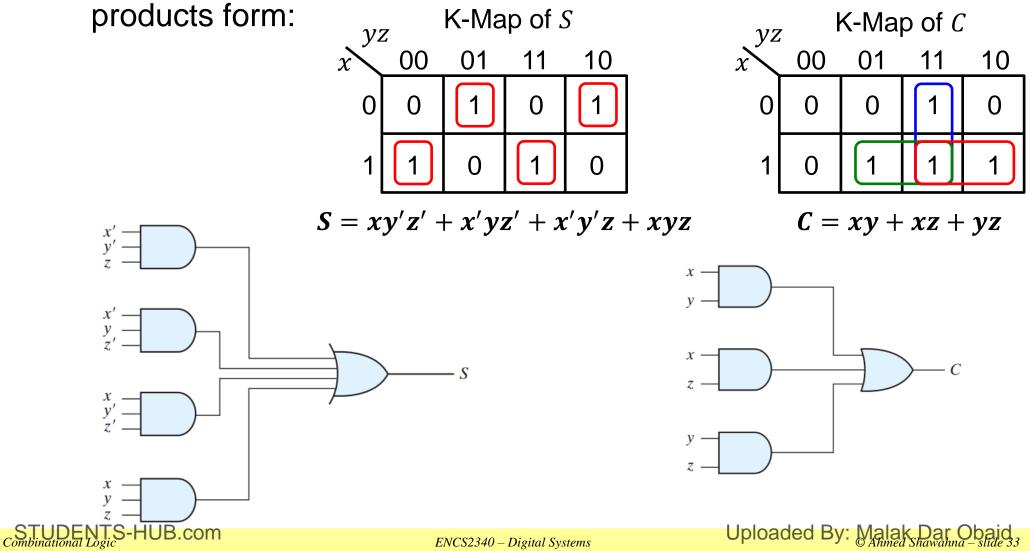

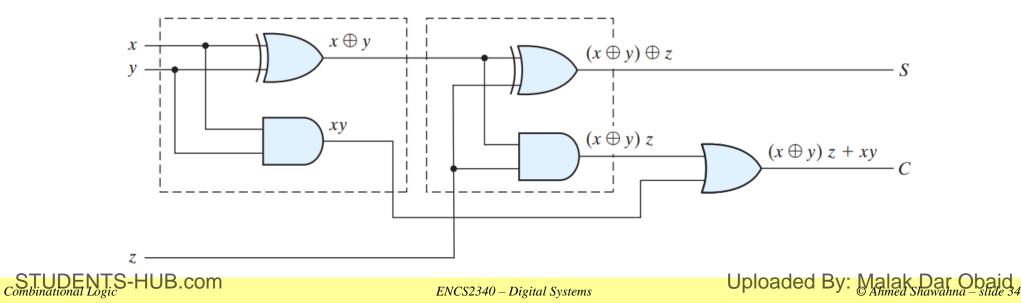

### Full Adder

The logic diagram for the full adder implemented in sum-of-

### Full Adder

Full adder can also be implemented with two half adders and one OR gate:

$$S = xy'z' + x'yz' + x'y'z + xyz \qquad C = xy + xz + yz$$

=  $z'(xy' + x'y) + z(x'y' + xy) \qquad = xy + (x \oplus y)z$

=  $z'(x \oplus y) + z(x \oplus y)'$

$$= x \oplus y \oplus z = (x \oplus y) \oplus z$$

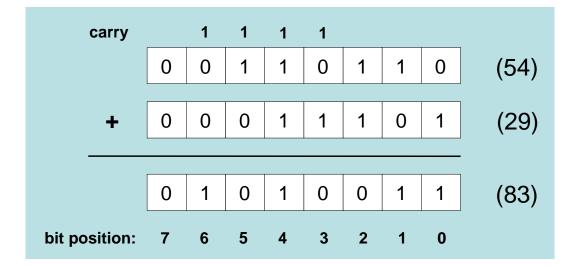

# Binary Adder (Ripple Carry Adder)

Start with the least significant bit (rightmost bit)

- ✤ Add each pair of bits

- Include the carry in the addition

### Iterative Design: Ripple Carry Adder

- Using identical copies of a smaller circuit to build a large circuit

- ✤ Addition of *n*-bit numbers requires:

- $\diamond$  A chain of *n* full adders, or

- $\diamond$  A chain of one-half adder and (n 1) full adders

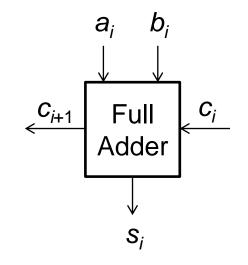

- Example: Building a 4-bit adder using 4 copies of a full adder

- $\diamond$  The **cell** (iterative block) is a **full adder**

- Adds 3 bits: *a<sub>i</sub>*, *b<sub>i</sub>*, *c<sub>i</sub>*

Combinational Logic

Computes: Sum s<sub>i</sub> and Carry-out c<sub>i+1</sub>

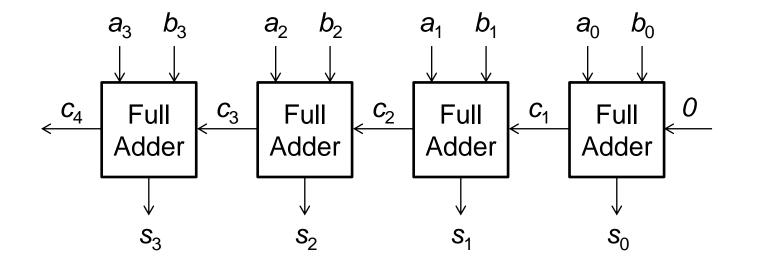

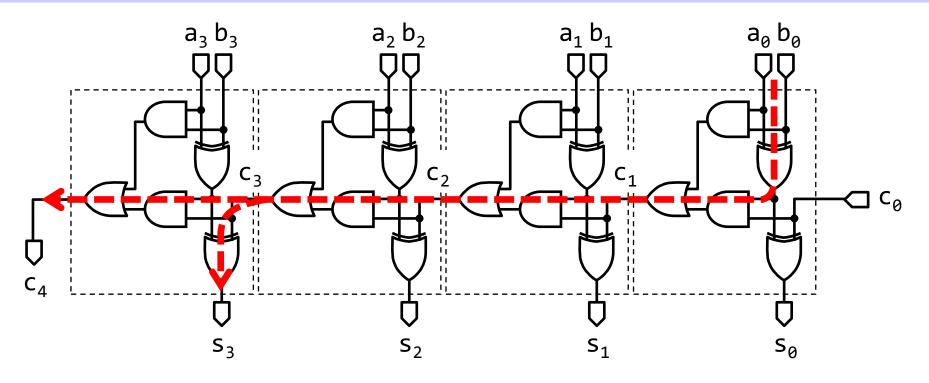

## Iterative Design: Ripple Carry Adder

- The Figure below shows the interconnection of four full-adder (FA) circuits to provide a four-bit binary ripple carry adder

- $\diamond$  Carry-out of cell *i* becomes carry-in to cell (*i*+1)

- $\diamond$  The input carry to the least significant position is fixed at 0

# Carry Propagation

Major drawback of ripple-carry adder is the carry propagation

- The carries are connected in a chain through the full adders

- The carry ripples (propagates) through all the full adders

- This is why it is called a ripple-carry adder

STUDENTS-HUB.com

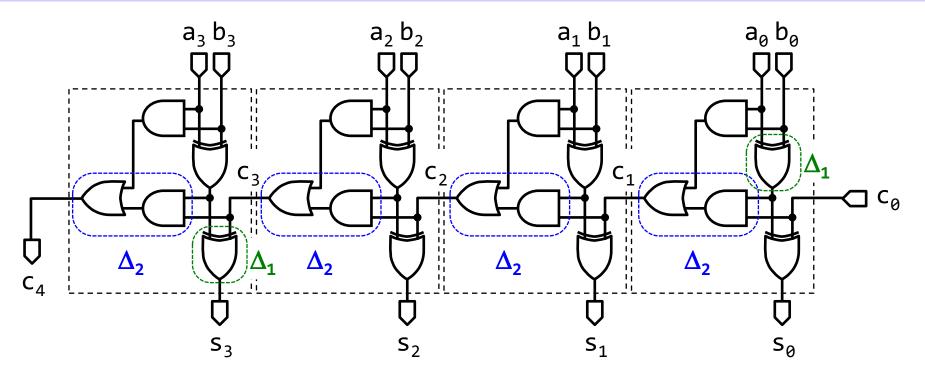

# Longest Delay Analysis

- Suppose the **XOR** delay is  $\Delta_1$  (Delay of XOR > Delay of AND) and **AND-OR** delay is  $\Delta_2$

- ✤ For an *N*-bit ripple-carry adder, if all inputs are present at once:

- 1. Most-significant sum-bit delay =  $2\Delta_1 + (N-1)\Delta_2$

- 2. Final Carry-out delay =  $\Delta_1 + N \Delta_2$

STUDENTS-HUB.com

Uploaded By: Malak Dar Obaid, O Ahmed Shawahna - slide 39

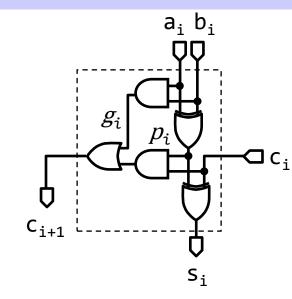

# Carry Lookahead Adder

- Is it possible to eliminate carry propagation?

- ↔ Observation:  $c_{i+1} = a_i b_i + (a_i \oplus b_i) c_i$

- ✤ If both inputs  $a_i$  and  $b_i$  are 1s then  $c_{i+1}$  will be 1 regardless of input  $c_i$

- ✤ Therefore, define  $g_i = a_i b_i$

UDENTS-HUB.com

$\diamond g_i$  is called **carry generate**: generates  $c_{i+1}$  regardless of  $c_i$

- ✤ In addition, define  $p_i = (a_i \oplus b_i)$ a<sub>i</sub> or  $b_i$  is 1, not both

♦  $p_i$  is called carry propagate: propagates value of  $c_i$  to  $c_{i+1}$

- Equation of output sum carry becomes:

$s_i = p_i \oplus c_i$  and  $c_{i+1} = g_i + p_i c_i$

♦ If both inputs  $a_i$  and  $b_i$  are 0s then  $g_i = p_i = 0$  and  $c_{i+1} = 0$

# Carry Bits

Carry bits are generated by a Lookahead Carry Unit as follows:  $c_0 = input carry$

$c_1 = g_0 + p_0 c_0$

$c_2 = g_1 + p_1 c_1 = g_1 + p_1 (g_0 + p_0 c_0) = g_1 + p_1 g_0 + p_1 p_0 c_0$

$c_3 = g_2 + p_2 c_2 = g_2 + p_2 g_1 + p_2 p_1 g_0 + p_2 p_1 p_0 c_0$

$c_4 = g_3 + p_3 c_3 = g_3 + p_3 g_2 + p_3 p_2 g_1 + p_3 p_2 p_1 g_0 + p_3 p_2 p_1 p_0 c_0$

Define Group Generate:  $GG = g_3 + p_3 g_2 + p_3 p_2 g_1 + p_3 p_2 p_1 g_0$

Define Group Propagate:  $GP = p_3 p_2 p_1 p_0$

$c_4 = GG + GP c_0$

Carry does not ripple anymore

Reduced delay when generating  $c_1$  to  $c_4$  in parallel

STUDENTS-HUB.com

ENCS2340 – Digital Systems

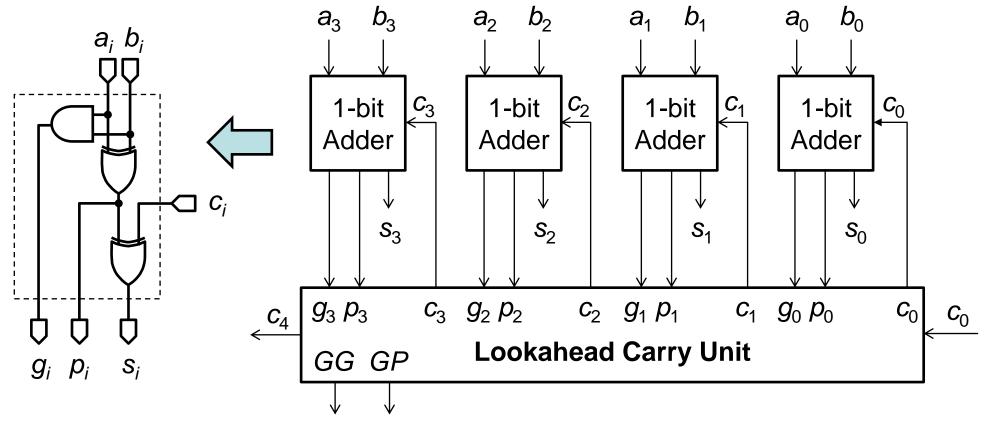

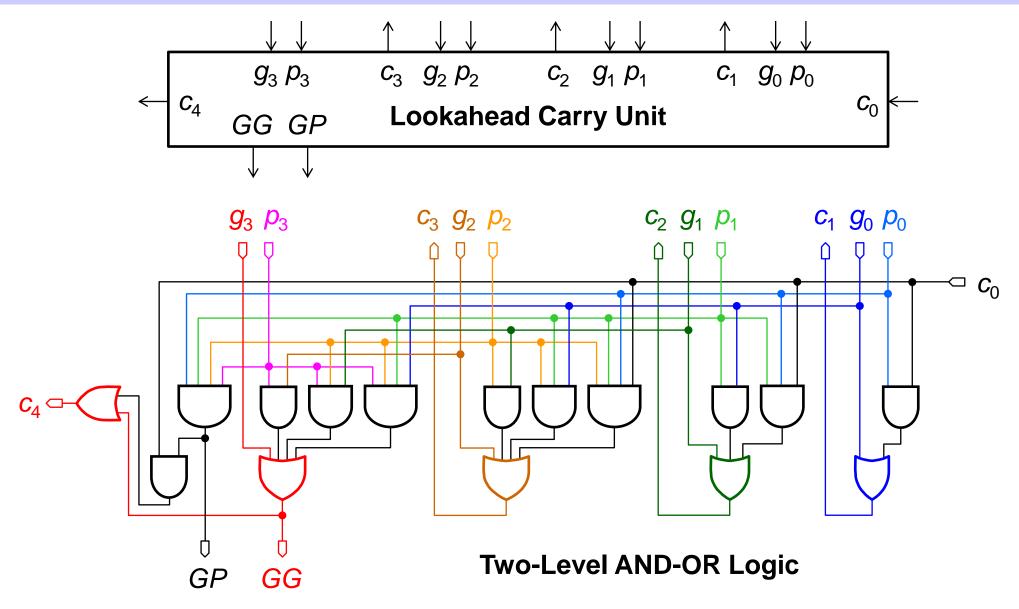

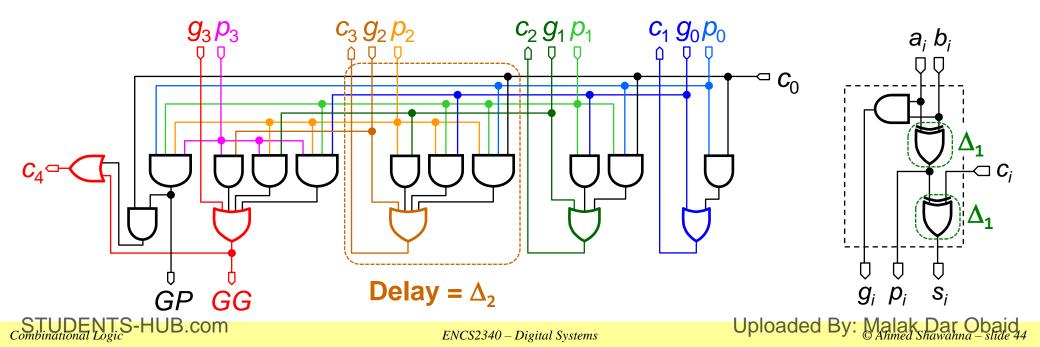

## 4-Bit Carry Lookahead Adder

All generate and propagate signals  $(g_i, p_i)$  are generated in parallel All carry bits  $(c_1 \text{ to } c_4)$  are generated in parallel

The sum bits are generated faster than ripple-carry adder

STUDENTS-HUB.com

#### Lookahead Carry Unit

STUDENTS-HUB.com

ENCS2340 – Digital Systems

Uploaded By: Malak Dar Obaid, © Ahmed Shawahna - slide 43

## Longest Delay of the 4-bit CLA

- ✤ All generate and propagate signals are produced in parallel

- ↔ Delay of all  $g_i$  and  $p_i = \Delta_1$  (Delay of XOR > Delay of AND)

- ♦ Carry bits  $c_1$ ,  $c_2$ , and  $c_3$  are generated in parallel (Delay =  $\Delta_2$ )

$\diamond$  Carry-out bit  $c_4$  is not needed to compute the sum bits

♣ Longest Delay of the 4-bit CLA =  $\Delta_1 + \Delta_2 + \Delta_1 = 2 \Delta_1 + \Delta_2$

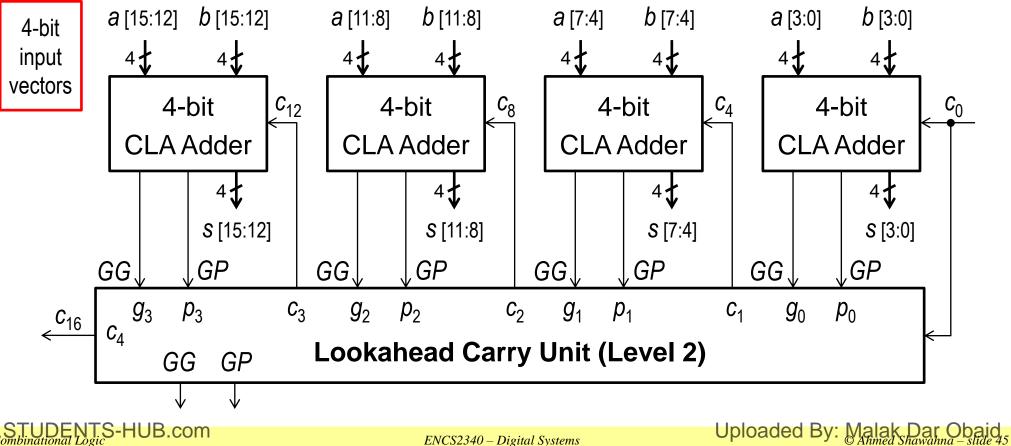

## Hierarchical 16-Bit Carry Lookahead Adder

- Designed with Four 4-bit Carry Lookahead Adders (CLA)

- A Second-Level Lookahead Carry Unit is required

- Uses Group Generate (GG) and Group Propagate (GP) signals

Combinational Logic

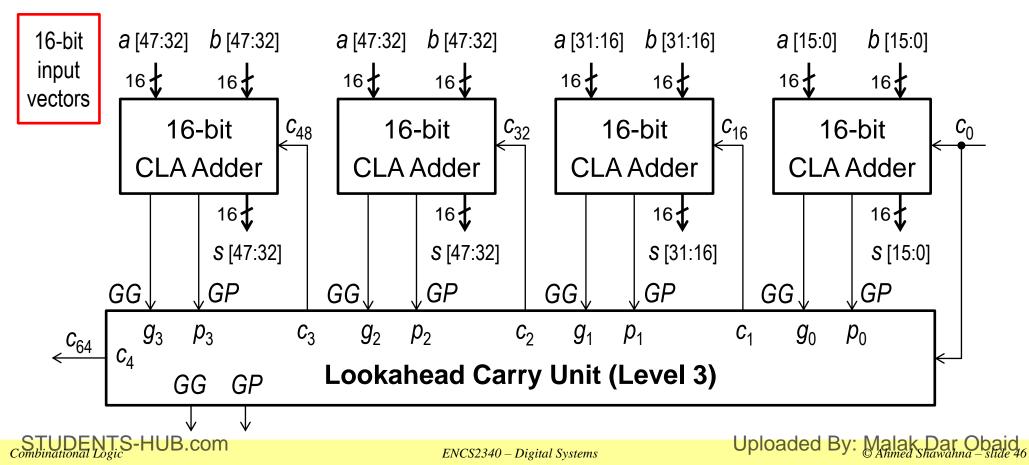

# Hierarchical 64-Bit Carry Lookahead Adder

- Designed with Four 16-bit Carry Lookahead Adders (CLA)

- A Third-Level Lookahead Carry Unit is required

- Uses Group Generate (GG) and Group Propagate (GP) signals

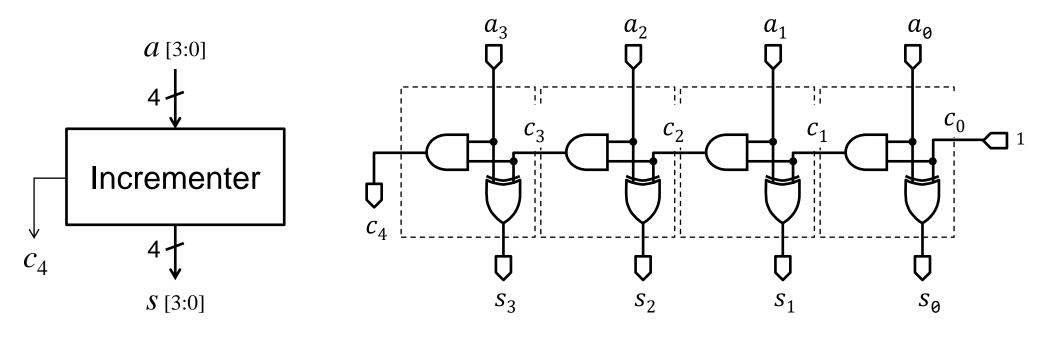

#### **Incrementor Circuit**

An incrementer is a special case of an adder

Sum = A + 1 (B = 0,  $C_0 = 1$ )

✤ An *n*-bit Adder can be simplified into an *n*-bit Incrementer

STUDENTS-HUB.com

ENCS2340 – Digital Systems

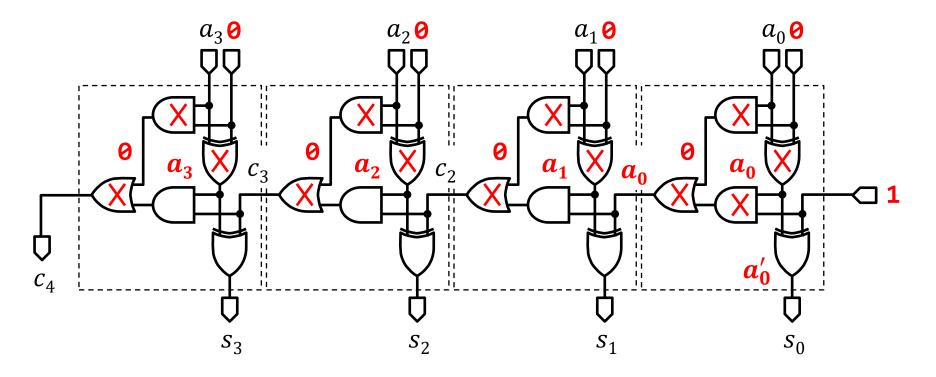

# Design by Contraction

- Contraction is a technique for simplifying the logic

- Applying 0s and 1s to some inputs

- Equations are simplified after applying fixed 0 and 1 inputs

- Converting a function block to a more simplified function

- Examples of Design by Contraction

- ♦ Incrementing a number by a fixed constant

- $\diamond\,$  Comparing a number to a fixed constant

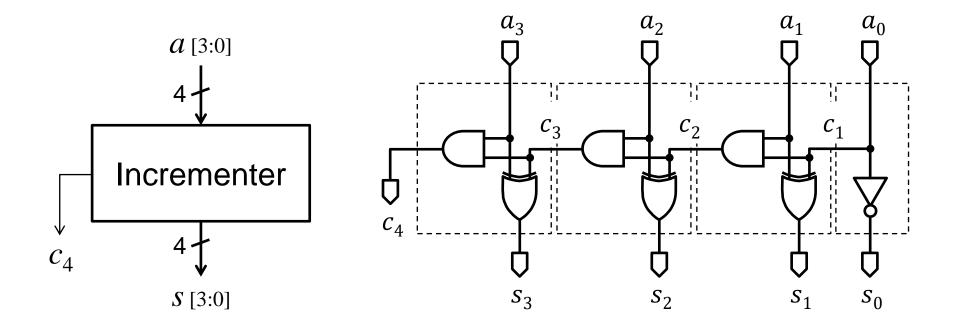

# Simplifying the Incrementer Circuit

- Many gates were eliminated

- No longer needed when an input is a constant

- ✤ Last cell can be replicated to implemented an *n*-bit incrementer

## Simplifying the Incrementer Circuit

First half adder can be simplified and replaced with an inverter

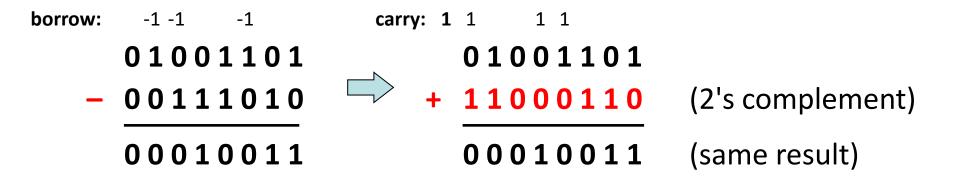

# **Binary Subtractor**

✤ When computing A – B, convert B to its 2's complement

A – B = A + (2's complement of B)

Same adder is used for both addition and subtraction

This is the biggest advantage of 2's complement

Final carry is ignored, because

A + (2's complement of B) = A +  $(2^n - B) = (A - B) + 2^n$

Final carry =  $2^n$ , for *n*-bit numbers

STUDENTS-HUB.com

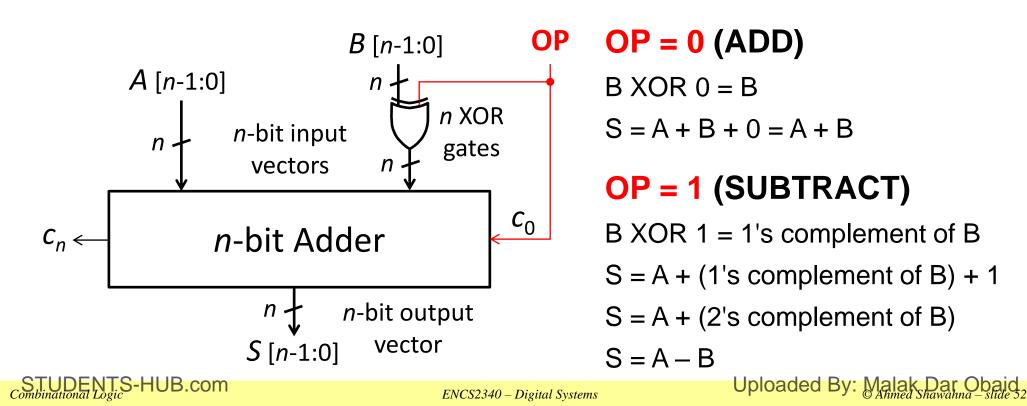

## Adder/Subtractor for 2's Complement

- Same adder is used to compute: (A + B) or (A B)

- ✤ Subtraction (A B) is computed as: A + (2's complement of B)

2's complement of B = (1's complement of B) + 1

Two operations: OP = 0 (ADD), OP = 1 (SUBTRACT)

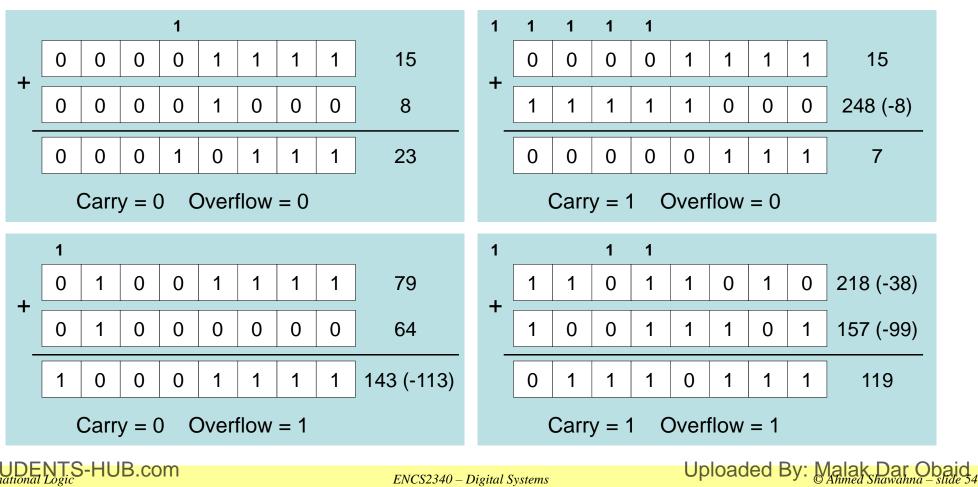

## Carry versus Overflow

- ✤ Carry is important when …

- Adding unsigned integers

- ♦ Indicates that the unsigned sum is out of range

- ♦ Sum > maximum unsigned *n*-bit value

- ✤ Overflow is important when …

- Adding or subtracting signed integers

- ♦ Indicates that the signed sum is out of range

- ✤ Overflow occurs when …

- $\diamond\,$  Adding two positive numbers and the sum is negative

- $\diamond$  Adding two negative numbers and the sum is positive

- ↔ Simplest way to detect Overflow:  $V = C_{n-1} \oplus C_n$

## Carry and Overflow Examples

- We can have carry without overflow and vice-versa

- Four cases are possible (Examples on 8-bit numbers)

STUDENTS-HUB.com

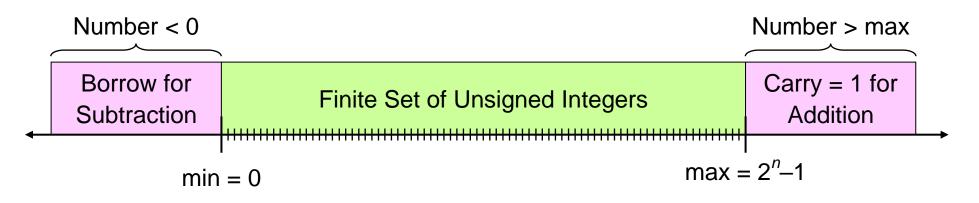

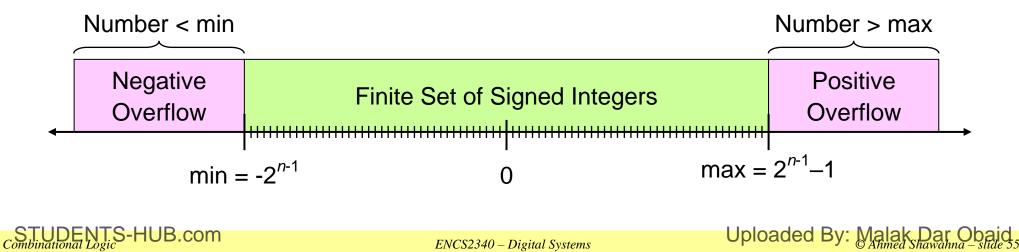

# Range, Carry, Borrow, and Overflow

#### Unsigned Integers: n-bit representation

#### Signed Integers: 2's complement representation

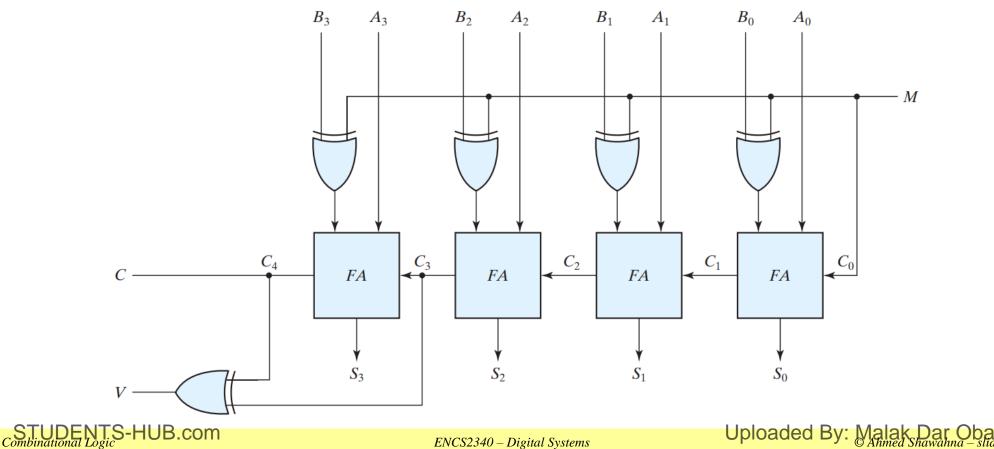

# **Binary Adder/Subtractor**

Example: A 4-bit adder/subtractor with carry/overflow detection

$\diamond$  Two operations: M = 0 (S = A + B), M = 1 (S = A - B)

$\diamond$  The C bit detects a carry after addition or a borrow after subtraction

$\diamond$  The V bit detects an overflow

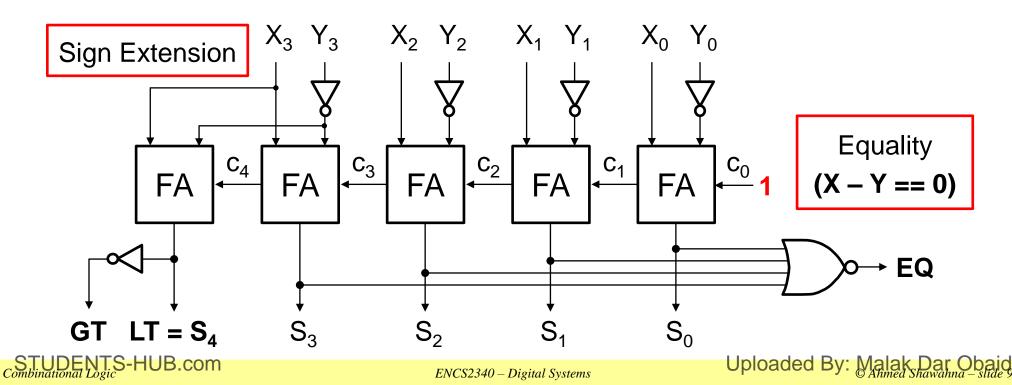

#### Zero versus Sign Extension

- Unsigned Integers are Zero-Extended

- Signed Integers are Sign-Extended

- ♦ Given that X is a 4-bit **unsigned** integer  $\rightarrow$  Range = 0 to 15

- ♦ Given that Y is a 4-bit **signed** integer  $\rightarrow$  Range = -8 to +7

- ✤ If unsigned X = 4'b1101 (binary), then X = 13 (decimal)

- ✤ If signed Y = 4'b1101 (binary), then Y = -3 (decimal)

- ✤ If X is zero-extended from 4 to 6 bits then X = 6'b001101 = 13

- If Y is sign-extended from 4 to 6 bits then Y = 6'b111101 = -3

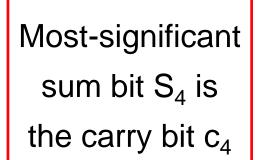

#### Unsigned Addition S = X + Y

- Design a circuit that computes: S = X + Y (unsigned X and Y)

- ✤ X[3:0] and Y[3:0] are 4-bit unsigned integers → Range = 0 to 15

#### **Solution:**

Combinational Logic

♦ Maximum S = 15 + 15 = 30 → unsigned S must be **5 bits**

Uploaded By: Malak Dar Obaid

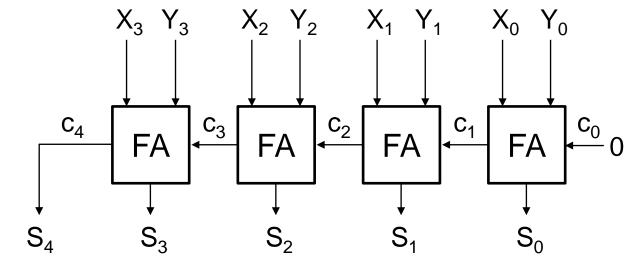

#### Signed Addition S = X + Y

- Design a circuit that computes: S = X + Y (signed X and Y)

- ❖ X[3:0] and Y[3:0] are 4-bit signed integers → Range = -8 to +7

Solution:

- ✤ Minimum S = (-8) + (-8) = -16, Maximum S = (+7) + (+7) = + 14

- ♦ Therefore, signed range of S = -16 to +14  $\rightarrow$  S must be **5 bits**

Uploaded By: Malak Dar Obaid Chimed Shawahna - slide 39

Combinational Logic

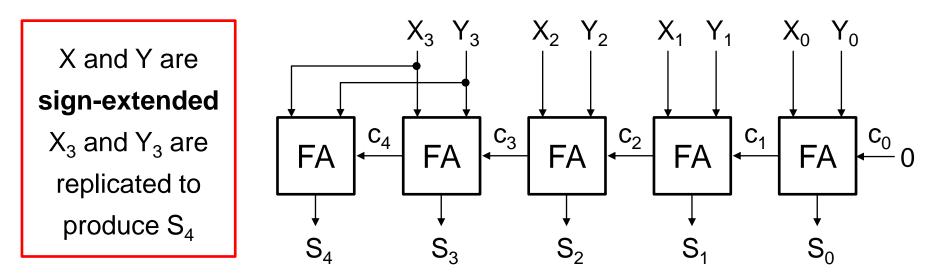

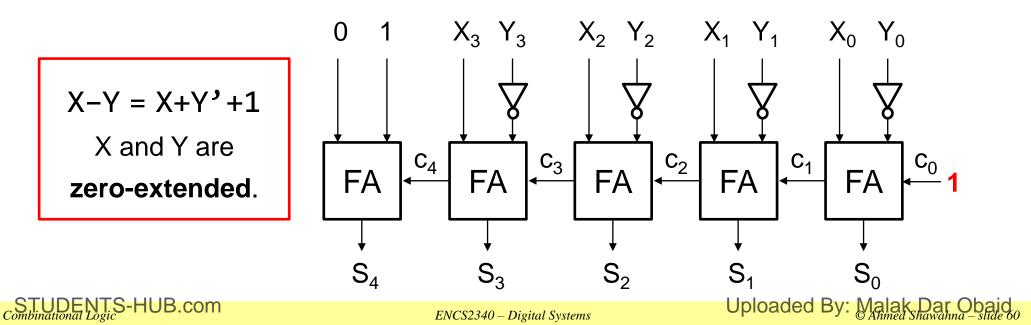

#### Unsigned Subtraction S = X - Y

- ✤ Design a circuit that computes S = X Y (unsigned X and Y)

- ♦ X[3:0] and Y[3:0] are 4-bit **unsigned** integers  $\rightarrow$  Range = 0 to 15

Solution: S = X - Y = X + 2's complement of Y = X + Y' + 1

- ✤ Minimum S = 0 15 = -15, Maximum S = 15 0 = +15

- ✤ S is signed, even though X are Y are unsigned → S is 5 bits

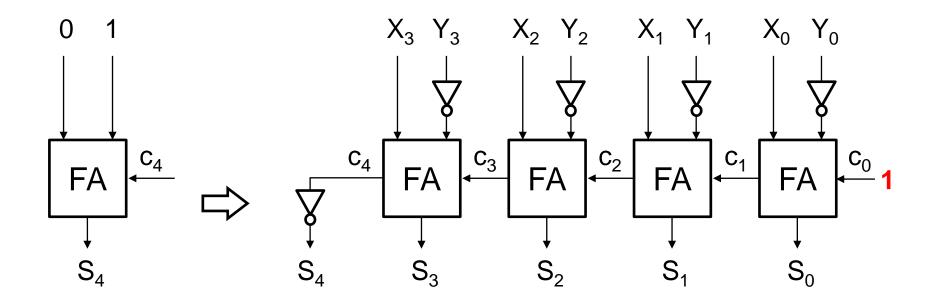

#### Unsigned Subtraction S = X - Y

- ↔ Most-significant bit:  $S_4 = 0 + 0' + c_4 = 1 + c_4 = c_4'$

- Full Adder for  $S_4$  can be replaced by an **inverter**

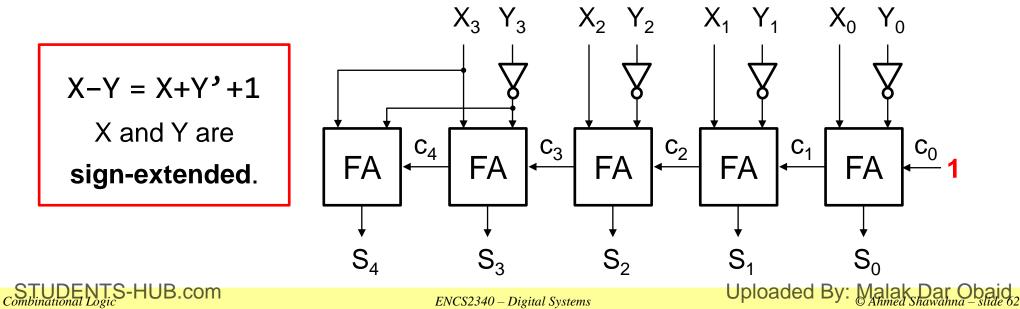

#### Signed Subtraction S = X - Y

- Design a circuit that computes S = X Y (signed X and Y)

- X[3:0] and Y[3:0] are 4-bit **signed** integers  $\rightarrow$  Range = -8 to +7

Solution: S = X - Y = X + Y' + 1

- ✤ Minimum S = -8 (+7) = -15, Maximum S = +7 (-8) = +15

- Signed range for S is -15 to +15  $\rightarrow$  S is 5 bits

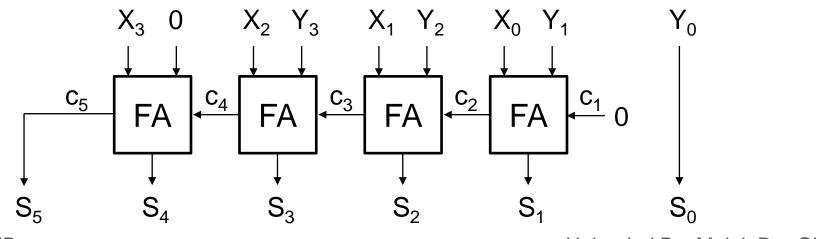

# S = 2\*X + Y (Unsigned X and Y)

- Design a circuit that computes S = 2\*X + Y (unsigned X and Y)

- ❖ X[3:0] and Y[3:0] are 4-bit unsigned integers → range = 0 to 15

Solution:

- ♦ Maximum value of  $S = 2*15 + 15 = 45 \rightarrow S$  is 6 bits = S[5:0]

STUDENTS-HUB.com

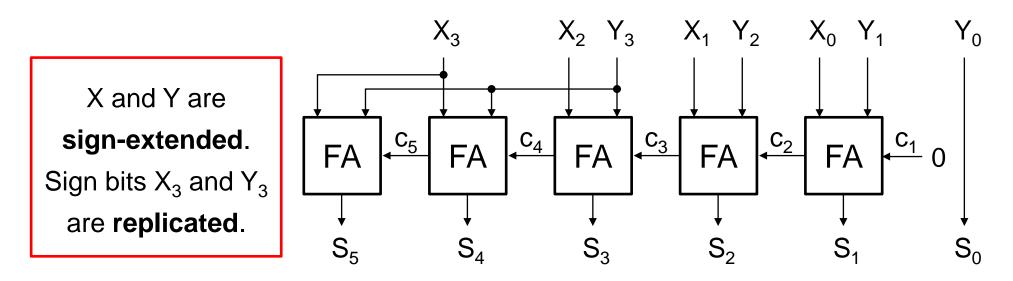

# S = 2\*X + Y (Signed X and Y)

- ✤ Design a circuit that computes S = 2\*X + Y using Full Adders

- ♦ X[3:0] and Y[3:0] are 4-bit **signed** integers → range = -8 to +7

#### Solution:

- ♣ Range of X and Y is -8 to +7 Minimum S =  $2^{*}(-8) + (-8) = -24$

- ♦ Maximum  $S = 2^{*}(+7) + 7 = +21 \rightarrow S$  is **6 bits** = S[5:0]

STUDENTS-HUB.com

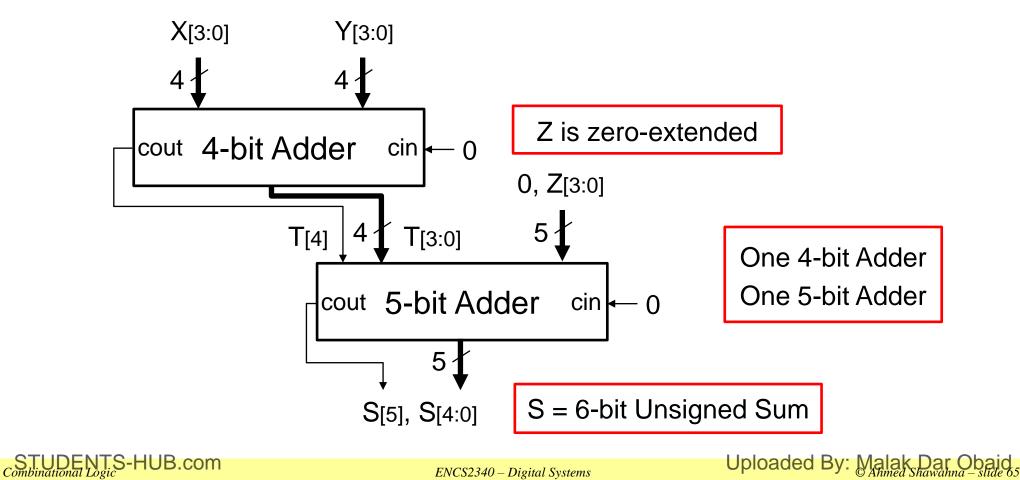

## Design a Circuit for Unsigned S = X + Y + Z

$\bigstar$  X, Y, and Z are 4-bit **unsigned** integers  $\rightarrow$  Range = 0 to 15

Solution: Maximum S =  $15 + 15 + 15 = 45 \rightarrow S$  must be 6 bits

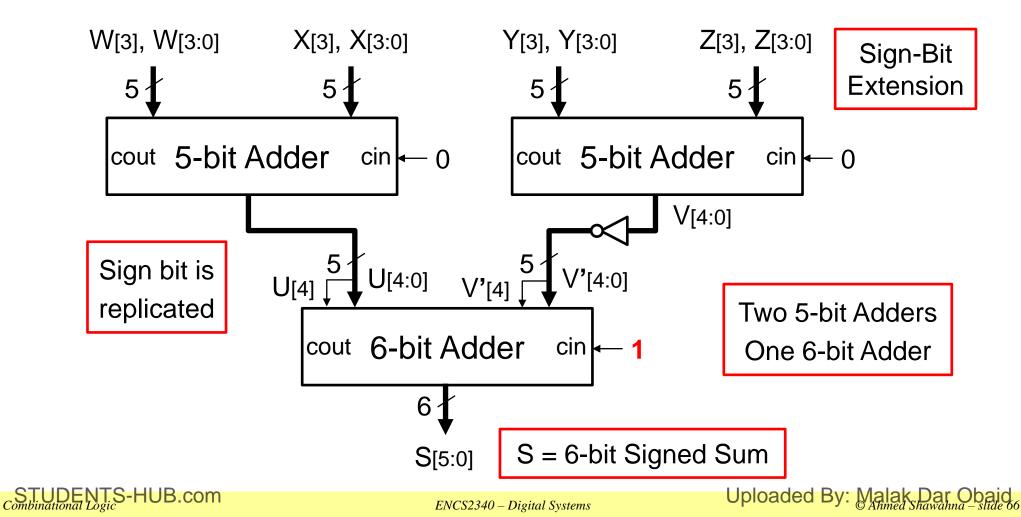

## Design a Circuit for Signed S = W + X - Y - Z

❖ W, X, Y, and Z are 4-bit signed integers → Range = -8 to +7

Solution: S = W + X - Y - Z = (W+X) - (Y+Z) → 6 bits are used

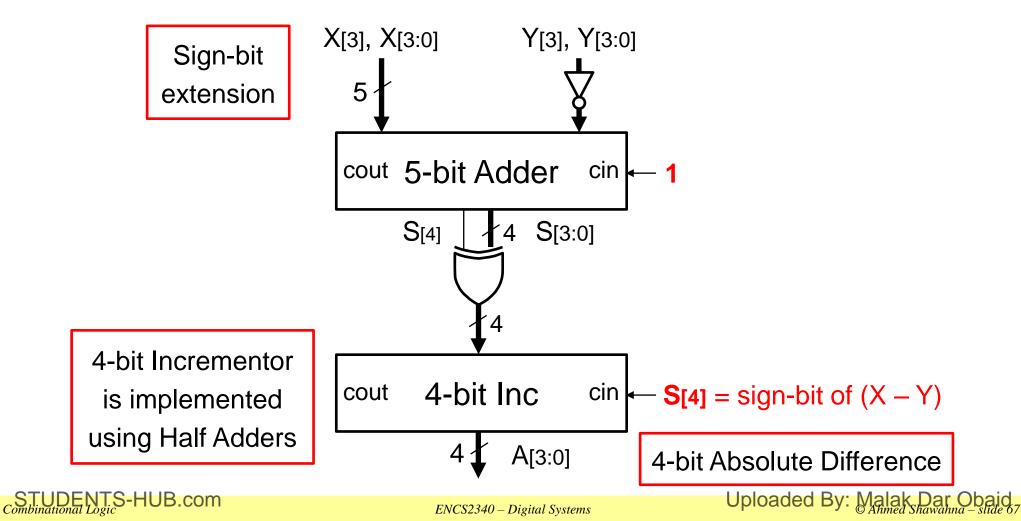

# Absolute Difference |X - Y| of Signed X, Y

• Design a circuit that computes A = |X - Y| (absolute difference)

**Solution:** Maximum  $A = |X - Y| = |-8 - +7| = 15 \rightarrow 4$  bits are used

## Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

BCD Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

STUDENTS-HUB.com

## **BCD** Addition

- Consider adding two decimal digits in BCD

- Operands and Result: 0 to 9

- Output sum cannot exceed 9 + 9 + 1 = 19

$\diamond$  The 1 in the sum is the input carry from previous digit

We use a 4-bit binary adder to add the BCD digits

$\diamond$  The adder will produce a result that ranges from 0 through 19 ♦ If the result is more than 9, it must be corrected to use 2 digits  $\Rightarrow$  To correct the digit, add 6 to the digit sum (a 4-bit binary adder)

|                 |   | 1000 |         |                       | 8   |                          |

|-----------------|---|------|---------|-----------------------|-----|--------------------------|

|                 | + | 0101 |         |                       | + 5 |                          |

|                 |   | 1101 |         |                       | 13  | (>9)                     |

|                 | Ŧ | 0110 |         |                       | + 6 | (add 6)                  |

|                 | 1 | 0011 | Final a |                       | 19  | (carry + 3)              |

| TUDENTS-HUB.com | ) |      | ENCS2   | 2340 – Digital Systen | ns  | Uploaded By: Malak Dar O |

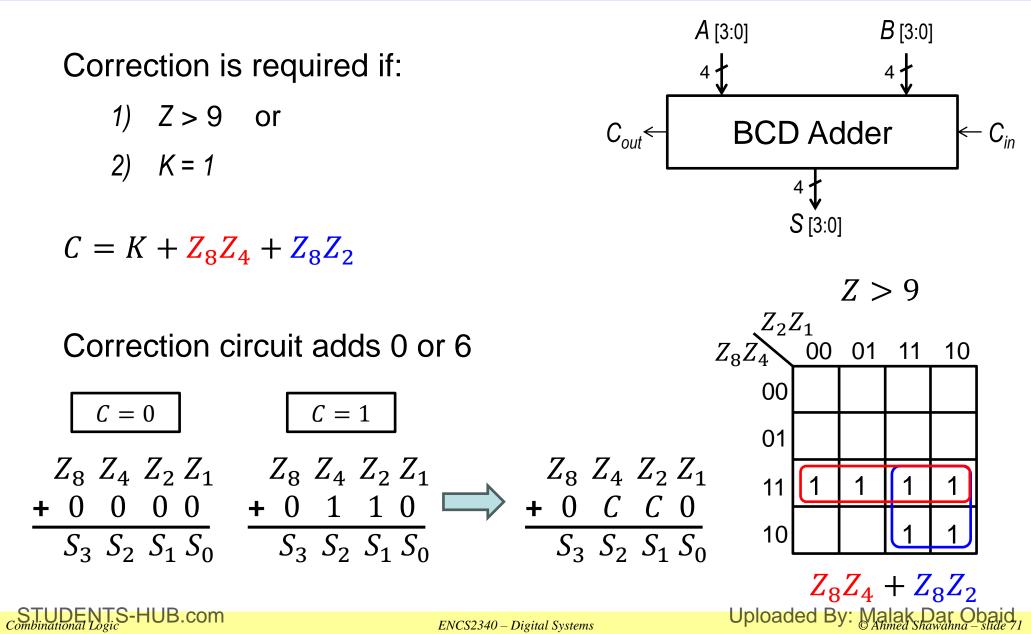

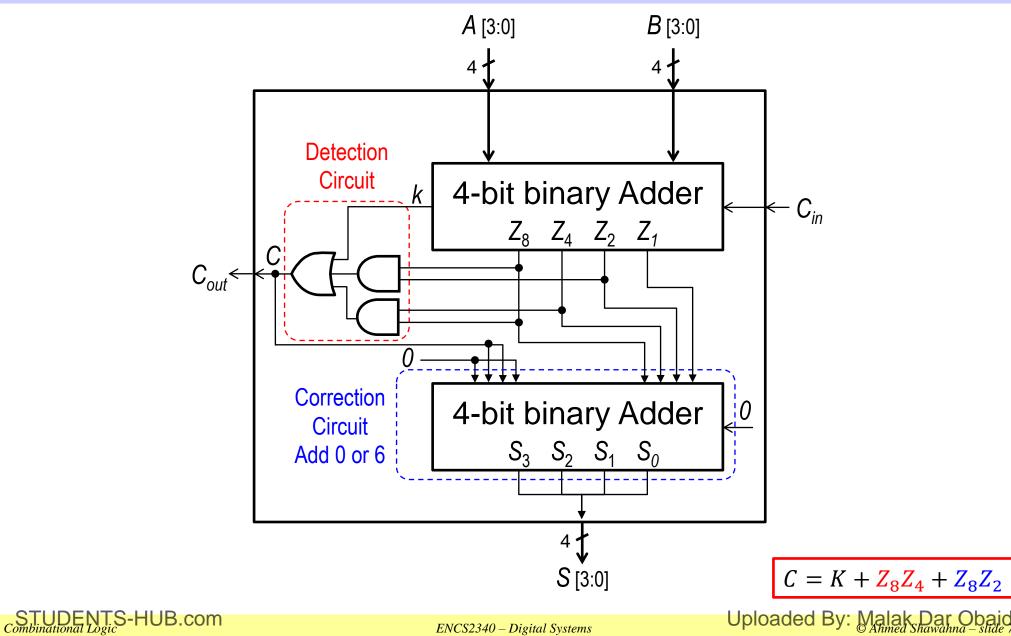

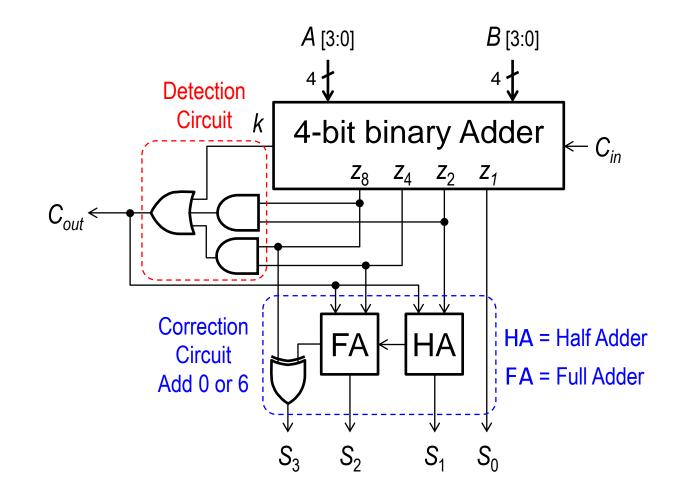

#### **BCD** Adder

|                                    |   | Bin        | ary S      | um             |            |    |   | B          | Decimal    |                |            |    |

|------------------------------------|---|------------|------------|----------------|------------|----|---|------------|------------|----------------|------------|----|

|                                    | K | <b>Z</b> 8 | <b>Z</b> 4 | Z <sub>2</sub> | <b>Z</b> 1 | _  | С | <b>S</b> 8 | <b>S</b> 4 | S <sub>2</sub> | <b>S</b> 1 |    |

|                                    | 0 | 0          | 0          | 0              | 0          |    | 0 | 0          | 0          | 0              | 0          | 0  |

|                                    | 0 | 0          | 0          | 0              | 1          |    | 0 | 0          | 0          | 0              | 1          | 1  |

| Valid Codes                        | 0 | 0          | 0          | 1              | 0          |    | 0 | 0          | 0          | 1              | 0          | 2  |

| p                                  | 0 | 0          | 0          | 1              | 1          | +0 | 0 | 0          | 0          | 1              | 1          | 3  |

| $\tilde{\mathbf{O}}$               | 0 | 0          | 1          | 0              | 0          |    | 0 | 0          | 1          | 0              | 0          | 4  |

|                                    | 0 | 0          | 1          | 0              | 1          |    | 0 | 0          | 1          | 0              | 1          | 5  |

|                                    | 0 | 0          | 1          | 1              | 0          |    | 0 | 0          | 1          | 1              | 0          | 6  |

| $\sim$                             | 0 | 0          | 1          | 1              | 1          |    | 0 | 0          | 1          | 1              | 1          | 7  |

|                                    | 0 | 1          | 0          | 0              | 0          |    | 0 | 1          | 0          | 0              | 0          | 8  |

|                                    | 0 | 1          | 0          | 0              | 1          |    | 0 | 1          | 0          | 0              | 1          | 9  |

|                                    | 0 | 1          | 0          | 1              | 0          |    | 1 | 0          | 0          | 0              | 0          | 10 |

| s D                                | 0 | 1          | 0          | 1              | 1          |    | 1 | 0          | 0          | 0              | 1          | 11 |

| Cti Ce                             | 0 | 1          | 1          | 0              | 0          |    | 1 | 0          | 0          | 1              | 0          | 12 |

| õ õ                                | 0 | 1          | 1          | 0              | 1          | +6 | 1 | 0          | 0          | 1              | 1          | 13 |

| U E                                | 0 | 1          | 1          | 1              | 0          |    | 1 | 0          | 1          | 0              | 0          | 14 |

| D C                                | 0 | 1          | 1          | 1              | 1          |    | 1 | 0          | 1          | 0              | 1          | 15 |

|                                    | 1 | 0          | 0          | 0              | 0          |    | 1 | 0          | 1          | 1              | 0          | 16 |

| Invalid Codes<br>(need Correction) | 1 | 0          | 0          | 0              | 1          |    | 1 | 0          | 1          | 1              | 1          | 17 |

| ы<br>Б                             | 1 | 0          | 0          | 1              | 0          |    | 1 | 1          | 0          | 0              | 0          | 18 |

| L)                                 | 1 | 0          | 0          | 1              | 1          |    | 1 | 1          | 0          | 0              | 1          | 19 |

STUDENTS-HUB.com

Invalid Codes

Uploaded By: Malak Dar Obaid <sup>©</sup> Ahmed Shawahna - slide 70

#### **BCD** Adder

STUDENTS-HUB.com

#### **BCD** Adder

Uploaded By: Malak Dar Obaid

#### **BCD** Adder

STUDENTS-HUB.com

ENCS2340 – Digital Systems

Uploaded By: Malak Dar Obaid, C Ahmed Shawahna - slide 73

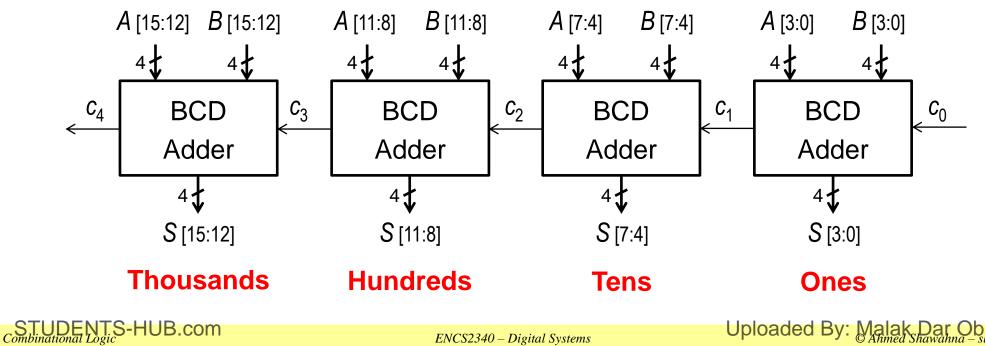

#### Multiple Digit BCD Addition

Add: 2905 + 1897 in BCD

Showing carries and digit corrections

|               | carry | +1   | +1    | +1   |      |

|---------------|-------|------|-------|------|------|

|               | ÷     | 0010 | 1001  | 0000 | 0101 |

|               | •     | 0001 | 1000  | 1001 | 0111 |

|               |       | 0100 | 10010 | 1010 | 1100 |

| digit correct | ion   |      | 0110  | 0110 | 0110 |

|               |       | 0100 | 1000  | 0000 | 0010 |

Final answer: 2905 + 1897 = 4802

## **Ripple-Carry BCD Adder**

Inputs are BCD digits: 0 to 9

- Sum are BCD digits: **ones**, **tens**, **hundreds**, **thousands**, etc.

- Can be extended to any number of BCD digits

- BCD adders are larger in size than binary adders

ENCS2340 – Digital Systems

### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

## **Binary Multiplication**

Binary Multiplication is simple:

| 0×0=0,                   | 0×1=0,  | 1×0=0,                       | 1×1=1                                                                            |

|--------------------------|---------|------------------------------|----------------------------------------------------------------------------------|

| Multiplica<br>Multiplier | nd<br>× | $1100_2 = 1$<br>$1101_2 = 1$ |                                                                                  |

|                          |         | 100                          | Binary multiplication<br>0 × multiplicand = 0<br>1 × multiplicand = multiplicand |

| Product                  | 100:    | 11100 <sub>2</sub> = 1       | .56                                                                              |

\* *n*-bit multiplicand × *m*-bit multiplier = (n + m)-bit product

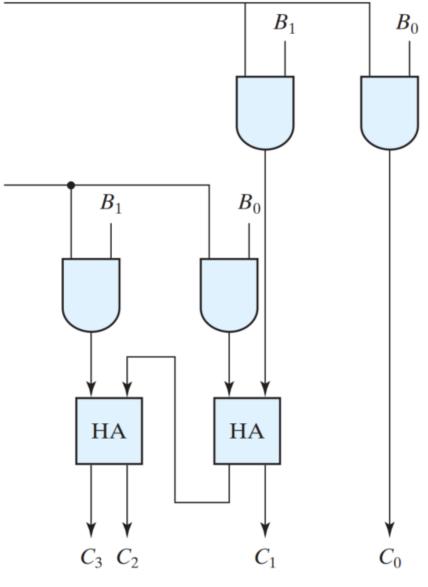

## 2-bit × 2-bit Binary Multiplier

$A_0$

- Suppose we want to multiply two numbers  $B = B_1 B_0$  and  $A = A_1 A_0$

- Step 1: AND (multiply) each bit of A with each bit of B  $\diamond$  Requires 2x2 AND gates and produces 2x2 product bits

- Step 2: Add the partial product  $\diamond$  Requires (2 - 1) 2-bit binary adders

$$\begin{array}{cccc} B_{1} & B_{0} \\ \\ A_{1} & A_{0} \\ \hline A_{0}B_{1} & A_{0}B_{0} \\ \\ \hline C_{3} & C_{2} & C_{1} & C_{0} \\ \end{array}$$

$C_3$

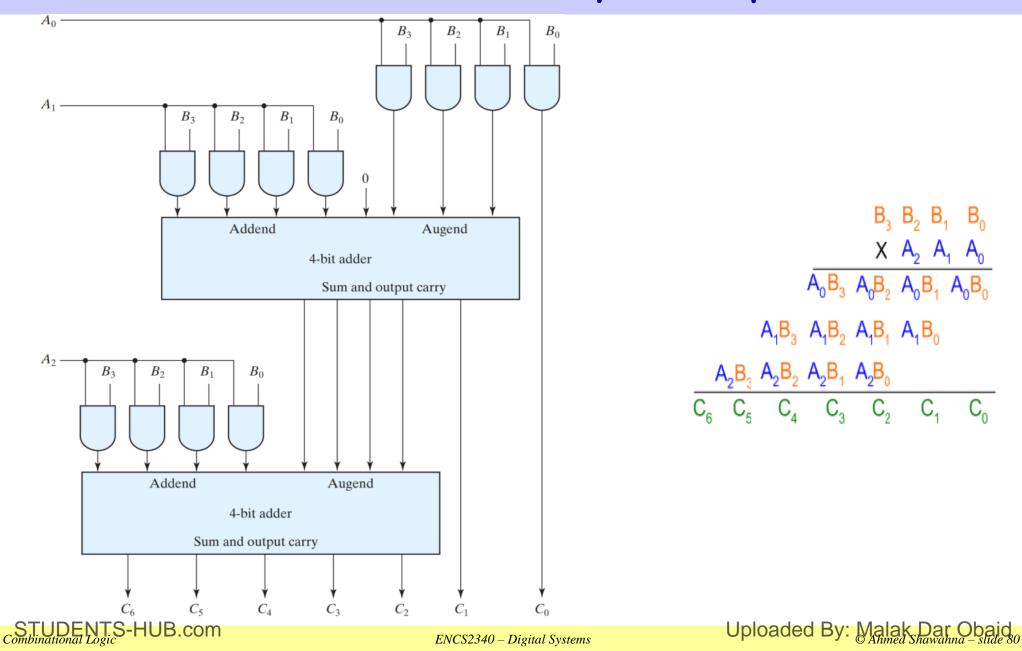

## 4-bit × 3-bit Binary Multiplier

- ♣ Suppose we want to multiply two numbers  $B = B_3 B_2 B_1 B_0$  and  $A = A_2 A_1 A_0$

- Step 2: Add the partial product

Requires (3 1) 4-bit binary adders

$$\begin{array}{c} B_{3} \ B_{2} \ B_{1} \ B_{0} \\ X \ A_{2} \ A_{1} \ A_{0} \\ \hline A_{0} B_{3} \ A_{0} B_{2} \ A_{0} B_{1} \ A_{0} B_{0} \\ \hline A_{1} B_{3} \ A_{1} B_{2} \ A_{1} B_{1} \ A_{1} B_{0} \\ \hline A_{2} B_{3} \ A_{2} B_{2} \ A_{2} B_{1} \ A_{2} B_{0} \\ \hline C_{6} \ C_{5} \ C_{4} \ C_{3} \ C_{2} \ C_{1} \ C_{0} \end{array}$$

Combinational Logic

ENCS2340 – Digital Systems

#### 4-bit × 3-bit Binary Multiplier

### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

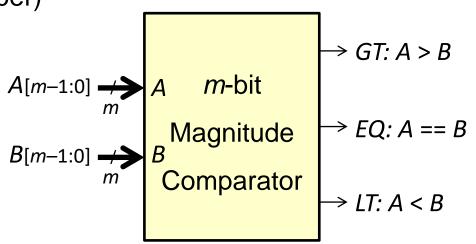

## Magnitude Comparator

A combinational circuit that compares two unsigned integers

#### Two Inputs:

♦ Unsigned integer A (*m*-bit number)

♦ Unsigned integer B (*m*-bit number)

#### Three outputs:

- $\Rightarrow$  A > B (GT output)

- $\Rightarrow$  A == B (EQ output)

- ♦ A < B (LT output)</p>

- Exactly one of the three outputs must be equal to 1

- While the remaining two outputs must be equal to 0

STUDENTS-HUB.com

ENCS2340 – Digital Systems

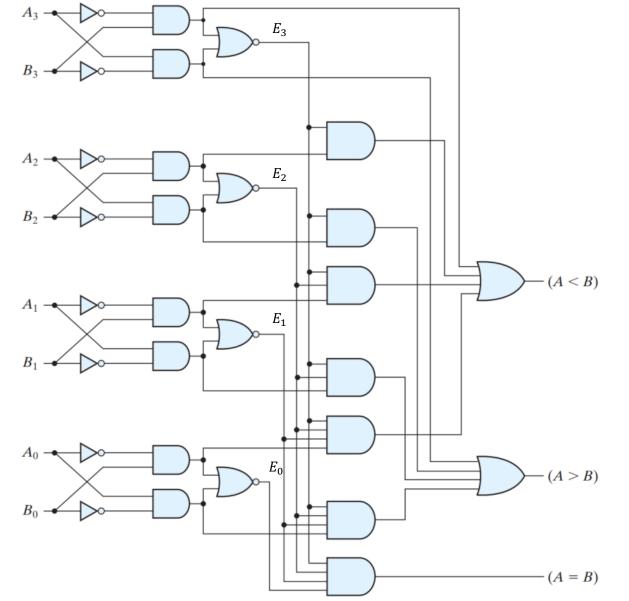

#### Example: 4-bit Magnitude Comparator

Inputs:

STUDENTS-HUB.com

- $\diamond A = A_3 A_2 A_1 A_0$

- $\diamond B = B_3 B_2 B_1 B_0$

- $\diamond$  8 bits in total  $\rightarrow$  256 possible combinations

- Not simple to design using conventional K-map techniques

- The magnitude comparator can be designed at a higher level

- $\clubsuit$  Let us implement first the EQ output (A is equal to B)

$$\diamond EQ = 1 \leftrightarrow A_3 == B_3$$

,  $A_2 == B_2$ ,  $A_1 == B_1$ , and  $A_0 == B_0$

♦ Define:  $E_i = (A_i = B_i) = (A_i \oplus B_i)' = A_i B_i + A'_i B'_i$

$\diamond$  Therefore,  $EQ = (A == B) = E_3 E_2 E_1 E_0$

#### The Greater Than Output

Given the 4-bit input numbers: *A* and *B*

1. If  $A_3 > B_3$  then GT = 1, irrespective of the lower bits of A and B

Define:

$$G_3 = A_3 B'_3$$

( $A_3 == 1$  and  $B_3 == 0$ )

2. If  $A_3 == B_3$  ( $E_3 == 1$ ), we compare  $A_2$  with  $B_2$

Define:

$$G_2 = A_2 B'_2$$

( $A_2 == 1$  and  $B_2 == 0$ )

3. If  $A_3 == B_3$  and  $A_2 == B_2$ , we compare  $A_1$  with  $B_1$

Define:  $G_1 = A_1 B'_1$  ( $A_1 == 1$  and  $B_1 == 0$ )

4. If  $A_3 == B_3$  and  $A_2 == B_2$  and  $A_1 == B_1$ , we compare  $A_0$  with  $B_0$

Define:  $G_0 = A_0 B'_0$  ( $A_0 == 1$  and  $B_0 == 0$ )

Therefore,  $GT = G_3 + E_3G_2 + E_3E_2G_1 + E_3E_2E_1G_0$

STUDENTS-HUB.com

### The Less Than Output

We can derive the expression for the LT output, similar to GTGiven the 4-bit input numbers: A and B

1. If  $A_3 < B_3$  then LT = 1, irrespective of the lower bits of A and B Define:  $L_3 = A'_3 B_3$  ( $A_3 == 0$  and  $B_3 == 1$ ) 2. If  $A_3 = B_3$  ( $E_3 == 1$ ), we compare  $A_2$  with  $B_2$ Define:  $L_2 = A'_2 B_2$  ( $A_2 == 0$  and  $B_2 == 1$ ) 3. Define:  $L_1 = A'_1 B_1$  ( $A_1 == 0$  and  $B_1 == 1$ ) 4. Define:  $L_0 = A'_0 B_0$  ( $A_0 == 0$  and  $B_0 == 1$ ) Therefore,  $LT = L_3 + E_3L_2 + E_3E_2L_1 + E_3E_2E_1L_0$ Knowing GT and EQ, we can also derive LT = (GT + EQ)'Uploaded By: Malak Dar Obaid Combinational Logic

### Example: 4-bit Magnitude Comparator

**STUDENTS-HUB.com**

ENCS2340 – Digital Systems

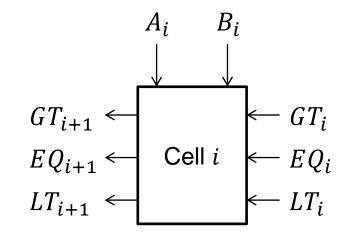

## Iterative Magnitude Comparator Design

- The Magnitude comparator can also be designed iteratively

- ✤ Each Cell *i* receives as inputs: Bit *i* of inputs *A* and *B*: *A<sub>i</sub>* and *B<sub>i</sub> GT<sub>i</sub>*, *EQ<sub>i</sub>*, and *LT<sub>i</sub>* from cell (*i* − 1)

- Each Cell *i* produces three outputs:

*GT*<sub>i+1</sub>, *EQ*<sub>i+1</sub>, and *LT*<sub>i+1</sub>

Outputs of cell *i* are inputs to cell (*i* + 1)

- ✤ Output Expressions of Cell i

$EQ_{i+1} = E_i \cdot EQ_i \qquad E_i = A'_i B'_i + A_i B_i (A_i \text{ equals } B_i)$   $GT_{i+1} = A_i B'_i + E_i \cdot GT_i \qquad A_i B'_i (A_i > B_i)$   $LT_{i+1} = A'_i B_i + E_i \cdot LT_i \qquad A'_i B_i (A_i < B_i)$ This has to be a set of the effective ATT of t

Third output can be produced for first two:  $LT_{i+1} = (EQ_{i+1} + GT_{i+1})'$ Combinational LogicENCS2340 - Digital SystemsLogicENCS2340 - Digital SystemsUploaded By: Malak Dar Obaid<br/>Obaid - shawahna - shae 87

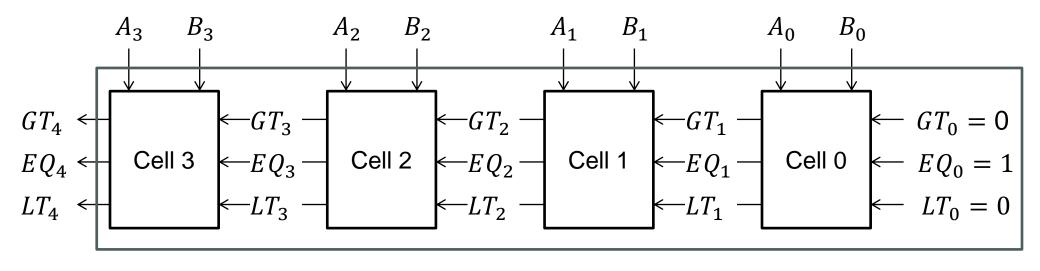

## Iterative Magnitude Comparator Design

- 4-bit magnitude comparator is implemented using 4 identical cells

Design can be extended to any number of cells

- Comparison starts at least-significant bit

- ✤ Final comparator output:  $GT = GT_4$ ,  $EQ = EQ_4$ ,  $LT = LT_4$

Uploaded By: Malak Dar Obaid, CAhmed Shawahna - stide 88

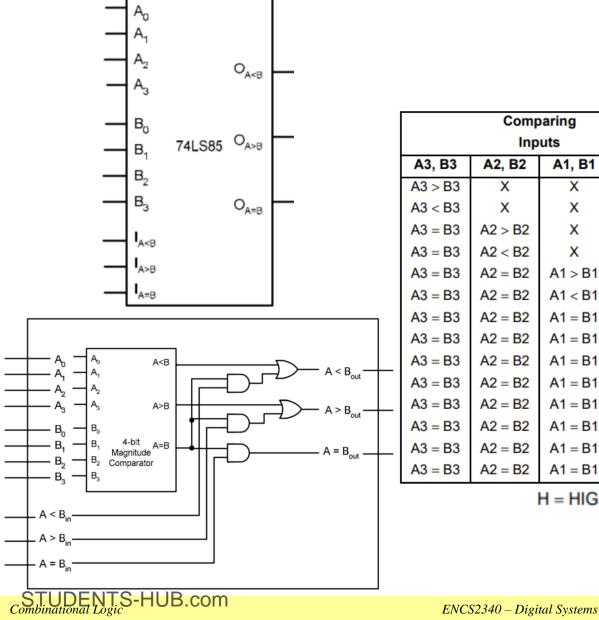

#### DM74LS85: A 4-Bit Magnitude Comparator

| Comparing |         |         | 0       | Cascading           | 3                   | Outputs             |       |                     |                     |

|-----------|---------|---------|---------|---------------------|---------------------|---------------------|-------|---------------------|---------------------|

|           | Inp     | uts     |         | Inputs              |                     |                     |       |                     |                     |

| A3, B3    | A2, B2  | A1, B1  | A0, B0  | <b>A</b> > <b>B</b> | <b>A</b> < <b>B</b> | <b>A</b> = <b>B</b> | A > B | <b>A</b> < <b>B</b> | <b>A</b> = <b>B</b> |

| A3 > B3   | Х       | Х       | Х       | Х                   | Х                   | Х                   | Н     | L                   | L                   |

| A3 < B3   | Х       | Х       | Х       | Х                   | Х                   | Х                   | L     | н                   | L                   |

| A3 = B3   | A2 > B2 | Х       | Х       | Х                   | Х                   | X                   | н     | L                   | L                   |

| A3 = B3   | A2 < B2 | Х       | Х       | х                   | х                   | X                   | L     | н                   | L                   |

| A3 = B3   | A2 = B2 | A1 > B1 | Х       | Х                   | Х                   | Х                   | н     | L                   | L                   |

| A3 = B3   | A2 = B2 | A1 < B1 | Х       | Х                   | Х                   | X                   | L     | Н                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 > B0 | х                   | Х                   | X                   | н     | L                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 < B0 | Х                   | Х                   | Х                   | L     | Н                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | н                   | L                   | L                   | н     | L                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | L                   | н                   | L                   | L     | н                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | L                   | L                   | н                   | L     | L                   | н                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | х                   | х                   | н                   | L     | L                   | н                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | н                   | н                   | L                   | L     | L                   | L                   |

| A3 = B3   | A2 = B2 | A1 = B1 | A0 = B0 | L                   | L                   | L                   | н     | н                   | L                   |

|           |         |         |         | 1.014               |                     |                     | 0     |                     |                     |

H = HIGH Level, L = LOW Level, X = Don't Care

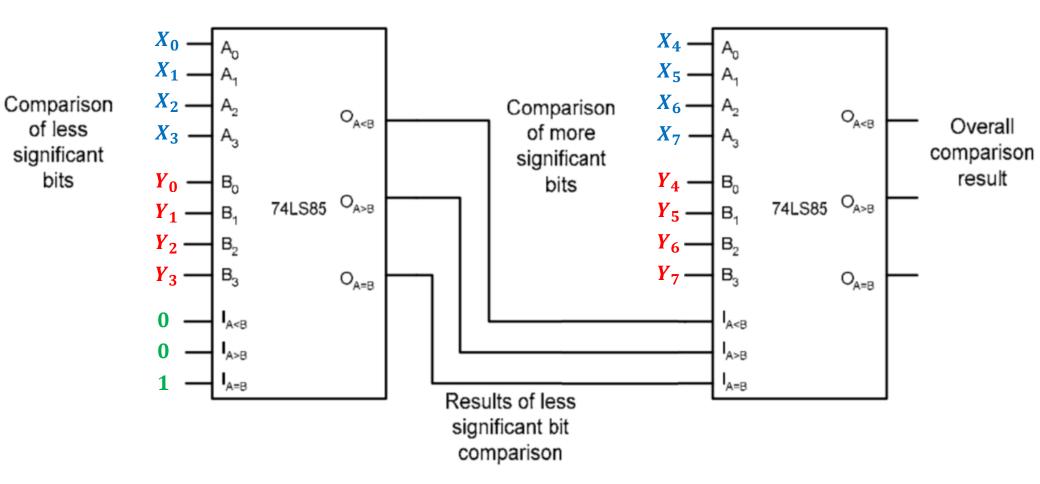

#### Cascading Two Comparators

### Signed Less Than: LT = X < Y

Design a circuit that computes signed LT (Signed X and Y)

Solution:

If (X < Y) then (X - Y) < 0, If (X == Y) then (X - Y == 0)

Do signed subtraction, LT = S<sub>4</sub> = sign-bit of the result

### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

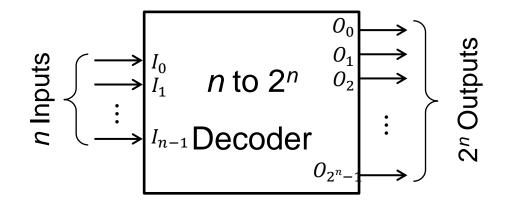

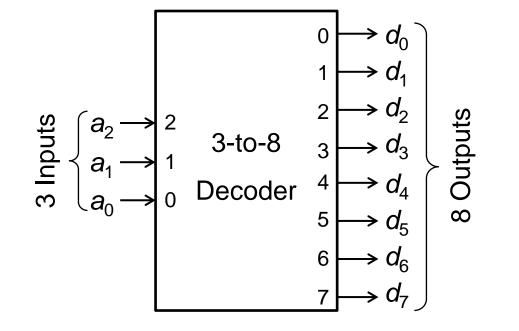

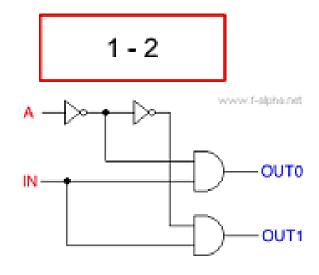

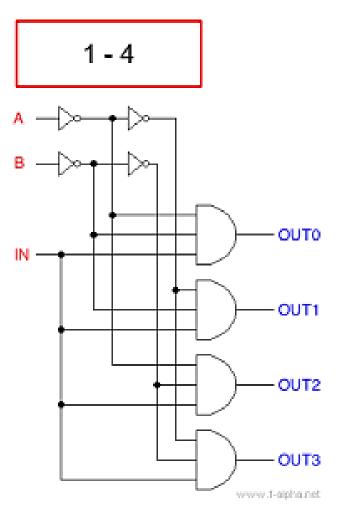

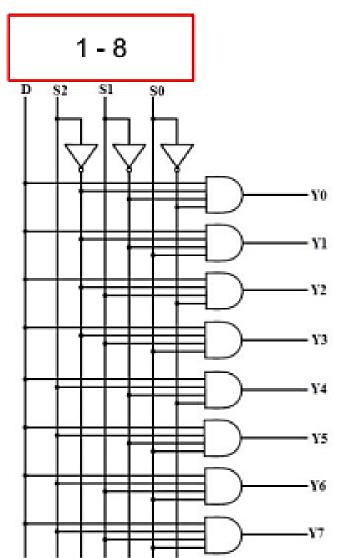

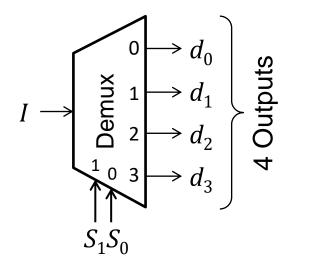

## **Binary Decoders**

- ✤ Given a *n*-bit binary code, there are 2<sup>n</sup> possible code values

- The decoder has an output for each possible code value

- The *n*-to- $2^n$  decoder has *n* inputs and  $2^n$  outputs

- Depending on the input code, only one output is set to logic 1

- The conversion of input to output is called decoding

UDENIS-HUB.com

A decoder can have less than 2<sup>n</sup> outputs if some input codes are unused

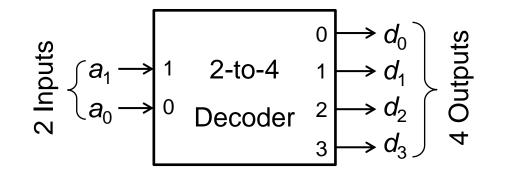

#### Examples of Binary Decoders

| <b>Truth Tables</b> |       |       |       |                |  |  |  |  |  |  |

|---------------------|-------|-------|-------|----------------|--|--|--|--|--|--|

| Inputs Outputs      |       |       |       |                |  |  |  |  |  |  |

| $a_1 a_0$           | $d_0$ | $d_1$ | $d_2$ | d <sub>3</sub> |  |  |  |  |  |  |

| 0 0                 | 1     | 0     | 0     | 0              |  |  |  |  |  |  |

| 0 1                 | 0     | 1     | 0     | 0              |  |  |  |  |  |  |

| 1 0                 | 0     | 0     | 1     | 0              |  |  |  |  |  |  |

| 1 1                 | 0     | 0     | 0     | 1              |  |  |  |  |  |  |

Combinational Logic

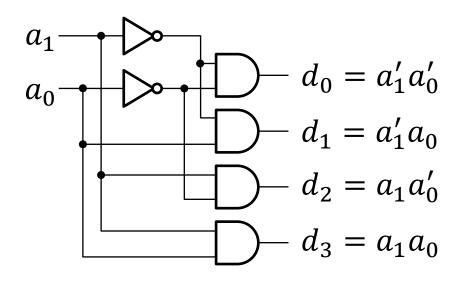

2-to-4 Decoder Implementation

Each decoder output is a minterm

Uploaded By: Malak Dar Obaid

ENCS2340 – Digital Systems

#### Examples of Binary Decoders

| Inputs $\bigcirc$ <t< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<> |               |       |         |       |                |       |       |       |       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|---------|-------|----------------|-------|-------|-------|-------|--|--|

| 0 0 0 0100000000 0 101000000000 1 0001000000000 1 1000100000001 0 000000100001 0 10000001001 1 000000010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Inputs        |       | Outputs |       |                |       |       |       |       |  |  |

| 0       0       1       0       0       0       0       0       0       0         0       1       0       1       0       0       0       0       0       0       0         0       1       0       0       1       0       0       0       0       0       0         0       1       0       0       0       1       0       0       0       0         1       0       0       0       0       0       1       0       0       0         1       0       0       0       0       0       1       0       0       0         1       0       0       0       0       0       0       1       0       0         1       0       0       0       0       0       0       1       0       0         1       1       0       0       0       0       0       0       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $a_2 a_1 a_0$ | $d_0$ | $d_1$   | $d_2$ | d <sub>3</sub> | $d_4$ | $d_5$ | $d_6$ | $d_7$ |  |  |

| 0       1       0       0       0       0       0       0       0         0       1       0       0       1       0       0       0       0       0         0       1       0       0       1       0       0       0       0       0         1       0       0       0       0       0       1       0       0       0         1       0       0       0       0       0       0       1       0       0       0         1       0       1       0       0       0       0       1       0       0       0         1       1       0       0       0       0       0       1       0       0         1       1       0       0       0       0       0       0       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 0 0         | 1     | 0       | 0     | 0              | 0     | 0     | 0     | 0     |  |  |

| 0       1       0       0       0       1       0       0       0       0         1       0       0       0       0       0       1       0       0       0       0         1       0       0       0       0       0       1       0       0       0       0         1       0       1       0       0       0       0       1       0       0       0         1       0       1       0       0       0       0       0       1       0       0         1       1       0       0       0       0       0       0       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 001           | 0     | 1       | 0     | 0              | 0     | 0     | 0     | 0     |  |  |

| 1 0 0       0       0       0       1       0       0       0         1 0 1       0       0       0       0       0       1       0       0       0         1 1 0       0       0       0       0       0       0       1       0       0         1 1 0       0       0       0       0       0       0       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 010           | 0     | 0       | 1     | 0              | 0     | 0     | 0     | 0     |  |  |

| 1 0 1       0       0       0       0       1       0       0         1 1 0       0       0       0       0       0       1       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 011           | 0     | 0       | 0     | 1              | 0     | 0     | 0     | 0     |  |  |

| 1       0       0       0       0       0       0       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 0 0         | 0     | 0       | 0     | 0              | 1     | 0     | 0     | 0     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101           | 0     | 0       | 0     | 0              | 0     | 1     | 0     | 0     |  |  |

| 1 1 1 0 0 0 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 1 0         | 0     | 0       | 0     | 0              | 0     | 0     | 1     | 0     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 1 1         | 0     | 0       | 0     | 0              | 0     | 0     | 0     | 1     |  |  |

**Truth Tables**

STUDENTS-HUB.com

ENCS2340 – Digital Systems

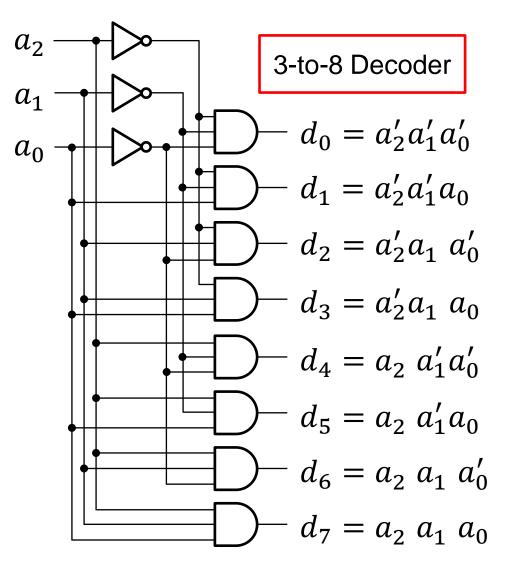

#### 3-to-8 Decoder Implementation

Each decoder output is a **minterm**

Combinational Logic

```

Uploaded By: Malak Dar Obaid

© Ahmed Shawahna - slide 97

```

ENCS2340 – Digital Systems

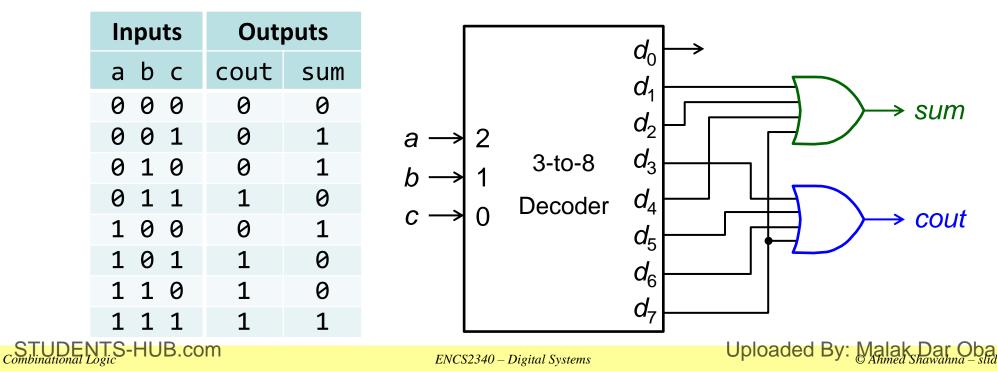

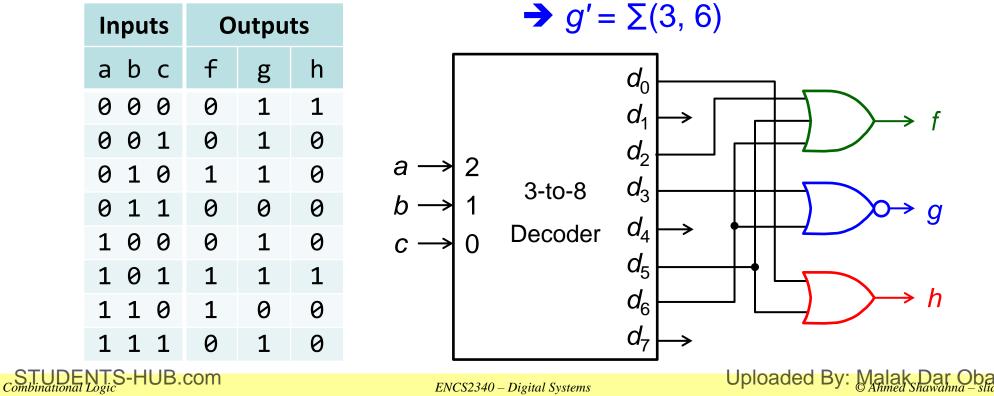

## Using Decoders to Implement Functions

- ✤ A decoder generates all the minterms

- ✤ A Boolean function can be expressed as a sum of minterms

- Any function can be implemented using a decoder + OR gate Note: the function must not be minimized

- **♦ Example:** Full Adder sum =  $\Sigma(1, 2, 4, 7)$ , cout =  $\Sigma(3, 5, 6, 7)$

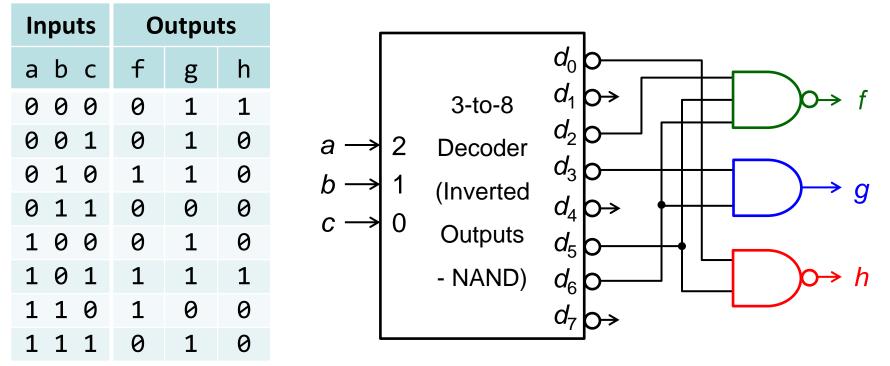

## Using Decoders to Implement Functions

- Good if many output functions of the same input variables

- ✤ If number of minterms is large → Wider OR gate is needed

- Use NOR gate if number of maxterms is less than minterms

- ★ Example:  $f(a,b,c) = \Sigma(2, 5, 6), g(a,b,c) = \prod(3, 6), h(a,b,c) = \Sigma(0, 5)$

ENCS2340 – Digital Systems

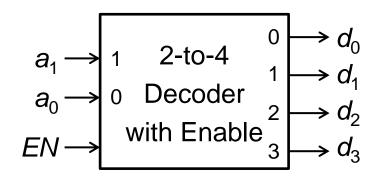

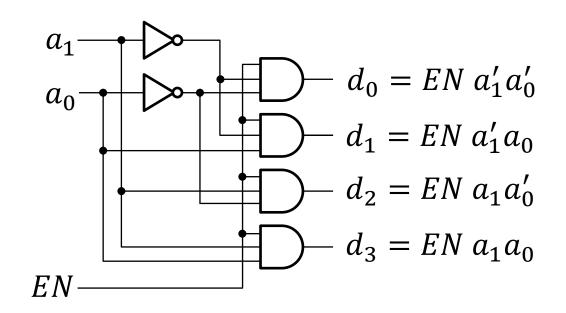

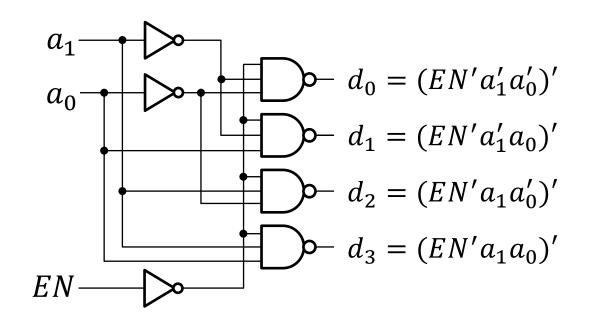

#### 2-to-4 Decoder with Enable Input

#### **Truth Table**

| In |                               | Out            | puts  |       |                |

|----|-------------------------------|----------------|-------|-------|----------------|

| EN | a <sub>1</sub> a <sub>0</sub> | d <sub>0</sub> | $d_1$ | $d_2$ | d <sub>3</sub> |

| 0  | ХХ                            | 0              | 0     | 0     | 0              |

| 1  | 0 0                           | 1              | 0     | 0     | 0              |

| 1  | 0 1                           | 0              | 1     | 0     | 0              |

| 1  | 1 0                           | 0              | 0     | 1     | 0              |

| 1  | 1 1                           | 0              | 0     | 0     | 1              |

If *EN* input is zero then all outputs are zeros, regardless of  $a_1$  and  $a_0$

Combinational Logic

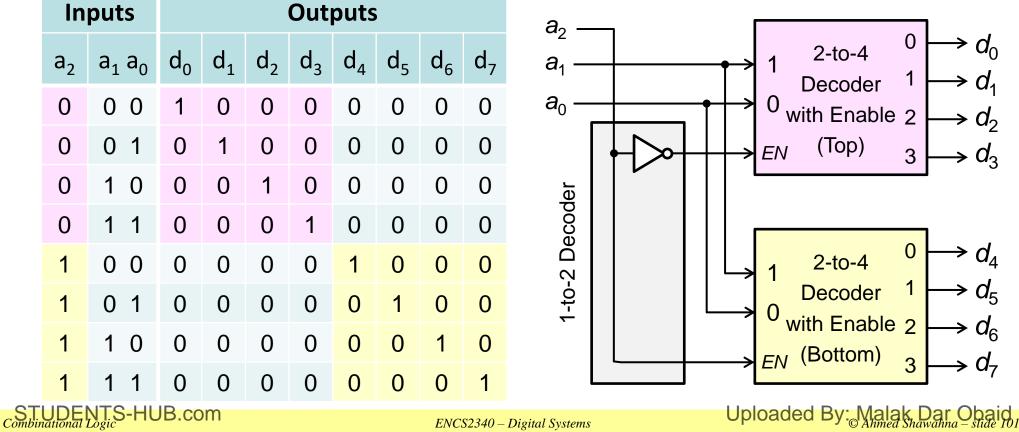

## **Building Larger Decoders**

- Larger decoders can be build using smaller ones

- ✤ A 3-to-8 decoder can be built using:

Two 2-to-4 decoders with Enable and an inverter (1-to-2 decoder)

ENCS2340 – Digital Systems

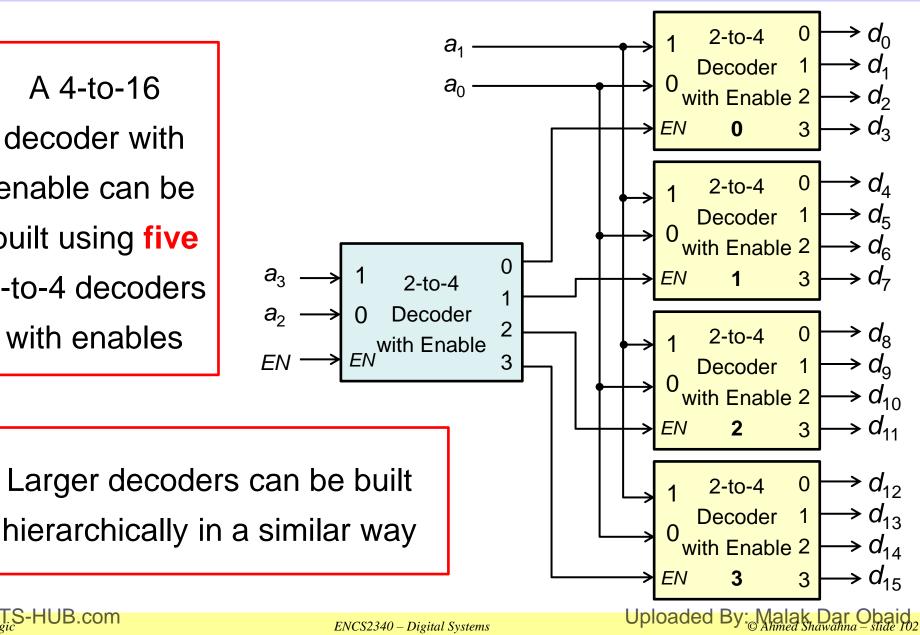

## **Building Larger Decoders**

A 4-to-16 decoder with enable can be built using five 2-to-4 decoders with enables

Combinational Logic

ENCS2340 – Digital Systems

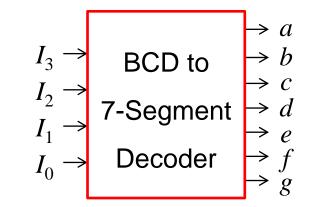

## BCD to 7-Segment Decoder

Seven-Segment Display:

а

Combinational Logic

- ♦ Made of Seven segments: light-emitting diodes (LED)

- ♦ Found in electronic devices: such as clocks, calculators, etc.

0 723456789

- ✤ BCD to 7-Segment Decoder

- ♦ Called also a decoder, but not a binary decoder

- ♦ Accepts as input a BCD decimal digit (0 to 9)

- $\diamond\,$  Generates output to the seven LED segments to display the BCD digit

- $\diamond$  Each segment can be turned on or off separately

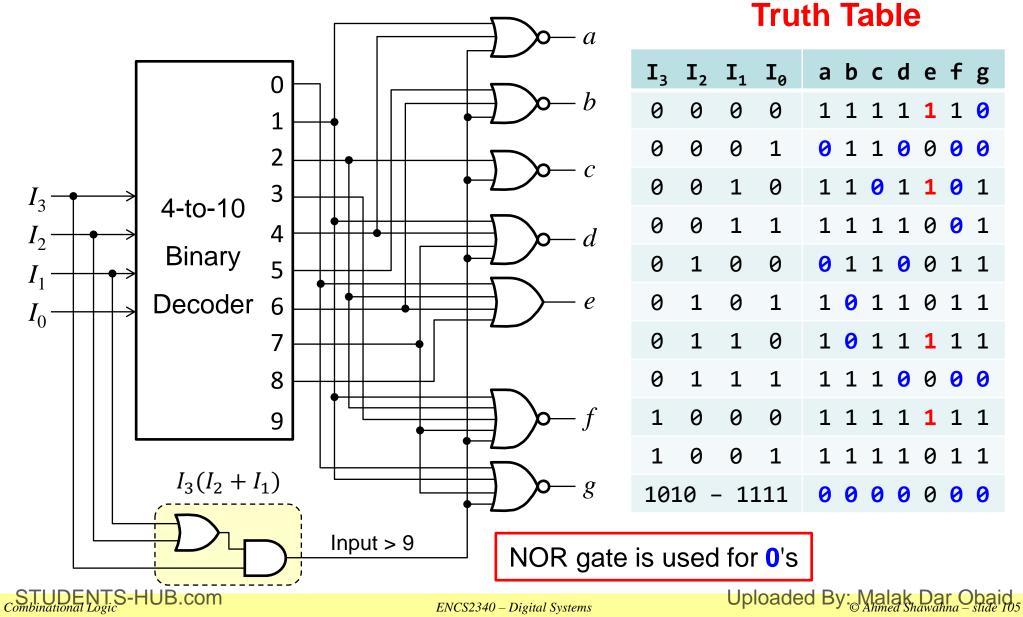

## BCD to 7-Segment Decoder

#### **Specification:**

- ♦ Input: 4-bit BCD ( $I_3$ ,  $I_2$ ,  $I_1$ ,  $I_0$ )

- $\diamond$  Output: 7-bit (*a*, *b*, *c*, *d*, *e*, *f*, *g*)

- Display should be OFF for Non-BCD input codes.

#### Implementation can use:

- ♦ A binary decoder

- ♦ Additional gates

STUDENTS-HUB.com

#### **Truth Table**

| B     | CD    | 7-    | Se             | g | me | en | t C | Du | tput |   |   |

|-------|-------|-------|----------------|---|----|----|-----|----|------|---|---|

| $I_3$ | $I_2$ | $I_1$ | I <sub>0</sub> |   | а  | b  | С   | d  | е    | f | g |

| 0     | 0     | 0     | 0              |   | 1  | 1  | 1   | 1  | 1    | 1 | 0 |

| 0     | 0     | 0     | 1              |   | 0  | 1  | 1   | 0  | 0    | 0 | 0 |

| 0     | 0     | 1     | 0              |   | 1  | 1  | 0   | 1  | 1    | 0 | 1 |

| 0     | 0     | 1     | 1              |   | 1  | 1  | 1   | 1  | 0    | 0 | 1 |

| 0     | 1     | 0     | 0              |   | 0  | 1  | 1   | 0  | 0    | 1 | 1 |

| 0     | 1     | 0     | 1              |   | 1  | 0  | 1   | 1  | 0    | 1 | 1 |

| 0     | 1     | 1     | 0              |   | 1  | 0  | 1   | 1  | 1    | 1 | 1 |

| 0     | 1     | 1     | 1              |   | 1  | 1  | 1   | 0  | 0    | 0 | 0 |

| 1     | 0     | 0     | 0              |   | 1  | 1  | 1   | 1  | 1    | 1 | 1 |

| 1     | 0     | 0     | 1              |   | 1  | 1  | 1   | 1  | 0    | 1 | 1 |

| 101   | 0 t   | o 1   | 111            |   | 0  | 0  | 0   | 0  | 0    | 0 | 0 |

## Implementing a BCD to 7-Segment Decoder

ENCS2340 – Digital Systems

#### NAND Decoders with Inverted Outputs

#### **Truth Table**

| In | Outputs                       |                |       |       |       |  |

|----|-------------------------------|----------------|-------|-------|-------|--|

| EN | a <sub>1</sub> a <sub>0</sub> | d <sub>0</sub> | $d_1$ | $d_2$ | $d_3$ |  |

| 1  | ХХ                            | 1              | 1     | 1     | 1     |  |

| 0  | 0 0                           | 0              | 1     | 1     | 1     |  |

| 0  | 0 1                           | 1              | 0     | 1     | 1     |  |

| 0  | 1 0                           | 1              | 1     | 0     | 1     |  |

| 0  | 1 1                           | 1              | 1     | 1     | 0     |  |

Some decoders are constructed with NAND gates. Their outputs are inverted. The Enable input is also active low (Enable if zero)

STUDENTS-HUB.com

$$\begin{array}{c} a_{1} \rightarrow \\ a_{0} \rightarrow \end{array} \begin{array}{c} 1 & 2 \text{-to-4} & 0 \\ 1 & 2 \text{-to-4} & 1 \\ 0 & \text{Decoder} & 2 \\ \text{with Enable} & 2 \\ 3 & 0 \rightarrow d_{2} \\ 0 \rightarrow d_{3} \end{array}$$

## Using NAND Decoders

- NAND decoders can be used to implement functions

- Use NAND gates to <u>output the minterms</u> (if fewer ones)

- Use AND gates to <u>output the maxterms</u> (if fewer zeros)

- **♦ Example:**  $f = \sum (2, 5, 6), g = \prod (3, 6), h = \sum (0, 5)$

Combinational Logic

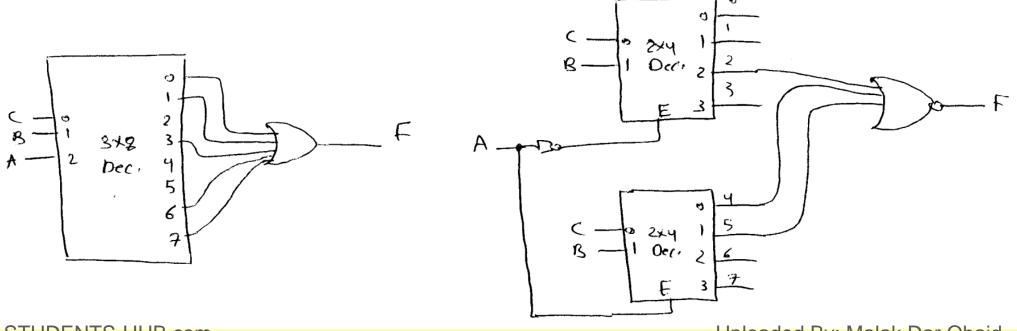

## Example

- ↔ Implement the Boolean function: F(A, B, C) = AB + A'C + A'B'

- a) Using a single 3x8 decoder and an OR gate.

- b) Using a single NOR gate and the minimum number of 2x4 decoders with enable.

$$F = \Sigma m(0, 1, 3, 6, 7)$$

STUDENTS-HUB.com

ENCS2340 – Digital Systems

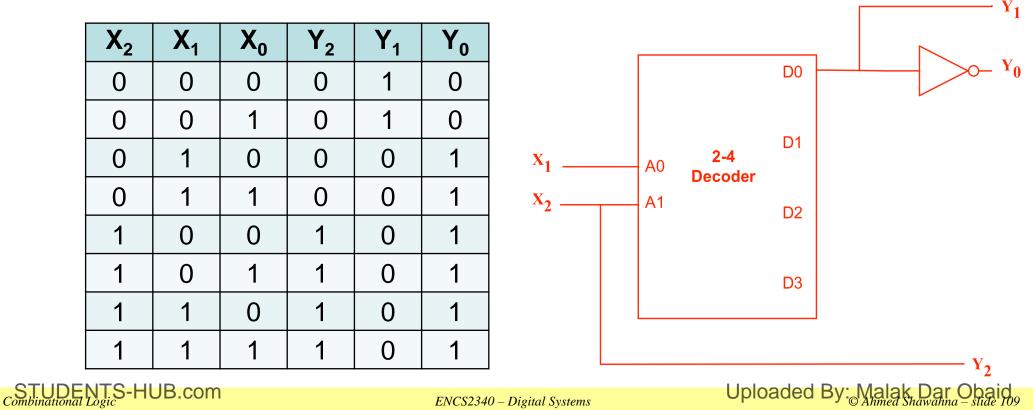

# Example

• Consider the following truth table, in which  $X_2$ ,  $X_1$ , and  $X_0$  are the inputs and  $Y_2$ ,  $Y_1$ , and  $Y_0$  are the outputs. Using a minimum-size decoder and a minimum number of additional gates, show how to implement  $Y_2$ ,  $Y_1$ , and  $Y_0$ . Your additional logic gates must use the smallest possible number of inputs.

#### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

- Multiplexers

- Design Examples

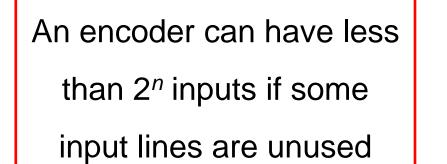

#### Encoders

- An encoder performs the opposite operation of a decoder

- It converts a  $2^n$  input to an *n*-bit output code

- The output indicates which input is active (logic 1)

- Typically, one input should be 1 and all others must be 0's

- The conversion of input to output is called encoding

Combinational Logic

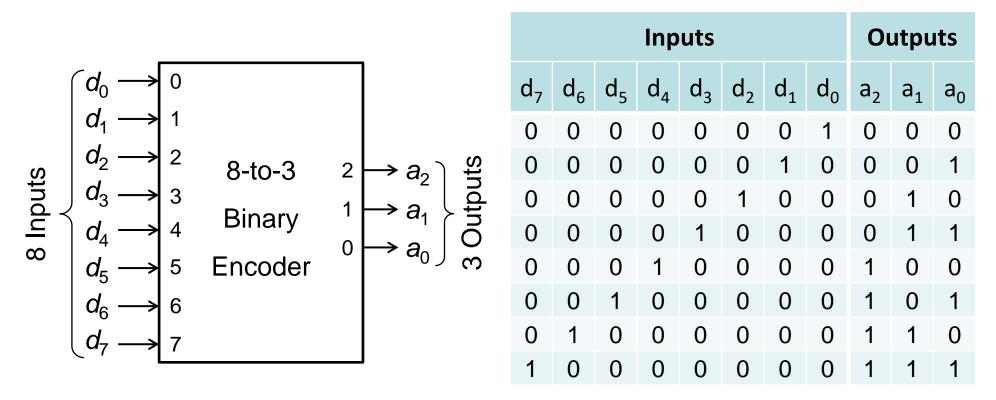

#### Example of an 8-to-3 Binary Encoder

- ✤ 8 inputs, 3 outputs, only one input is 1, all others are 0's

- Encoder generates the output binary code for the active input

- Output is not specified if more than one input is 1

Combinational Logic

Uploaded By: Malak Dar Obaid © Ahmed Shawahna - stide 112

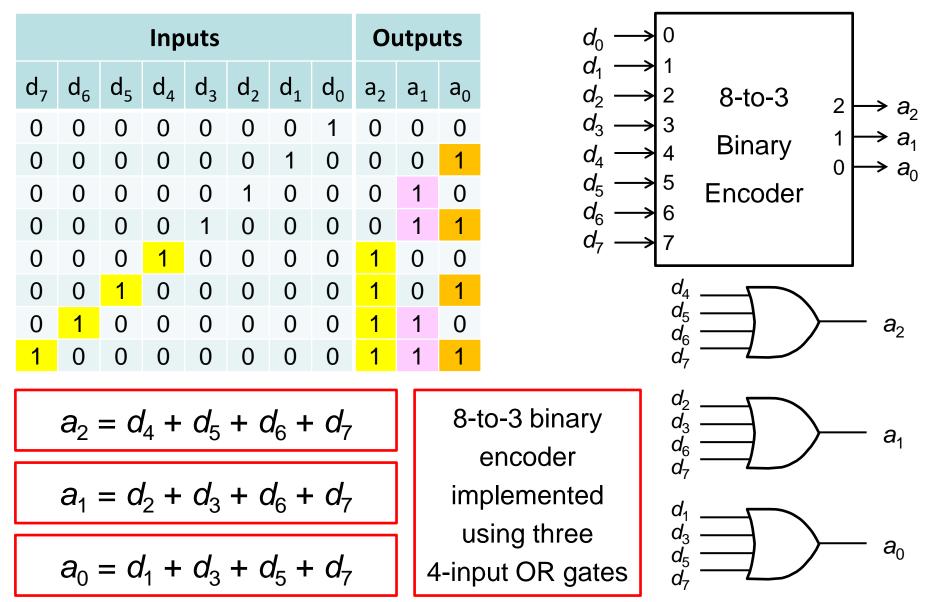

#### 8-to-3 Binary Encoder Implementation

STUDENTS-HUB.com

ENCS2340 – Digital Systems

#### **Binary Encoder Limitations**

- Exactly one input must be 1 at a time (all others must be 0's)

- If more than one input is 1 then the output will be incorrect

- ✤ For example, if  $d_3 = d_6 = 1$ Then  $a_2 a_1 a_0 = 111$  (incorrect)

- Two problems to resolve:

$$a_{2} = d_{4} + d_{5} + d_{6} + d_{7}$$

$$a_{1} = d_{2} + d_{3} + d_{6} + d_{7}$$

$$a_{0} = d_{1} + d_{3} + d_{5} + d_{7}$$

- 1. If **two** inputs are **1** at the same time, what should be the output?

- 2. If all inputs are 0's, what should be the output?

- Output  $a_2 a_1 a_0 = 000$  if  $d_0 = 1$  or all inputs are 0's

How to resolve this ambiguity?

STUDENTS-HUB.com

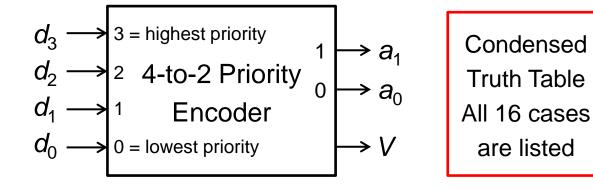

# Priority Encoder

- Eliminates the two problems of the binary encoder

- Inputs are ranked from highest priority to lowest priority

- If more than one input is active (logic 1) then priority is used Output encodes the active input with higher priority

- $\clubsuit$  If all inputs are zeros then the  ${\bf V}$  (Valid) output is zero

Indicates that all inputs are zeros

Combinational Logic

|                | Inp   | uts   | 0              | utpu  | ts             |   |

|----------------|-------|-------|----------------|-------|----------------|---|

| d <sub>3</sub> | $d_2$ | $d_1$ | d <sub>0</sub> | $a_1$ | a <sub>0</sub> | V |

| 0              | 0     | 0     | 0              | Х     | Х              | 0 |

| 0              | 0     | 0     | 1              | 0     | 0              | 1 |

| 0              | 0     | 1     | Х              | 0     | 1              | 1 |

| 0              | 1     | Х     | Х              | 1     | 0              | 1 |

| 1              | Х     | Х     | Х              | 1     | 1              | 1 |

Uploaded By: Malak Dar Obaid

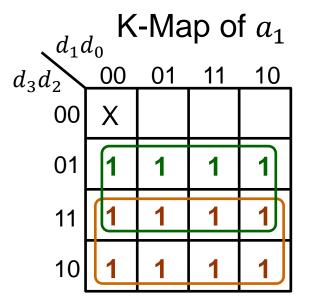

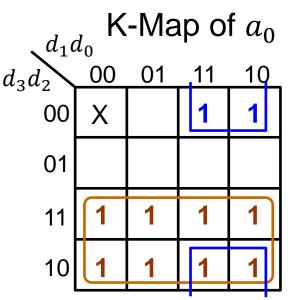

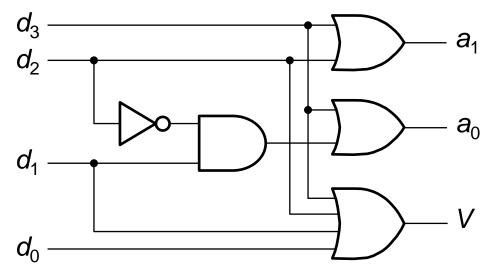

#### Implementing a 4-to-2 Priority Encoder

|                | Inp   | uts   | 0              | utpu  | ts             |   |

|----------------|-------|-------|----------------|-------|----------------|---|

| d <sub>3</sub> | $d_2$ | $d_1$ | d <sub>0</sub> | $a_1$ | a <sub>0</sub> | V |

| 0              | 0     | 0     | 0              | Х     | Х              | 0 |

| 0              | 0     | 0     | 1              | 0     | 0              | 1 |

| 0              | 0     | 1     | Х              | 0     | 1              | 1 |

| 0              | 1     | Х     | Х              | 1     | 0              | 1 |

| 1              | Х     | Х     | Х              | 1     | 1              | 1 |

Output Expressions:  $a_1 = d_3 + d_2$   $a_0 = d_3 + d_1 d'_2$  $V = d_3 + d_2 + d_1 + d_0$

STUDENTS-HUB.com

#### Next...

- Combinational Circuits

- Analysis Procedure

- Design Procedure

- Binary Adder-Subtractor

- Decimal Adder

- Binary Multiplier

- Magnitude Comparator

- Decoders

- Encoders

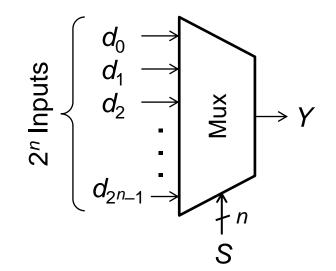

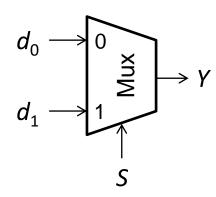

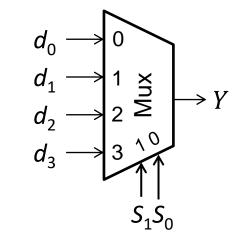

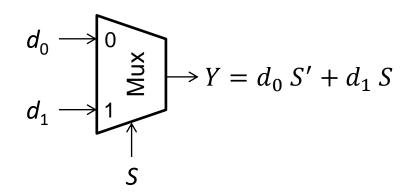

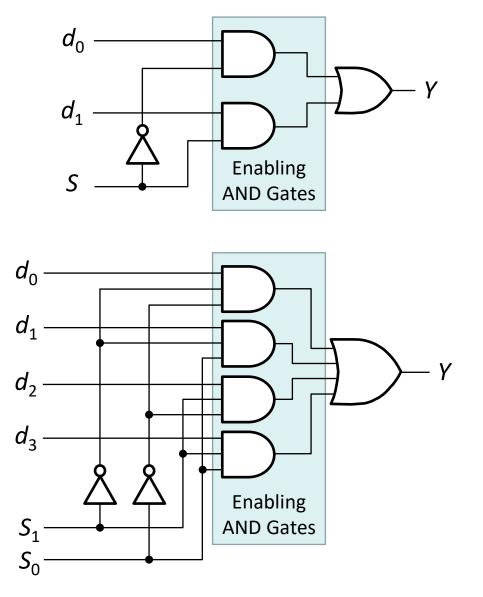

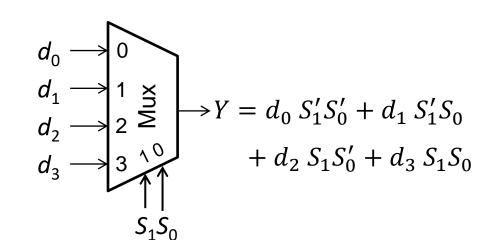

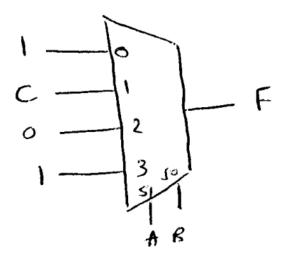

- Multiplexers