# DEPARTMENT OF COMPUTER SYSTEM ENGINEERING

Digital Integrated Circuits - ENCS333

#### Dr. Khader Mohammad

Lecture #5- Transistor\_I\_V\_Curve and Mode of operations

Integrated-Circuit Devices and Modeling

### **Transistor Sizing**

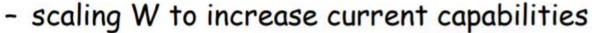

- Channel Resistance (from Chapter 3)

"ON" resistance of transistors

- Rn =  $1/(\mu_n Cox (W/L) (V_{GS}-Vtn))$

- Rp =  $1/(\mu_p Cox (W/L) (V_{SG}-|Vtp|))$

- $Cox = \varepsilon_{ox}/t_{ox}$  [F/cm<sup>2</sup>], process constant

### Channel Resistance Analysis

- R ≈ 1/W (increasing W decreases R & increases Current)

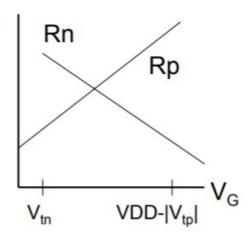

- R varies with Gate Voltage, see plot above

- If Wn = Wp, then Rn < Rp

- since μ<sub>n</sub> > μ<sub>p</sub>

- assuming Vtn ~ |Vtp|

- to match resistance, Rn = Rp

- adjust Wn/Wp to balance for  $\mu_n > \mu_p$

### **Transistor Sizing**

#### Channel Resistances

- Rn =  $1/(\mu_n Cox (W/L) (V_G Vtn))$

- Rp =  $1/(\mu_p Cox (W/L) (V_G |Vtp|))$

- Rn/Rp =  $\mu_p/\mu_n$

- if Vtn = |Vtp|, (W/L)<sub>n</sub> = (W/L)<sub>p</sub>

### Matching Channel Resistance

- there are performance advantage to setting Rn = Rp

- discussed in Chapter 7

- to set Rn = Rp

- define mobility ratio,  $r = \mu_n/\mu_p$

- $\cdot (W/L)_p = r (W/L)_n$

- pMOS must be larger than nMOS for same resistance/current

#### Negative Impact

-  $\Rightarrow$   $C_{Gp}$  = r  $C_{Gn}$  larger gate = higher capacitance

See class notes we explained in class for sizing

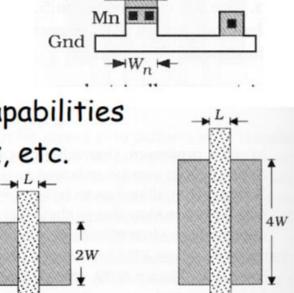

## Transistor Matching and Scaling

- Channel Resistance Matching

- increase Wp so that Rn = Rp

- pMOS larger than nMOS

- pMOS current drive = nMOS current drive

- Scaling ratio, S

1X

- typically in unit steps, 1x, 2x, 4x, etc.

- generally L kept at

minimum value

VDD

4X