# IC Notes for the Final Exam

## **Topics:**

∩1. Key Concepts from First Hour Exam Material ✓

- 2. Power  $\sqrt{}$

- 3. Combinational Logic Design (Static, Dynamic) 🗸

- 4. Sequential Logic Design 🗸

- 5. Interconnect 🗸

- 6. Layout and Timing

### **References:**

- 1. Digital Integrated Circuits

- 2. CMOS VLSI Design

Prepared By: Ghazi Haj Qassem

Up

Jibreel Born

Review Nonideal IV effects 1. Body effect Ve = Veo + y (VØS+VS2 ïs  $\bigcirc$ Øs= 2 Vy In NA y = tox  $\sqrt{2q} \Xi_{s} N_{A} = \sqrt{2q} \Xi_{s} N_{A}$ Cox For small values of Vis, eqn. O can be linearized to: -> 9-Ve= Ve+ Ky Vs ... 2 Vs6 kg = 2 √2øs OV2 × VE VV 2. Subthreshold Leakage 2 NAX 14 V95- V20 + 17 Vas - Ky Vsb NVT > Ids = Idso e Pass Transistors VDD-Vtn wegk "1" 1VEp1 VTC \* For complementary CMOS invertor: VOH = VOD, VOL = GND, VIH, VIL are when dVous = -1, and VAN Example: Match the following transitions 3.0 With their corresponding curve: a) A=B=0->1 2.0 b) A=1, B=0->1 V<sub>out</sub>, V C) A=0-1, B=1 1.0 M2: Ve = Ve + & [VØs+V12 -Ves M1. Ve. V6 +8 [ JU1+0 - JBJ] 0.0 1.0 <mark>₩a</mark> Vin, V 2.0 3.0 = V10 F= A.R Ver M2 on, M1 off you =) A=1, B=0-1 Vop  $M_1 \circ n_1 =$ M2 off -> on => A= 0->1, B=1 VIT Stionar PDN A) Du

Power Petroli Pdynamic static CMOS (switching) 0 -1  $P = \chi C_L V_{DD} \frac{1}{2}$  $= C_L V_{DD} \frac{1}{2} \frac{1}{2} \frac{1}{2}$ 3GH2 Vpp, 9-2 and CX Ps supply soils inputs withoming directioned and uncorrelated Ŷ ~<u>~~, = } P(0-)= Pop = 3.1 = 3</u> 4 4 16 νρρ A 8 Out Rp A= O RP 0 1 6 ALL = C2 akay. 1 С Ο 0 0 pour ١ 1 С ratio  $\frac{N_{0}(2^{N}-N_{0})}{2^{N}}$ No 2N x = 21 Example: do->1 \* n-input XOR gete  $\alpha = \frac{2^{N/2}}{2^{N}} \cdot \frac{2^{N/2}}{2^{N}} \cdot \frac{2^{N/2}}{2^{N}} \cdot \frac{2^{N/2}}{2^{N}} \cdot \frac{2^{N/2}}{2^{N}} \cdot \frac{2^{N/2}}{2^{N/2}} \cdot \frac{2^$ <u>۲</u> Ð

Combinational Logic Design

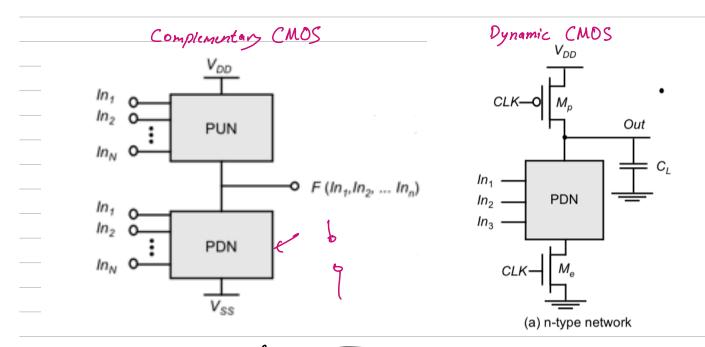

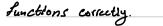

Dynamic Logic

- static CMOS logic with a fan-in of N requires 2N devices

Example: Implement the logic function F=AB+C using complementary CMOS and dynamic CMOS

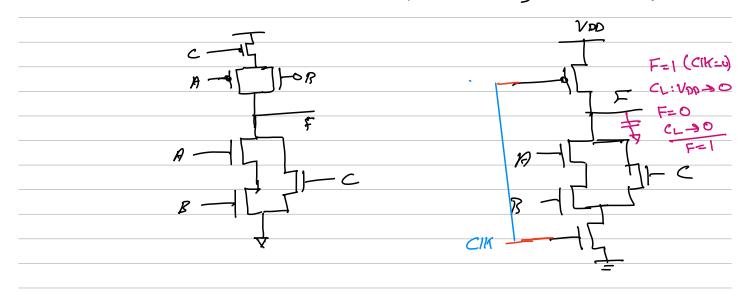

CIK = 0 -> CIK= Dynamic Logic Phases: CL(VDD) iff (F=1) CL (VOD) S Precharge [CIK = 0] CL(VOD->0) if F==>F=1 - Mp on - Out charged to Vob. -> Me off -> no static current flows from VoD to GND (no static power during prechase) (2) Evaluation -> Me on => Out conditionally discharged. CIKEU (preches) CIN =1 (EVAL)\_ PDN conducts PDN off CL=VAD Out discharged Precharsed Volu is stored on CL to GND PDN F== N.B. Once Out is discharged, it connot be charged until the next precharge phase. Jone transition per E.P. 2 PDN off = Out in high impedance state, susceptible to note Crosstalk (a) n-type network - Unlike complementary CMOS, where Out is in a low impedance State. (Static) Complementary CMOS VS Dynamic CMOS Static CMOS Dynamic CMOS transistor Count 2N🔿 tp14 =0 faster Switching speed Slower 🙋 CL T=, BC typically less Eypically higher power dissipation (high) VTC VOH= VDD, VOL= GND VOH = VOD, VOL = GND NMH= VDD-Vien VIL = VIH = VM = Vin - VOD/2 V12, V14, Vy cricuit depender parameters NM2 = Vin (10W) robust Pdynamic = x CV2f x=po U. NML

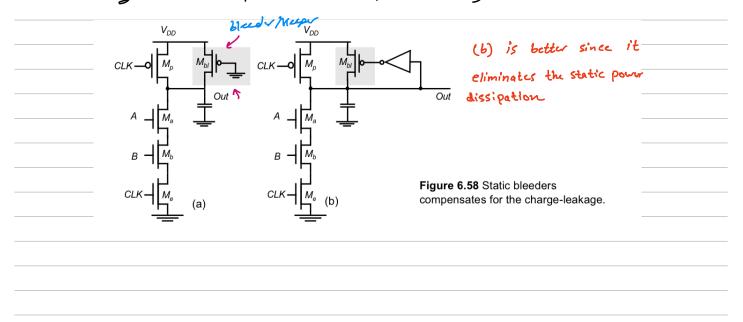

1854es in Dynamic Design I Backgate Compring I Clock-fudthrough I Charge Leakage

\* Leakage is caused by the high impedance state of the output node during evaluation, when PUN is off.

Solution: Reducing the output impedance of the output node during evaluation (add a bleder transistor)

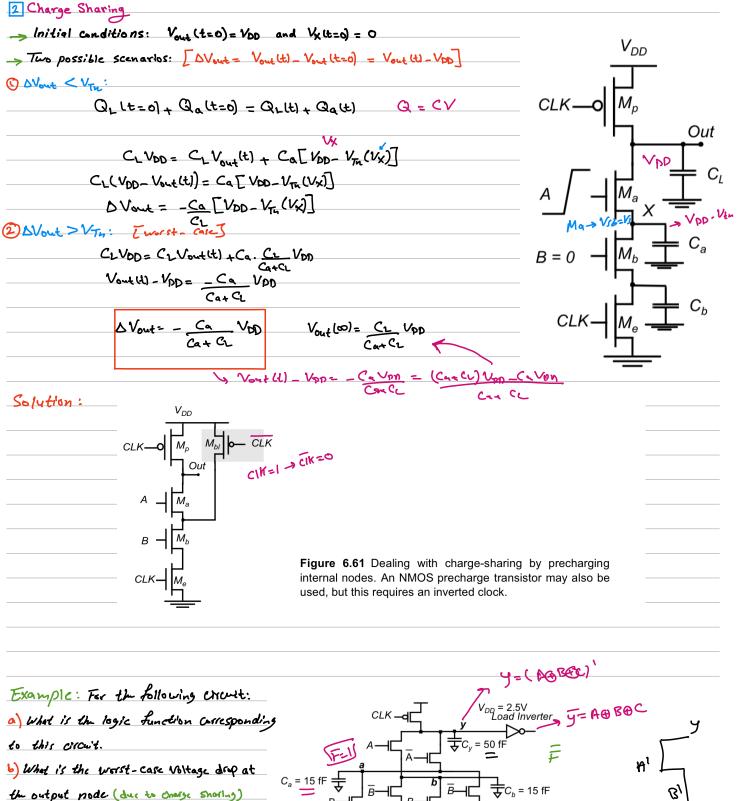

c) What should be the switching thershold

of the load inverter so that the circuit

| b) Cx=15FF+15JF                                                                                                                                    | A B C out       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $bV_{2} = C_{2} V_{p0} = -(2.5) = -0.44 V$                                                                                                         | 0000 25.1F      |

| $C_{u*}C_{l} \qquad \qquad$ | 0 0 1 0         |

|                                                                                                                                                    | O < / O         |

| c) VDD+ DVoul = 25-097 = 1.56V                                                                                                                     | 0 1 1 1- 3.FF   |

|                                                                                                                                                    | 1000 0 78F      |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    | note - 1 - 2517 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

|                                                                                                                                                    |                 |

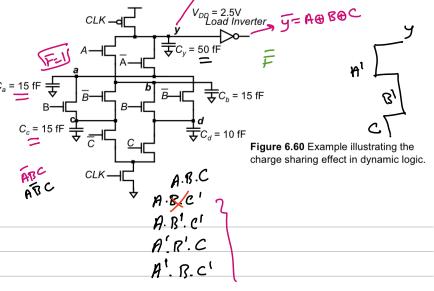

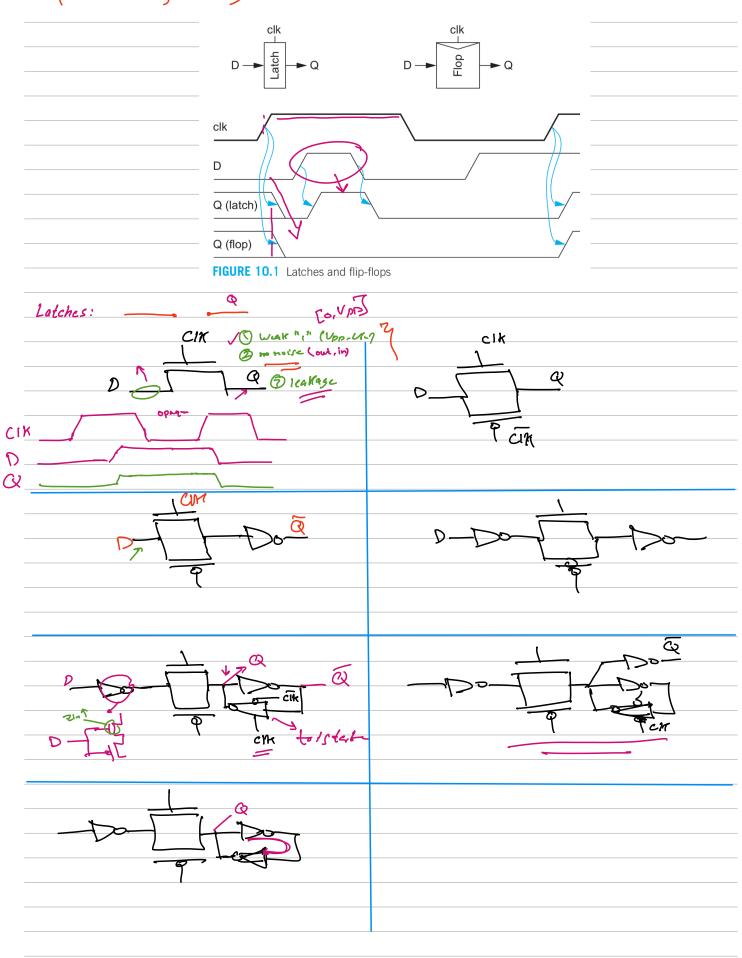

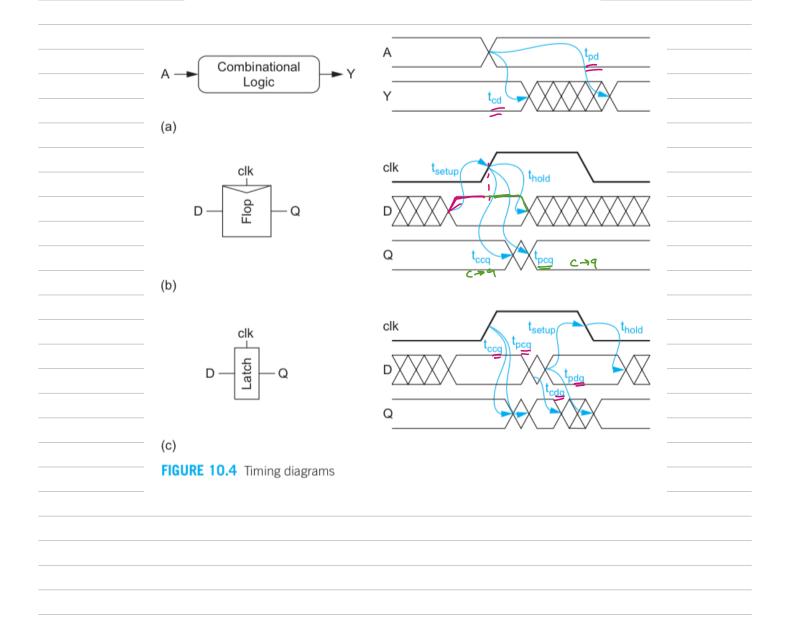

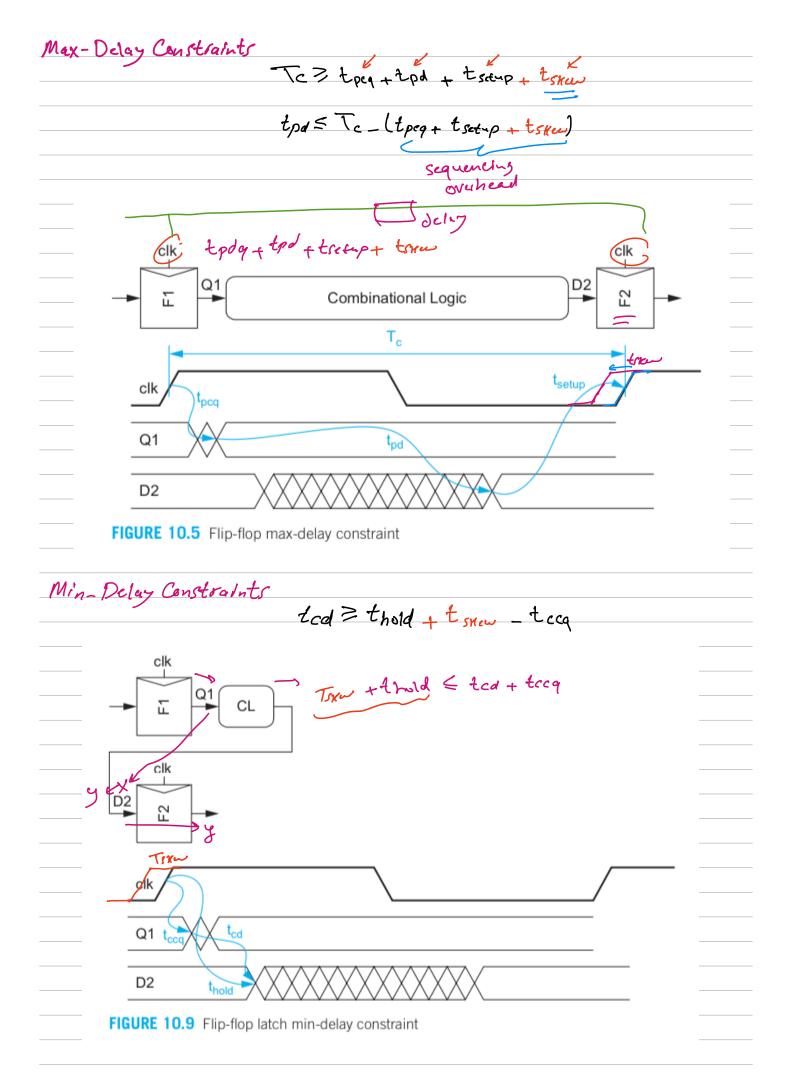

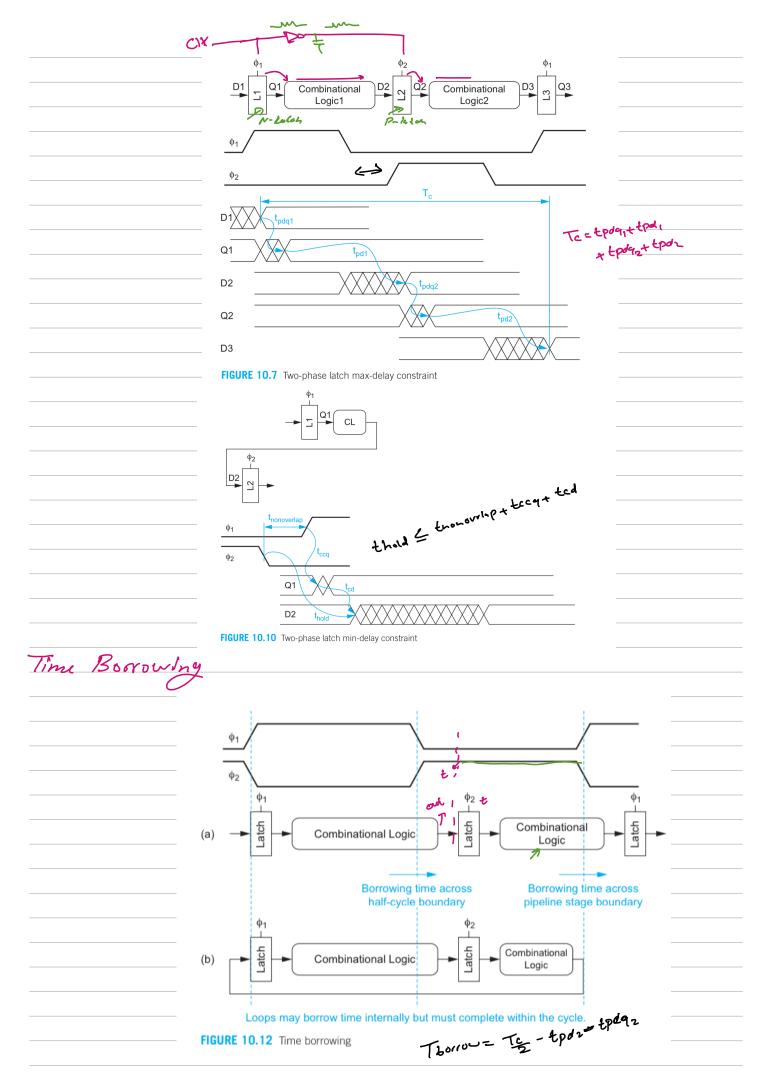

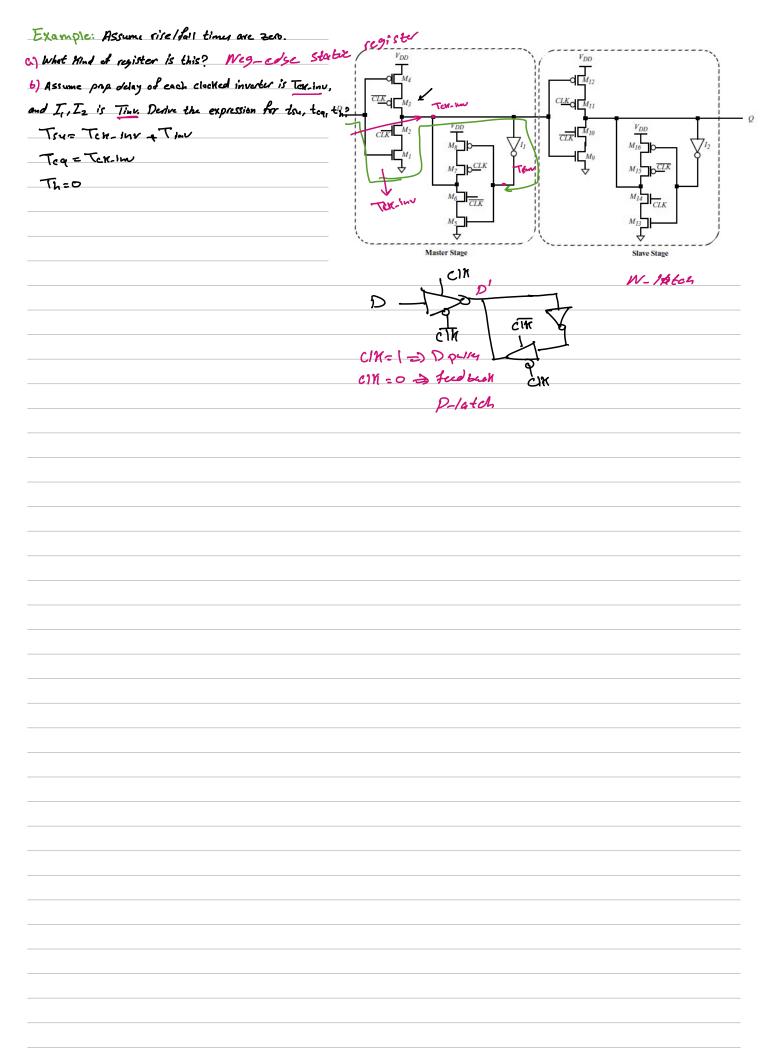

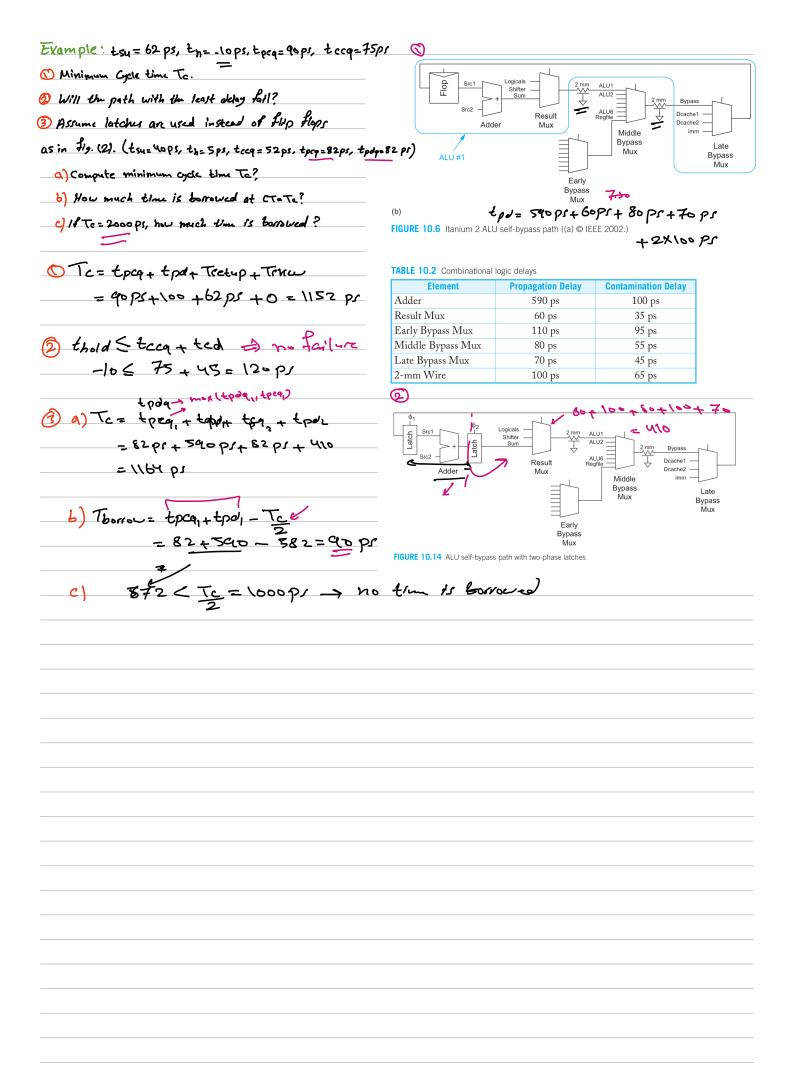

Sequential Logic Desig

#### Sequencing Element Timing Notation

| TABLE 10.1         Sequencing element timing notation |                                           |

|-------------------------------------------------------|-------------------------------------------|

| Term                                                  | Name                                      |

| $t_{pd}$                                              | Logic Propagation Delay                   |

| t <sub>cd</sub>                                       | Logic Contamination Delay min-            |

| t <sub>pcq</sub>                                      | Latch/Flop Clock-to-Q Propagation Delay   |

| t <sub>ccq</sub>                                      | Latch/Flop Clock-to-Q Contamination Delay |

| t <sub>pdq</sub>                                      | Latch $D$ -to- $Q$ Propagation Delay      |

| t <sub>cdq</sub>                                      | Latch D-to-Q Contamination Delay          |

| t <sub>setup</sub>                                    | Latch/Flop Setup Time                     |

| $t_{ m hold}$                                         | Latch/Flop Hold Time                      |

STUDENTS-HUB.com

Interconnect Interconnect Modellin lumped approximations: 2 TI-model 3 I-model 🕲 L-model R12 -71V 2 Wire Resistance heat resistance (RIJ) Example: Compute the sheet resistance of a 0.22 pum thick Cu wire in a 65 nm process. Find the total resistance if the wire 0.125 um wide and Imm long. Solution: R=RJL = 0.1 × 1000 = 800 L W 0.125  $R_{U} = P = \frac{1}{L}$ =0.1 27J Example: A lox unit-sized inverter drives a 2x inverter at the end of the Imm wire from the previous example. Suppose wire capacitance is 0-2fF/um and that a unit-sized nMOS tomaster has R= 10Ka and C= 0.1 fF. Estimate the propagation delay using Elmore delay modely ignoring diffusion capacitance Solution: C2U.2FA -= Imm 800 5ort CL= Cgp+ CgN = 6Cg=0.6 120 T= Revin ( 12 Cu) + (Revin + Ru) ( 12 Cu + Cz) = 1000 × 100 \$F+ (1000+80-) (0.715) - -

Crosstalk B=0-NOD Crosstall Dulay Effects AzVOD >0 B ΔV Ceff (A) Constant VDD Cgnd+Cadj Switching in the same  $\bigcirc$ Cand direction as 2Vnn Switching opposite to A Cand + 2 Cadj Cand fum) Example: Each wire in a pair of Imm lines has capacitance 0.08 fF/ um to ground and 0.12 fF/um to its neighbour. Each line is driven by an inverter with IKR effective resistance. Estimate the contamination and propagation delays of the poth. Neglect parasitic capacitance of the inverter and resistance of the wires. Solution: Contamination: min. delay Ronin \_m\_ Runn propagation: mex. delay + Cao' Cadj = Imn (0.127 7) Cgrd = Imm (0.0(12) tp = Rdriver [2Cadj + Cond] te = Rorive. [Cgnd] (2) Crosstalk Noise Effects Aggressor a. Floating Victim ( high impedance) DVvictim = \_\_\_\_\_ DVaggressor 6Vaggicsion Cend-v+Cadj Victim b. driven Victim Cand-1 DVvictim = Cadj 1\_ Waggressor Cend-v+Cadj 1+K Aggressor Raggassor K = Taggressor = Raggressor (Cgnd-a+ Cadj) Cand-a **DVaggicsser** Rvichim (Cgud-v + Cadj) Tvictim Rvictim Victim -W Cand-1