University of California College of Engineering Department of Electrical Engineering and Computer Sciences

TuTh 11-12:30

Thursday, December 15, 5:00-8:00pm

# EECS 141: FALL 2005-FINAL

|      | SOLUTION |       |  |

|------|----------|-------|--|

| NAME | Last     | First |  |

|      |          |       |  |

| SID |  |

|-----|--|

|     |  |

**D.** Markovic

Problem 1(7): 7Problem 2(9): 9Problem 3(15): 15Problem 4(11): 11Problem 5(10): 10Problem 6(8): 8Problem 7(15): 15

EECS 141: FALL 2005—FINAL

STUDENTS-HUB.com

Uploaded By: anonymous

#### **PROBLEM 1: Devices (7 pts)**

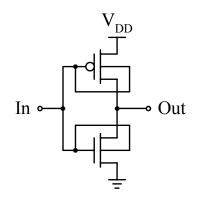

Consider the inverter shown below.

Compared to an inverter of the same size with the bulk connections at GND (for the NMOS) and  $V_{DD}$  (for the PMOS), and connecting the gates to the bulk, how will the following parameters change? For each of the parameters place an "X" in the appropriate column of the table.

| Parameter               | Increase | Decrease | Stays the same | Cannot be<br>determined |

|-------------------------|----------|----------|----------------|-------------------------|

| Input capacitance       | Х        |          |                |                         |

| Intrinsic cap           |          |          | X              | (X)                     |

| Intrinsic delay         |          | X        |                | (X)                     |

| Inverter V <sub>M</sub> |          |          | X              |                         |

| Drive current           | Х        |          |                |                         |

| Leakage current         | Х        |          | (X)            |                         |

| Switching energy        | (X)      |          | X              |                         |

Input cap increases due to added well-to-substrate cap needed to be driven by the input.

Intrinsic cap <u>stays the same</u> since the source/drain cap to bulk are not changed. (also accepted <u>cannot be determined</u>)

Intrinsic delay <u>decreases</u> since more drive current is available to drive the intrinsic load cap. (also accepted <u>cannot be determined</u>)

Inverter  $V_M$  stays the same since PMOS and NMOS current increase by the same amount.

Inverter drive current increases due to the reduction in threshold voltage by forward body bias.

Inverter leakage current <u>increases</u> due to smaller effective threshold. (we also accept if you considered only off current and answered <u>stays the same</u>)

Switching energy <u>stays the same</u> since the intrinsic load cap is not changed. (also OK if you considered gate cap and answered <u>increase</u>)

EECS 141: FALL 2005-FINAL

#### **PROBLEM 2:** Logic (9 pts)

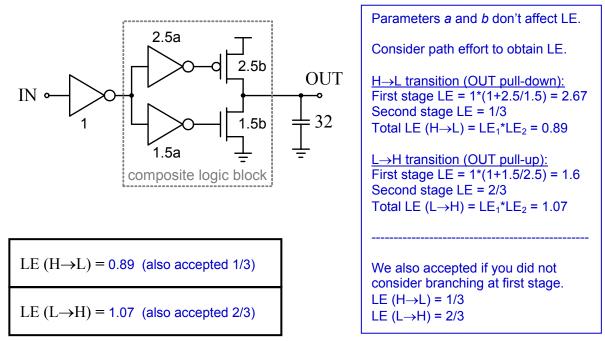

a. Find the logical effort of the composite logic block below. (4 pts) *Hint:* consider path logical effort.

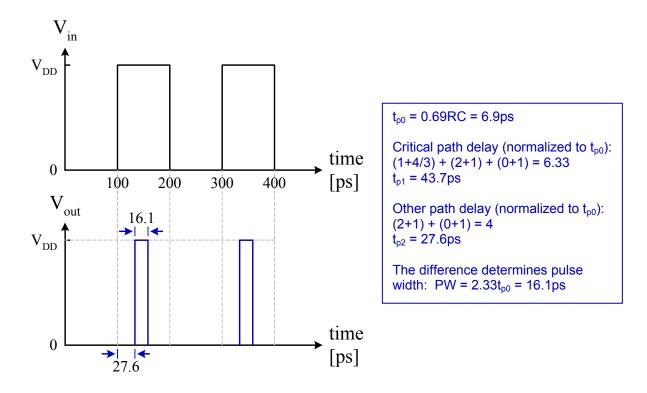

**b.** This logic block is placed in a circuit shown above. Write an expression for the propagation delay from input to output (the delay is normalized to  $t_{p0}$ ). Assume  $\gamma = 1$ . (3 pts)

Use stage-based delay calculation approach. Main point to realize is that parasitic cap of the second stage is different for L $\rightarrow$ H and H $\rightarrow$ L: For L $\rightarrow$ H, we compare total output W to 2/1 inverter (2.5b/1.25b inverter for simpler calculation). We get P (L $\rightarrow$ H) = 4b/3.75b = 16/15. For H $\rightarrow$ L, we compare total output W to 2/1 inverter (3b/1.5b) and obtain P (H $\rightarrow$ L) = 4b/4. 5b = 8/9.

$$D(L \rightarrow H) = (1+4a) + (1 + b/a) + (16/15 + 2/3*32/2.5b)$$

$D(H \rightarrow L) = (1+4a) + (1 + b/a) + (8/9 + 1/3*32/1.5b)$

c. Find a and b for optimum  $t_{pLH}$ . (2 pts)

Take partial derivative of D(L $\rightarrow$ H) w.r.t. *a* and *b*. a = (8/15)<sup>1/3</sup> = 0.81, b = 4a<sup>2</sup> = 2.62 Observe that 1.5a > 1 (assuming min transistor size is 1)

a  $(L \rightarrow H) = 0.81$  b  $(L \rightarrow H) = 2.62$

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

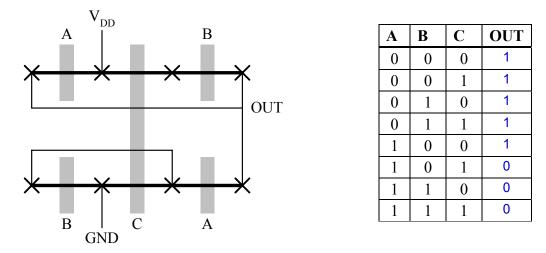

# PROBLEM 3: Layout techniques (15 pts)

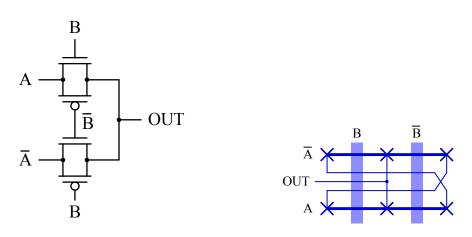

a. Write out the truth table that corresponds to the following stick diagram. (2 pts)

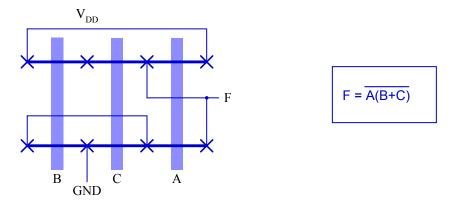

**b.** Implement  $F = \overline{AB+AC}$  in one diffusion region using stick diagram. Each gate must be used for both PMOS and NMOS. Use static CMOS. Clearly denote if crossing wires are connected or not. Use the fewest number of transistors possible. (4 pts)

**c.** Repeat part (b) for dynamic CMOS using a PUN. All PMOS transistors must share one diffusion. **(3 pts)**

EECS 141: FALL 2005—FINAL STUDENTS-HUB.com

Uploaded By: anonymous

d. Implement the following circuit in stick diagram. Assume all inputs are given and do not break the diffusion. (2 pts)

e. Fill out the table using only one word per entry. (4 pts)

| Logic Family  | Advantage | Disadvantage |

|---------------|-----------|--------------|

| Standard CMOS | Robust    | Area         |

| Dynamic       | Delay     | Power        |

| PTL           | Area      | Swing        |

| RTL           | Area      | Power        |

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

## PROBLEM 4: Sequential circuits and their building blocks (11 pts)

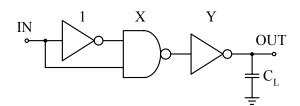

X and Y are the sizing factors. For the unit sized inverter assume  $\gamma = 1$ ,  $C_{in} = 2$  fF,  $R_{eq} = 5$  K $\Omega$ .

**a.** Assume  $C_L = 0$  and IN is a perfect 5 GHz clock with 50% duty cycle. Graph OUT and label important points on the x-axis. Do not label more than two points. X = Y = 1. (4 pts)

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

Uploaded By: anonymous

**b.** Assume  $C_L = 100$  fF. Given IN is a perfect 500 MHz clock signal with 50% duty cycle. Size X and Y such that OUT is a 500 MHz clock signal with 10% duty cycle and minimized propagation delay. (4 pts)

Clock is high for 1ns, want 200ps:  $t_{p0}^{*}(1+4/3^{*}X) = 200ps \implies X = 21$

For fixed X, delay is minimized when SE of the last two stages is equal:  $SE_2 = Y/X$ ,  $SE_3 = 50/Y$ . Y =  $(21*50)^{1/2} = 32.4$

| X = 21 | Y = 32.4 |

|--------|----------|

|--------|----------|

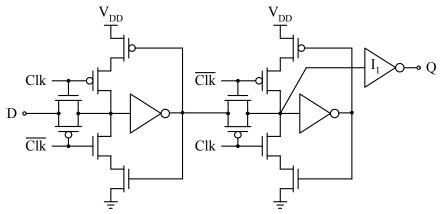

c. What is the functionality of the circuit below? Why is it advantageous to implement its functionality in this manner? (3 pts)

Functionality: flip-flop

Why is this circuit good:  $\underline{C^2MOS} \Rightarrow no skew$

Main reason to use inverter I1: buffer (avoid loading of state node)

EECS 141: FALL 2005—FINAL

STUDENTS-HUB.com

Uploaded By: anonymous

#### **PROBLEM 5: Timing (10 pts)**

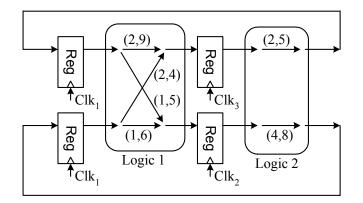

The notation for each path is (min-Delay, max-Delay).

The above is a register based system. The registers have following characteristics:  $(\min-t_{CQ}, \max-t_{CQ}) = (0.5, 2), t_{setup} = 1, t_{hold} = 1.$

**a.** Assuming Clk<sub>1-3</sub> have the same exact frequency and phase, determine the minimum T<sub>cycle</sub> for this system. (2 pts)

```

T_{min} > max-CQ + max-Logic + max-t<sub>setup</sub> = 2 +9 +1

T_{min} > 12

```

$Min T_{cycle} = 12$

b. If we use an arbitrary larger T<sub>cycle</sub>, what is the maximum random clock skew (|t<sub>skew</sub>|) between Clk<sub>1-3</sub> that this system can tolerate? From calculated max(|t<sub>skew</sub>|), what is the minimum T<sub>cycle</sub>? (3 pts)

```

\begin{array}{l} \mbox{min-Logic} > t_{\mbox{hold}} - \mbox{min-CQ} + |t_{\mbox{skew}}| \\ \mbox{case 1: btw Clk}_1 \mbox{ and Clk}_2 \\ \mbox{case 2: btw Clk}_1 \mbox{ and Clk}_2 \\ \mbox{$2 > 1 - 0.5 + |t_{\mbox{skew}}| \Rightarrow |t_{\mbox{skew}}| < 1.5 \\ 1 > 1 - 0.5 + |t_{\mbox{skew}}| \Rightarrow |t_{\mbox{skew}}| < 0.5 \\ \mbox{(case 1)} \\ \mbox{(case 2) critical case} \\ \mbox{$T_{\mbox{min}} > 12 - 0.5 = 11.5 $ for $t_{\mbox{skew}} < 0$ \\ \mbox{$T_{\mbox{min}} > 12 + 0.5 = 12.5 $ for $t_{\mbox{skew}} < 0$ \\ \mbox{$T_{\mbox{min}} > 12.5$ to satisfy both inequalities} \end{array}

```

| Max $( t_{skew} ) = 0.5$ | $Min T_{cycle} = 12.5$ |

|--------------------------|------------------------|

|--------------------------|------------------------|

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

Uploaded By: anonymous

**c.** Assuming no random skew, you are now permitted to adjust the timing of  $Clk_2$  with respect to  $Clk_1$  intentionally. What  $t_{skew21}$  would you choose to further reduce  $T_{cycle}$  (define  $t_{skew21}$  positive when  $Clk_2$  arrives later than  $Clk_1$ )? What is the new minimum  $T_{cycle}$ ? (5 pts)

| For Logic 1:                  | $\begin{array}{l} t_{hold} +  t_{skew, \ Clk21}  < min-CQ + min-Logic \\  t_{skew, \ Clk21}  < 0.5 \end{array}$                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| For Logic 2:                  | $\begin{array}{l} t_{\text{hold}} +  t_{\text{skew, Clk21}}  < \text{min-CQ} + \text{min-Logic} \\  t_{\text{skew, Clk21}}  < 3.5 \end{array}$ |

| Chose  t <sub>skew, Clk</sub> | $_{21}  < 0.5$ , to satisfy hold time constraints                                                                                              |

$\begin{array}{ll} \mbox{If } t_{skew,\ Clk21} = 0.5 & \\ & \mbox{For Logic 1:} & T_{min} > 2 + 6 + 1 - 0.5 = 8.5 \\ & \mbox{For Logic 2:} & T_{min} > 2 + 8 + 1 + 0.5 = 11.5 \end{array}$

Therefore:  $T_{min} = 11.5$

| $t_{\rm skew21} = 0.5$ | $Min T_{cycle} = 11.5$ |

|------------------------|------------------------|

|------------------------|------------------------|

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

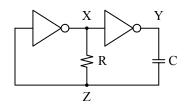

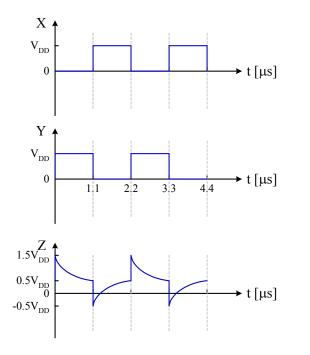

## **PROBLEM 6: Oscillator (8 pts)**

Figure below shows a relaxation oscillator. Assume  $V_{DD} = 2.5V$ ,  $R = 1k\Omega$ , C = 1nF. Switching threshold of the inverters is  $V_M = V_{DD}/2$ .

**a.** Calculate and draw voltage waveforms at nodes X, Y, and Z using diagrams below. Clearly label time and voltage axes. (6 pts)

| $V_{C} = V_{Y} - V_{Z}$<br>$\tau = RC = 1\mu s$                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------|

| For Y = V <sub>DD</sub> , X = 0:<br>$V_{C}(0) = -V_{DD}/2$ , $V_{C}(\infty) = V_{DD}$<br>Switching point: $V_{C}(t) = V_{DD}/2$ |

| For Y = 0, X = $V_{DD}$ :<br>$V_C(0) = V_{DD}/2$ , $V_C(\infty) = -V_{DD}$<br>Switching point: $V_C(t) = -V_{DD}/2$             |

| $V_{C}(\mathfrak{t})=V_{C}(\infty)+[V_{C}(0)-V_{C}(\infty)]^{*}\mathrm{e}^{-\mathfrak{t}/\tau}$                                 |

| Half-period is given by:<br>$T_{half} = \tau^* ln3$                                                                             |

**b.** What is the oscillation frequency? (2 pts)

$1/f_{OSC} = T_{OSC} = 2RC*ln3 = 2.2\mu s$

$f_{OSC} = \text{455 kHz}$

# PROBLEM 7: Memory (15 pts)

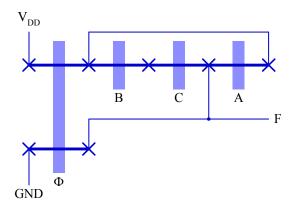

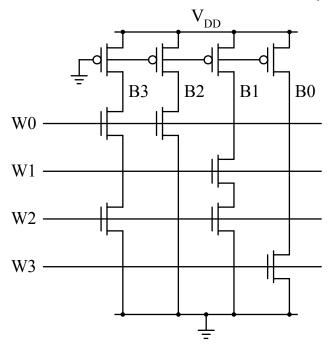

a. What are the words stored in the NAND memory block. (MSB on the left) (2 pts)

| W0 | 1100 |

|----|------|

| W1 | 0010 |

| W2 | 1010 |

| W3 | 0001 |

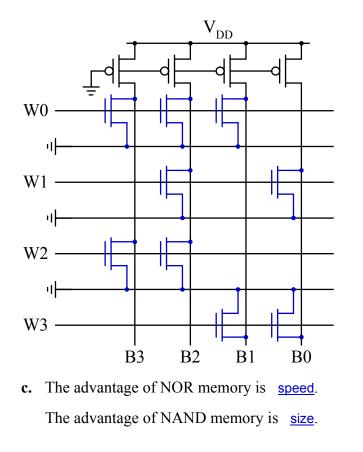

**b.** Program the following NOR block by drawing transistors. ( $W = \{B3, B2, B1, B0\}$ ) (3 pts)

| W0 | 0001 |

|----|------|

| W1 | 1010 |

| W2 | 0011 |

| W3 | 1100 |

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

(2 pts)

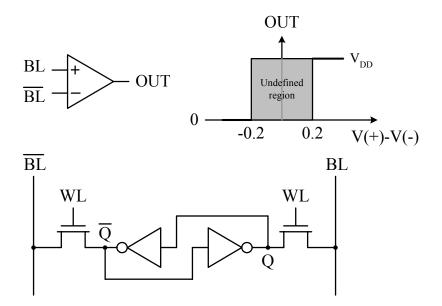

**d.** The inverters have  $W_p/W_n = 3\mu m/1\mu m$  and the other two transistors have width 0.5 $\mu m$ . Assume 1,000 words are attached to each bit line. BL and  $\overline{BL}$  are precharged to 0. The VTC for the sense amp is shown. In words, the amp's output become valid if the difference between the two inputs is greater than 0.2 volts. What is the read delay? For simplicity, calculate  $C_{eq}$  at the initial stage and assume it stays constant. (5 pts)

Refer to Table 3-2 on page 103 of text for MOS parameters. You can ignore bulk capacitance and use  $\varepsilon_{ox} = 3.5 \cdot 10^{-11}$  F/m,  $t_{ox} = 10$ nm,  $C_{overlap} = 0.1$  fF/µm, L = 0.25µm.

C<sub>L</sub> = 1,000 \* [(1/2µm \* 0.1 fF/µm) + (2/3 \* 1/2µm \* L \* E<sub>ox</sub>/t<sub>ox</sub>)] = 342 fF V<sub>M</sub> = 0.2V

$\begin{array}{l} \mbox{Smaller transistor is in velocity saturation/saturation the whole time.} \\ I_{DS}(initial) = 0.254 \mbox{ mA} \\ I_{DS}(final) = 0.225 \mbox{ mA} \\ R_{eq} = \frac{1}{2} * (2.5/0.254 \mbox{ mA} + 2.3/0.225 \mbox{ mA}) = 10 \mbox{k}\Omega \\ T_{read} = - \mbox{ RC In } (2.3/2.5) = 2.85 * 10^{-10} \sim 285 \mbox{ ps} \end{array}$

EECS 141: FALL 2005-FINAL

STUDENTS-HUB.com

e. Repeat part d but BL and  $\overline{BL}$  are precharged to V<sub>DD</sub>/2. (3 pts)

NMOS is pulling down while PMOS is pulling up. Assume each node change by 0.1V. This is a conservative estimate.

$$\label{eq:classical_states} \begin{split} & \underline{\text{For pull-up:}}\\ & C_L = 1,000 \ ^* \ (0.5 \mu m \ ^* \ 0.1 \ \text{fF}/\mu m) = 50 \ \text{pF}\\ & \text{NMOS in velocity saturation the whole time.}\\ & I_{DS}(\text{initial}) = 70 \ \mu \text{A}\\ & I_{DS}(\text{final}) = 48 \ \mu \text{A}\\ & R_{eq} = 20.7 \ \text{k}\Omega\\ & T_{read} = \text{RC In} \ (1.25/1.15) = 86.3 \ \text{ps} \end{split}$$

$$\label{eq:classical_states} \begin{split} & \frac{For \ pull-down:}{No \ C_{gd}} \\ & C_L = 1,000 \ ^* \ (0.5 \mu m \ ^* \ 0.1 \ fF/\mu m) = 50 \ pF \\ & \text{NMOS in velocity saturation the whole time.} \\ & I_{DS}(initial) = 285 \ \mu A \\ & I_{DS}(final) = 285 \ \mu A \\ & R_{eq} = 4.2 \ k\Omega \\ & T_{read} = RC \ ln \ (1.25/1.15) = 17.5 \ ps \end{split}$$

$T_{read} = 51.9 \text{ ps}$

EECS 141: FALL 2005-FINAL