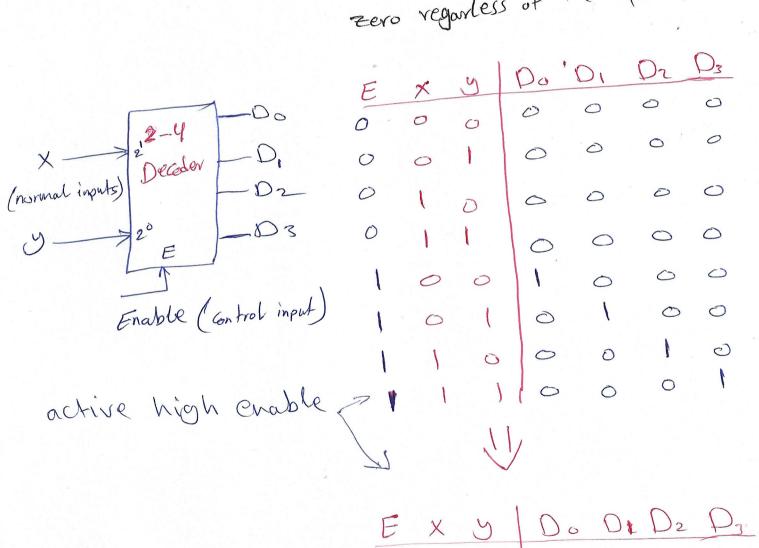

\* Decoder with Enable(E) 3-

E > high lever of If Enable 15 Zero Hen all outputs are

Zero regarless of the inputs (x,y)

If Enable 15 one the the outputsare

the minterns

Low level 3- If Enable is one all the outputs over zero regarless of the inputs.

| E | X | 5 | 00         | OL | D2 | Pg |

|---|---|---|------------|----|----|----|

| 0 | X | X | $\bigcirc$ | 0  | 0  |    |

| 1 | 0 | 0 | 1          | 0  | 0  | 0  |

| 1 | 0 | 1 | 0          | 1  | 0  | 0  |

| 1 | 1 | 0 | 0          | 0  | 1  | 0  |

| 1 | 1 |   | 0          |    | 0  | 1  |

STUDENTS-HUB.com

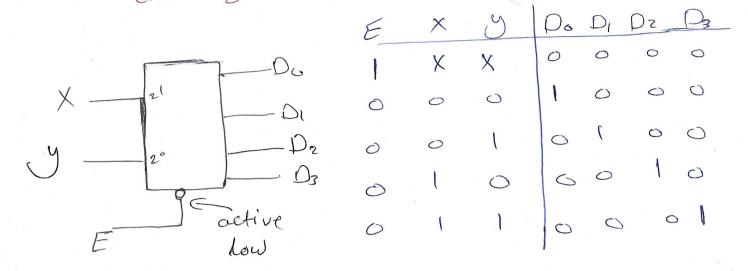

Example 3- Design 2 X4 active high Leader with active low enable 3-

Example & Design a 2 xy active low decoder active low Enable

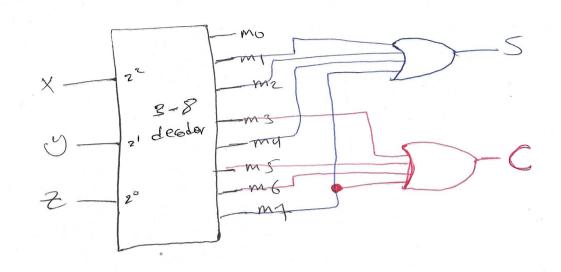

Examples-Implement the full adder using deader

$$S = 2(1,2,4,4)$$

$C = 2(3,5,6,7)$

| X | y | 2 | 5 | $\subseteq$ |

|---|---|---|---|-------------|

| 0 | 0 | 0 | 0 | 0           |

| 0 | 0 | 1 | 1 | 0           |

| 0 |   | 0 | 1 | 0           |

| 0 | 1 | 1 | 0 | 1           |

| 1 | ٥ | 0 | 1 | 0           |

| 1 | 0 | ( | 0 | 1           |

| 1 | 1 | 0 | 0 | 1           |

| 1 | ) |   | * | 1           |

STUDENTS-HUB.com

- 27-

we can design the full adder using 8-8 deader

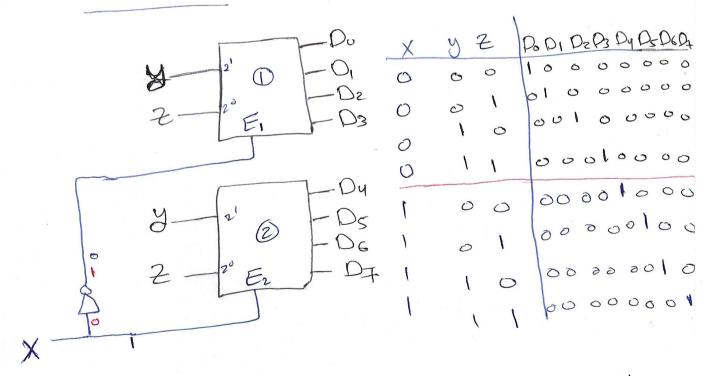

We Can implement the 8-8 decoder using 2-4 decoder using the enable input

If X = 0 then E1 will be I and Decoder I will work and If X=1 then E2 will be I and Decoder Z works

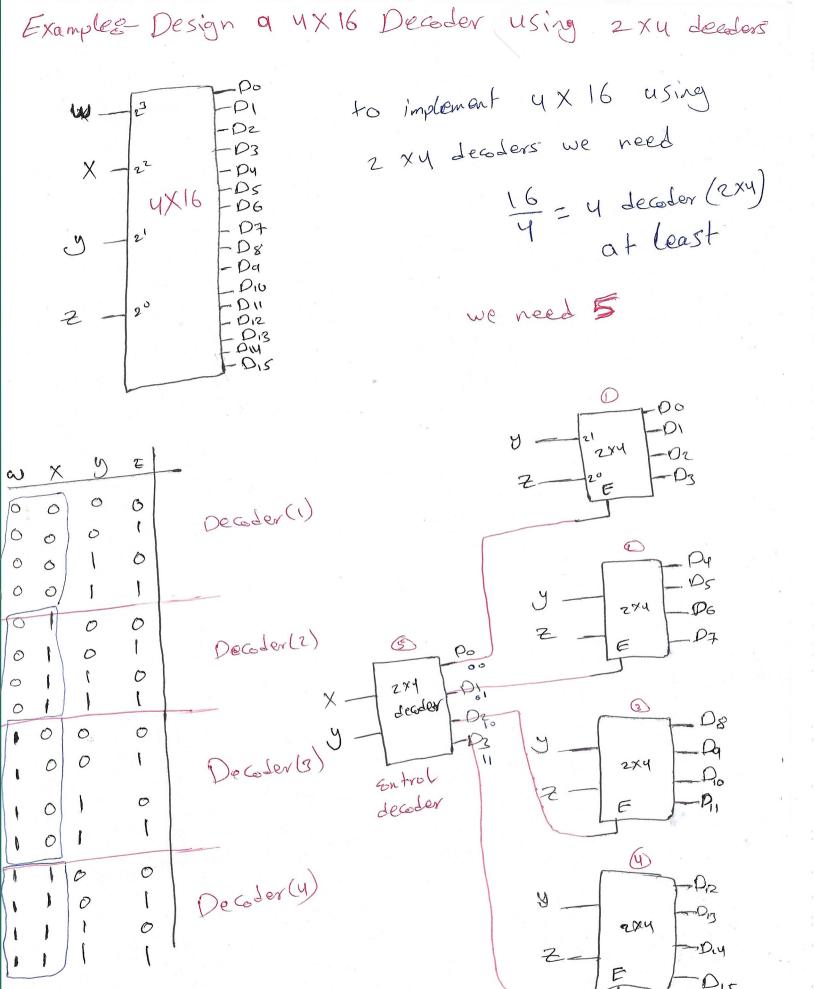

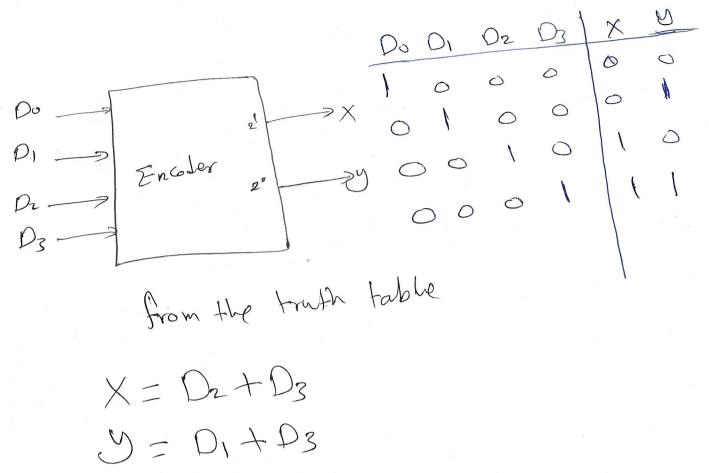

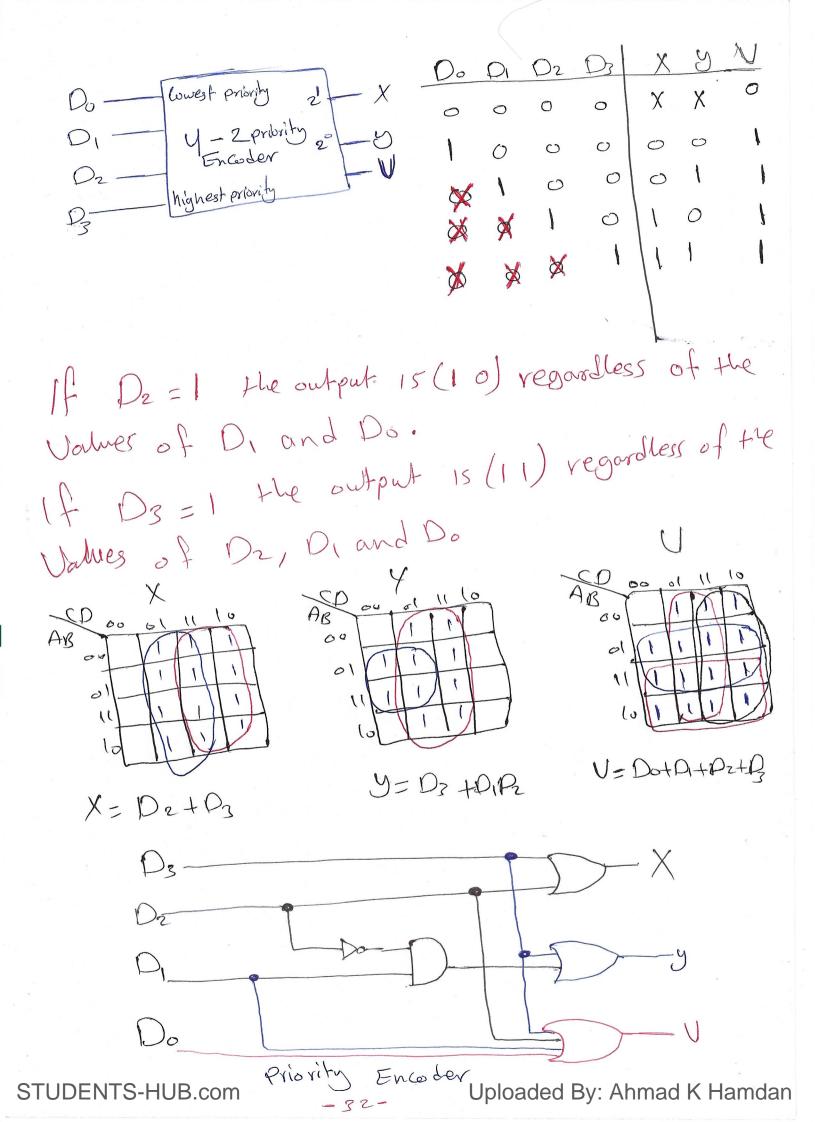

Examples- Implement the following fuction using 2xy decoder. F(A,B,C,D) = 5(0,2,4,15)B 0 MIS \* Encoders- Inverse operation of decoder ninputs peoder fronts 2" inputs Encoder noutputs Uploaded By: Ahmad K Hamdan STUDENTS-HUB.com -30YX2 Encoder

This type of Encoder has two problems (limitations) (1) If all inputs (Do-D3) are Zero 2) If more than one input 15 1 Thus the term "priority in Goder" is introduced with (v) valid output

X priority Encoder

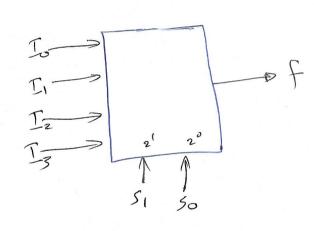

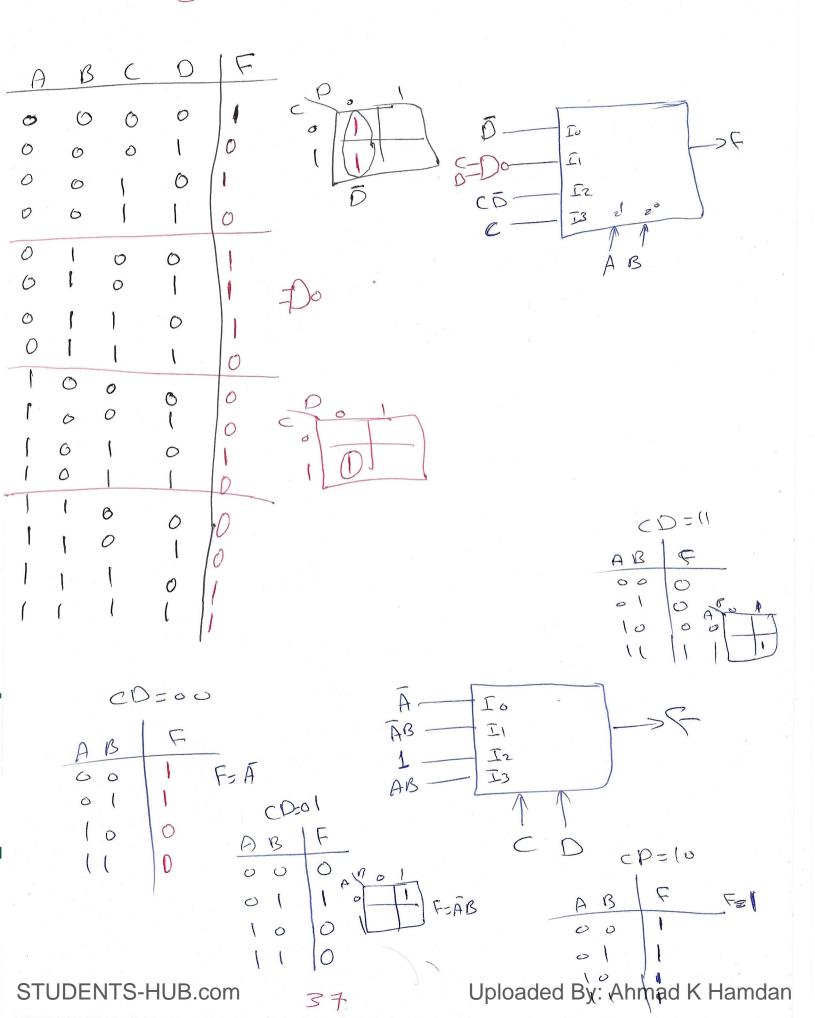

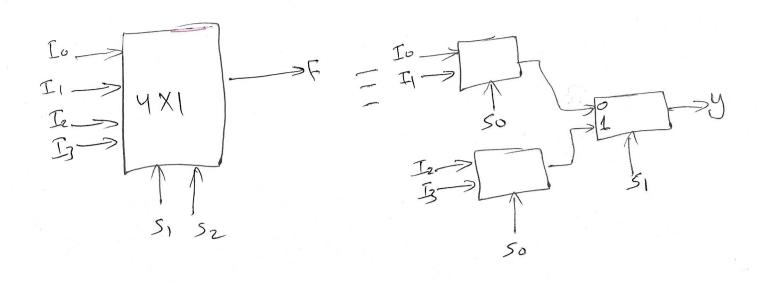

& Multiplexer (Mux) & A combination Circust that - Multiple data inputs (2") to select from - An n-bit select inputs (s) used for Control - one output (y) 2 inputs > Mux N-S' Selection (control inputs) Just one of the data inputs directed to the output based on the value of S Examples-Design a 2 x 1 mux 2 Io Mux

So (selection)

block diagram H 55= 0 F = Io else 5 = = 1 Uploaded By: Ahmad K Hamdan STUDENTSTHUB.com -53Truth toble

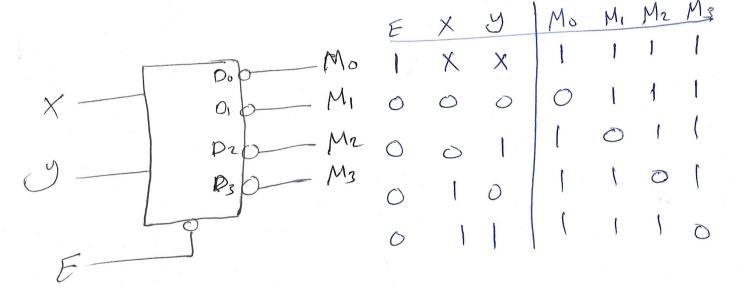

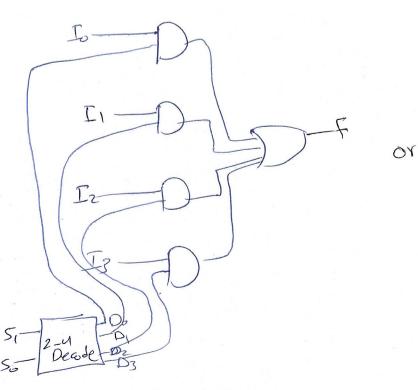

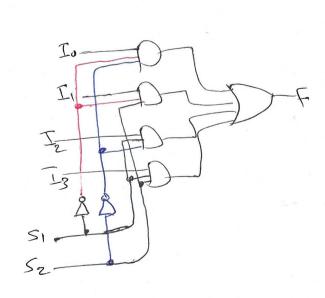

Example & YXI Mux

If

$$55 = 500$$

$F = I0$

else if  $550 = 501$

$F = I1$

else if  $5150 = 10$

$F = I2$

else  $F = I3$

STUDENTS-HUB.com

-34-

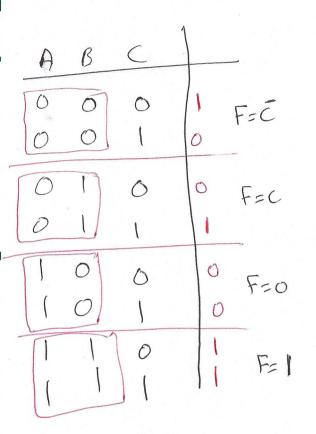

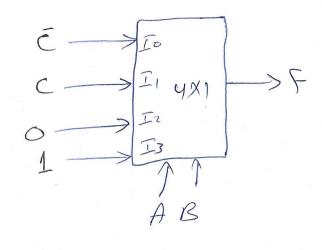

Examples implement the following Function using MuX.  $F(X,Y,Z) = \Sigma(1,2,6,7)$

Example: implement the following function Using 8x1 and 4x1 Max. F(A,B,C)=

-35-

STUDENTS-HUB.com

Examples Implement F(A,B,C)= E(0,3,6,7) using 2x1

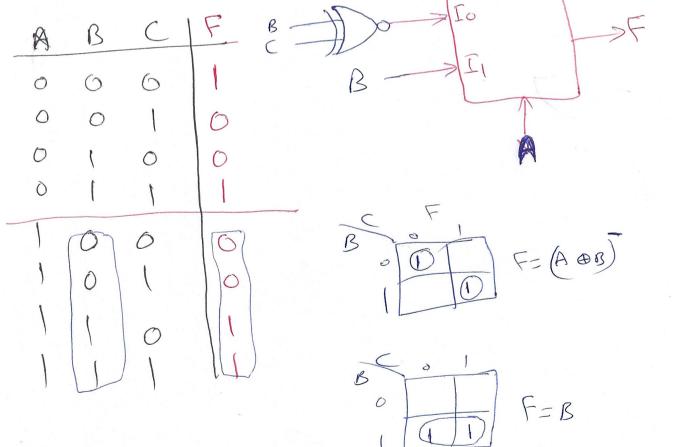

Example & Implement the F-(A,B,C,D) & (0,2,4,5,6,10,14,15)

using 4X1 Mux.

& Building larger Multiplexer

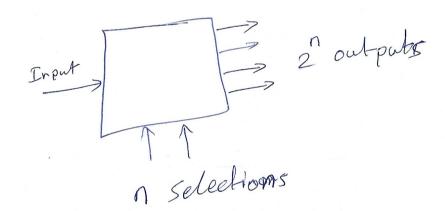

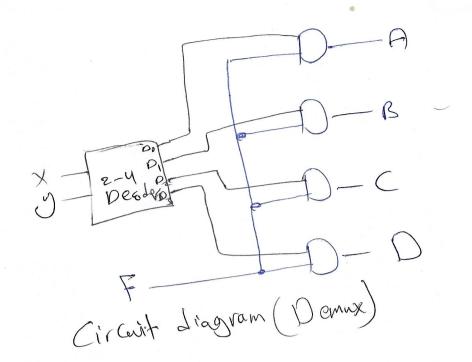

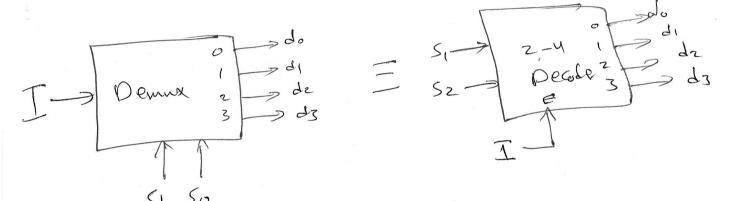

\* Demultiplexer ( Demux)

Demux 1 XY

O O O

B=F

C=F

21 20 D O

D=F

STUDENTS-HUB.com

-38-

\* Demultiplexer = Decoder with Enable

\* Three (Tri) shabe buffer &

X buffer (normal)

Normal buffer

Control (C) If \$== ( (short circuit) else F=Z (open circuit) Three state buffer

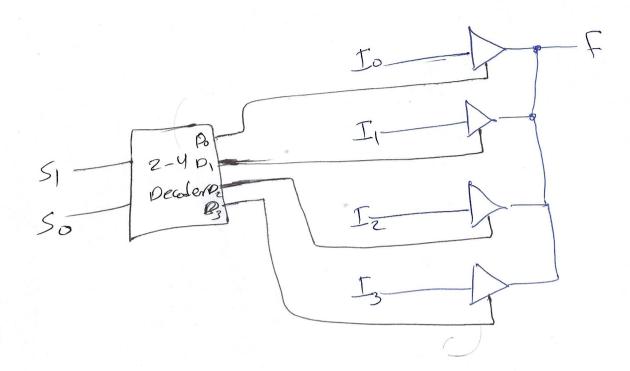

Example & Design a 2XI mux using buffer (Three state)

F= Io

Example & Design a 4-1 Mux using Three state

buffer.