## ANSWER BOOKLET

| Student: | Digital     | Number      | 8    |

|----------|-------------|-------------|------|

| Course:  | Department: | Number:     |      |

|          | Division:   | Instructor: |      |

| Date:    | Day         | Month       | Year |

## For Instructor's Use

| Question | Grade |

|----------|-------|

| 1        |       |

| 2        |       |

| 3        |       |

| 4        |       |

| 5        |       |

| 6        |       |

| 7        |       |

| 8        |       |

| 9        |       |

| 10       |       |

| 11       |       |

| 12       |       |

| Total    |       |

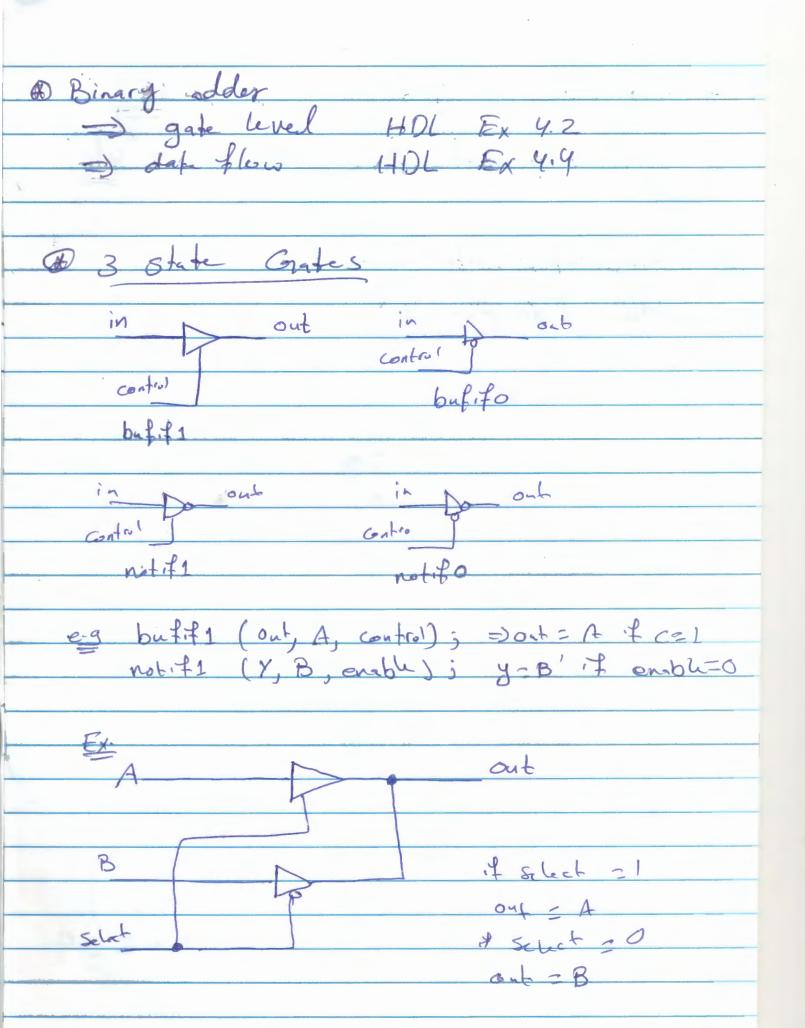

| . * mux (tri) in gate level page 152         |

|----------------------------------------------|

|                                              |

| many vil 11 DI and and of 11/                |

| * mux with data flow HDL example 4-6         |

|                                              |

|                                              |

| # Comparator with data flows HDL Example 4-5 |

| 1101 8 0 116                                 |

| HOL Example 4-5                              |

| -1                                           |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

B, and C and one output theb on gate level HDL to describe this Write a test bench that test, the circuit for all a log file of the regults. Solubiun

prime (A,B,C,y); (e2,e1,B); or 93 (4, e2,c); module test

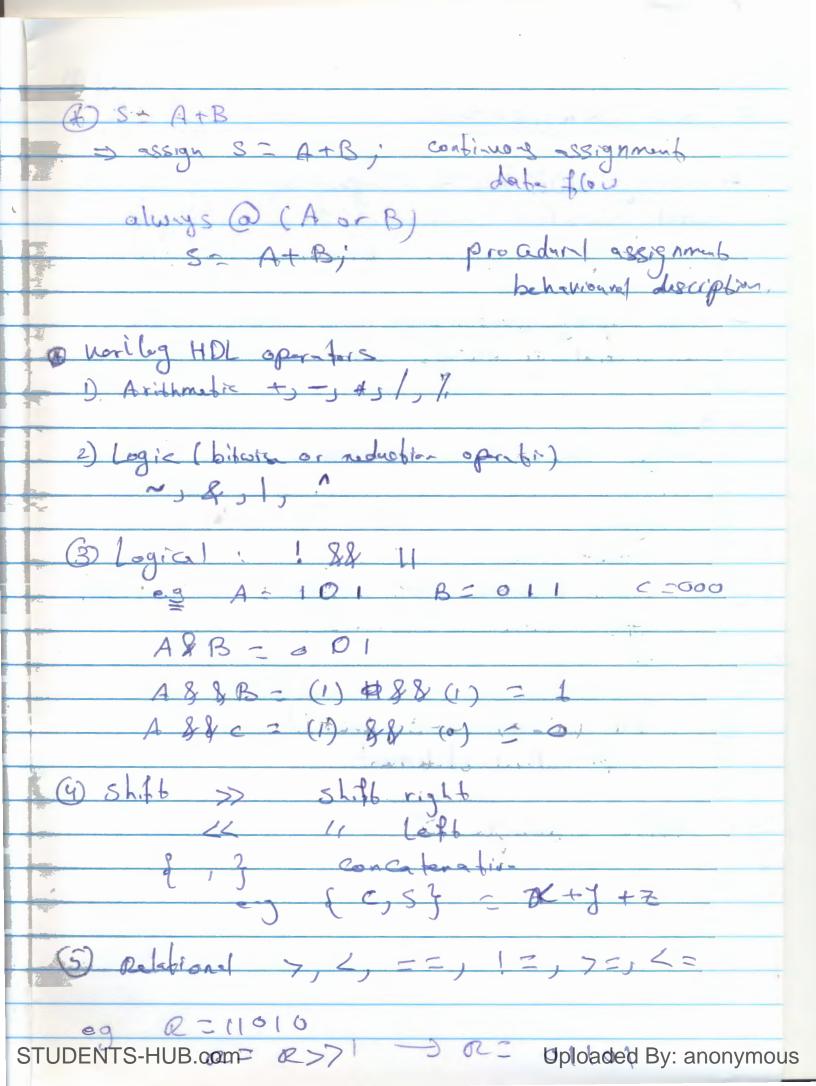

ASTC, PLD and FPGA assign for combinational circuits assign y - AIB (gate circuit) (1) y = A+B (full adder)

(1) y = A-B (1, with xorgatis)

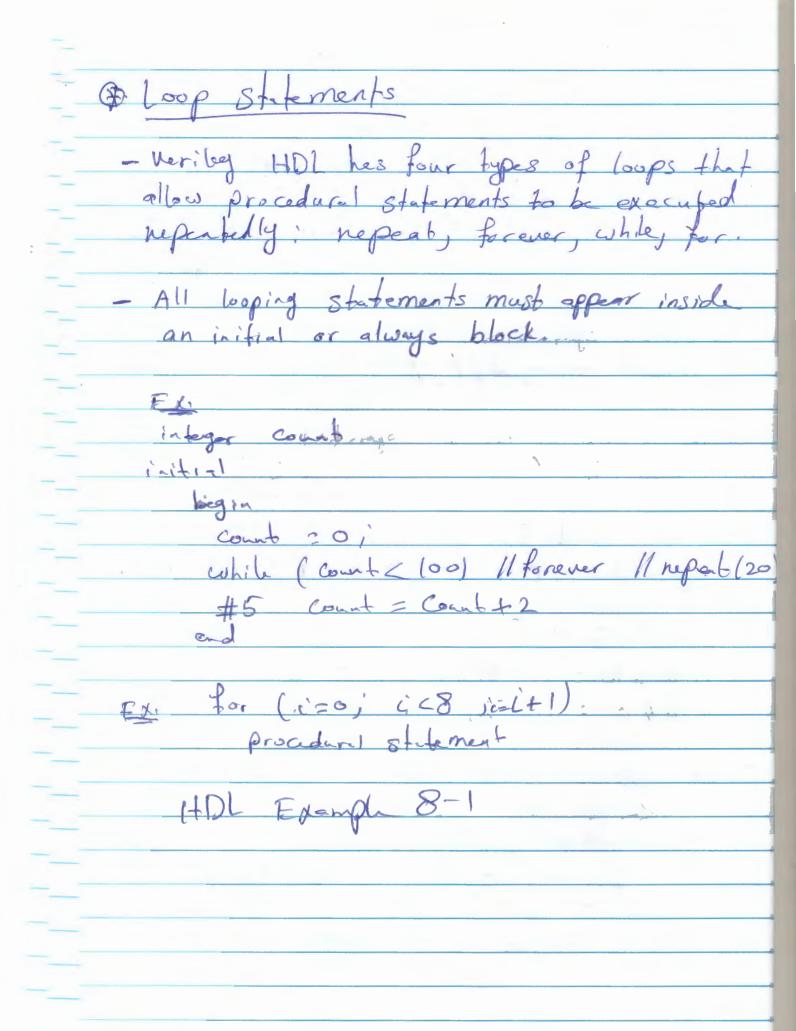

(1) y = 8? PliJo (2x1 mux) - always; for sequential or combinations eg alwys @ (Tror To ors) case strement (large max).