# DEPARTMENT OF COMPUTER SYSTEM ENGINEERING

Digital Integrated Circuits - ENCS333

Dr. Khader Mohammad

Lecture #9 Combinational Circuit

Integrated-Circuit Devices and Modeling

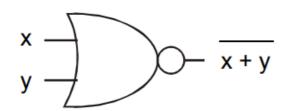

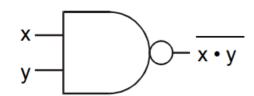

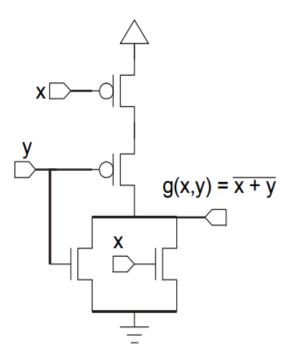

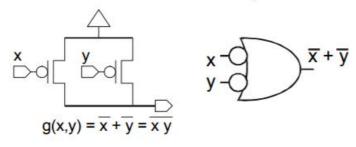

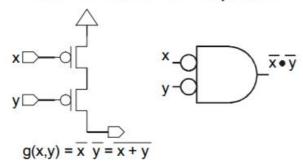

## **CMOS NOR Gate**

NOR Symbol

Karnaugh map

NOR Truth Table

| x y | <u>x+y</u> |

|-----|------------|

| 0 0 | 1          |

| 0 1 | 0          |

| 1 0 | 0          |

| 1 1 | 0          |

$$g(x,y) = \overline{x} \cdot \overline{y} \cdot 1 + x \cdot 0 + y \cdot 0$$

- construct Sum of Products equation with all terms

- each term represents a MOSFET path to the output

- '1' terms are connected to VDD via pMOS

- '0' terms are connected to ground via nMOS

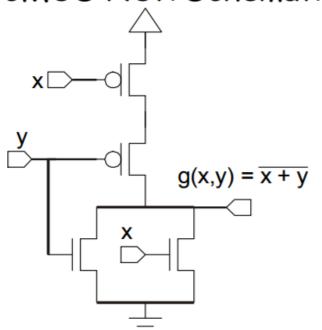

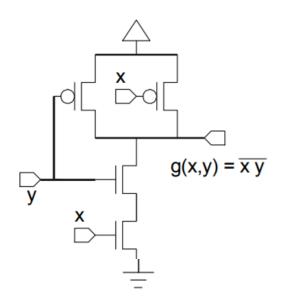

### **CMOS NOR Gate**

CMOS NOR Schematic

$$g(x,y) = \overline{x} \cdot \overline{y} \cdot 1 + x \cdot 0 + y \cdot 0$$

- output is LOW if x OR y is true

- parallel nMOS

- output is HIGH when x AND y are false

- series pMOS

- · Important Points

- series-parallel arrangement

- when nMOS in series, pMOS in parallel, and visa versa

- true for all CMOS logic gates

- allows us to construct more complex logic functions

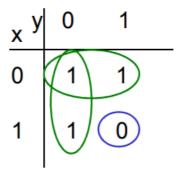

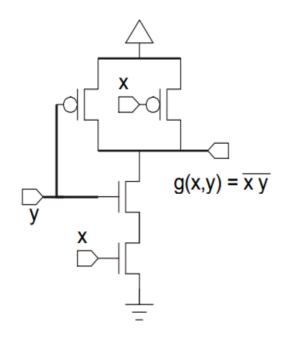

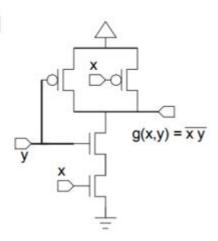

## **CMOS NAND Gate**

NAND Symbol

CMOS Schematic

Truth Table

| x y | $\sqrt{x^{\bullet}y}$ |

|-----|-----------------------|

| 0 ( | 1                     |

| 0 1 | 1 1                   |

| 1 ( | ) 1                   |

| 1 1 | 0                     |

K-map

$$g(x,y) = (\overline{x} \cdot \overline{y} \cdot 1) + (\overline{x} \cdot y \cdot 1) + (x \cdot \overline{y} \cdot 1)$$

$$(x \cdot y \cdot 0)$$

$$= x \cdot y \cdot 0 + \overline{x} \cdot 1 + \overline{y} \cdot 1$$

- output is LOW if x AND y are true

- series nMOS

- output is HIGH when x OR y is false

- parallel pMOS

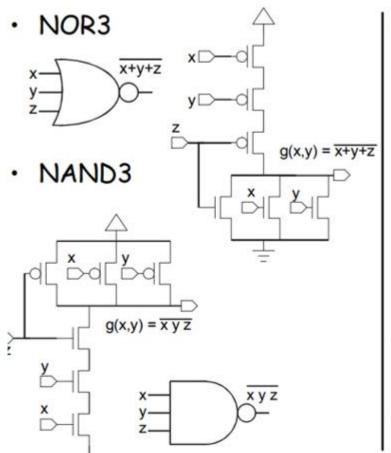

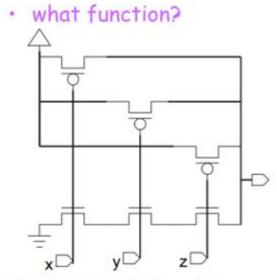

# 3-Input Gates

Alternate Schematic

- note shared gate inputs

- · is input order important?

- · in series, parallel, both?

- schematic resembles how the circuit will look in physical layout

#### Review: CMOS NAND/NOR Gates

NOR Schematic

- output is LOW if x OR y is true

- parallel nMOS

- output is HIGH when x AND y are false

- series pMOS

NAND Schematic

- output is LOW if x AND y are true

- series nMOS

- output is HIGH when x OR y is false

- parallel pMOS

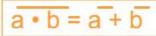

# Complex Combinational Logic

- General logic functions

- for example

$$f = \overline{a \cdot (b + c)}, \quad f = (\overline{d \cdot e}) + a \cdot (\overline{b} + c)$$

- How do we construct the CMOS gate?

- use DeMorgan principles to modify expression

- construct nMOS and pMOS networks

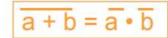

$$a \cdot b = a + b$$

$a + b = a \cdot b$

- use Structured Logic

- AOI (AND OR INV)

- OAI (OR AND INV)

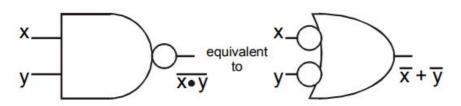

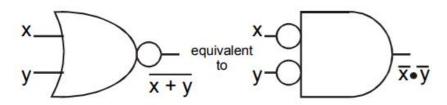

# Using DeMorgan

- DeMorgan Relations

- NAND-OR rule

· bubble pushing illustration

- · bubbles = inversions

- NOR-AND rule

to implement pMOS this way, must push all bubbles to the inputs and remove all NAND/NOR output bubbles

- pMOS and bubble pushing

- Parallel-connected pMOS

- assert-low OR

- creates NAND function

- Series-connected pMOS

- assert-low AND

- creates NOR function

## Rules for Constructing CMOS Gates

#### The Mathematical Method

Given a logic function

$$F = f(a, b, c)$$

- Reduce (using DeMorgan) to eliminate inverted operations

- inverted variables are OK, but not operations (NAND, NOR)

- Form pMOS network by complementing the inputs

$$Fp = f(a, b, c)$$

Form the nMOS network by complementing the output

$$Fn = f(a, b, c) = \overline{F}$$

Construct Fn and Fp using AND/OR series/parallel MOSFET structures

#### **EXAMPLE**:

$$F = \overline{ab} \Rightarrow$$

$Fp = \overline{ab} = a+b;$  OR/parallel

$Fn = \overline{ab} = ab;$  AND/series

complementary p-channel

network

n-channel network

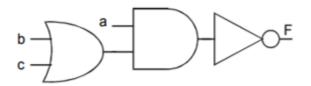

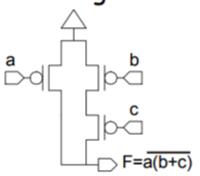

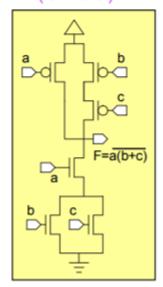

#### CMOS Combinational Logic Example

Construct a CMOS logic gate to implement the function:

$$F = \overline{a \cdot (b + c)}$$

14 transistors (cascaded gates)

- pMOS

- Apply DeMorgan expansions

$$F = \overline{a} + (\overline{b} + \overline{c})$$

$F = \overline{a} + (\overline{b} \cdot \overline{c})$

- Invert inputs for pMOSFp = a + (b · c)

- Resulting Schematic

6 transistors (CMOS)

- · nMOS

- Invert output for nMOSFn = a · (b + c)

- Apply DeMorgan none needed

- Resulting Schematic

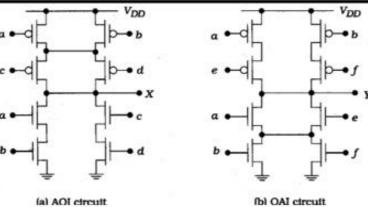

# Structured Logic

- Recall CMOS is inherently Inverting logic

- Can use structured circuits to implement general logic functions

- AOI: implements logic function in the order AND, OR, NOT (Invert)

- Example: F = a · b + c · d

- operation order: i) a AND b, c AND d, ii) (ab) OR (cd), iii) NOT

- Inverted <u>Sum-of-Products</u> (SOP) form

- OAI: implements logic function in the order OR, AND, NOT (Invert)

- Example:  $G = (x+y) \cdot (z+w)$

- · operation order: i) x OR y, z OR w, ii) (x+y) AND (z+w), iii) NOT

- Inverted Product-of-Sums (POS) form

Use a structured CMOS array to realize such functions

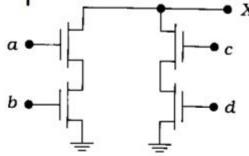

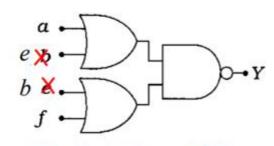

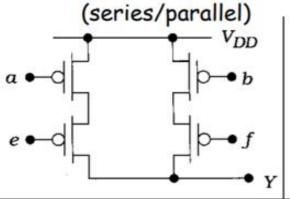

## AOI/OAI nMOS Circuits

· nMOS AOI structure

$$F = a \cdot b + c \cdot d$$

- series txs in parallel

- nMOS OAI structure

- series of parallel txs

$$F = (a + e) \cdot (b + f)$$

error in textbook Figure 2.45

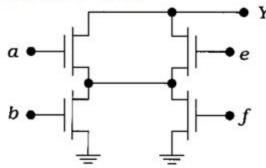

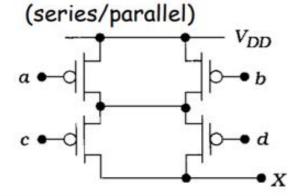

# AOI/OAI pMOS Circuits

- pMOS AOI structure

- series of parallel txs

- opposite of nMOS

- pMOS OAI structure

- series txs in parallel

- opposite of nMOS

Complete CMOS

AOI/OAI circuits

# Implementing Logic in CMOS

- Reducing Logic Functions

- fewest operations ⇒ fewest txs

- minimized function to eliminate txs

```

- Example: x y + x z + x v = x (y + z + v)

5 operations: 3 operations: 1 AND, 2 OR

# txs = # txs =

```

- Suggested approach to implement a CMOS logic function

- create nMOS network

- invert output

- reduce function, use DeMorgan to eliminate NANDs/NORs

- implement using series for AND and parallel for OR

- create pMOS network

- complement each operation in nMOS network

- i.e. make parallel into series and visa versa

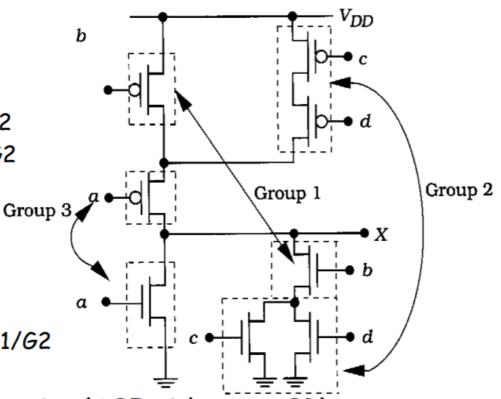

# CMOS Logic Example

Construct the function below in CMOS

$F = a + b \cdot (c + d)$ ; remember AND operations occur before OR

$Fn = a + b \cdot (c + d)$

- nMOS

- Group 2: c & d in parallel

- Group 1: b in series with G2

- Group 3: a parallel to G1/G2

- pMOS

- Group 2: c & d in series

- Group 1: b parallel to G2

- Group 3: a in series with G1/G2

Circuit has an OAOI organization (AOI with extra OR)

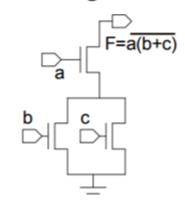

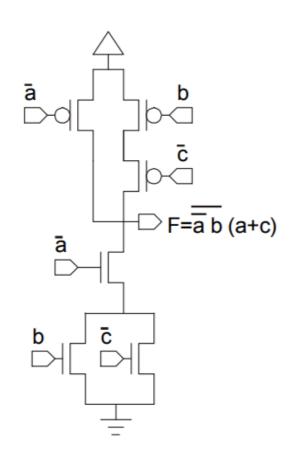

## Another Combinational Logic Example

Construct a CMOS logic gate which implements the function:

$$F = \overline{a \cdot (b + c)}$$

- pMOS

- Apply DeMorgan expansions none needed

- Invert inputs for pMOS  $Fp = a \cdot (\overline{b} + c)$

- Resulting Schematic?

- nMOS

- Inver<u>t output</u> for nMOS Fn =  $a \cdot (b + c)$

- Apply De<u>Morg</u>an Fn = a + (b+<del>c</del>) Fn = a + (b · c)

- Resulting Schematic?

#### Another Combinational Logic Example

Implement the function below by constructing the nMOS network and complementing operations for the pMOS:

$$F = \overline{a \cdot b} \cdot (a + c)$$

- nMOS

- Invert Output

• Fn =

$$\overline{a \cdot b} \cdot (a + c) = \overline{a \cdot b} + (a + c)$$

- Eliminate NANDs and NORs

• Fn =

$$\overline{a}$$

• b +  $(\overline{a}$  •  $\overline{c})$

- Reduce Function

• Fn =

$$\overline{a}$$

· (b +  $\overline{c}$ )

- Resulting Schematic?

- Complement operations for pMOS

• Fp =

$$\overline{a}$$

+ (b •  $\overline{c}$ )

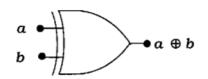

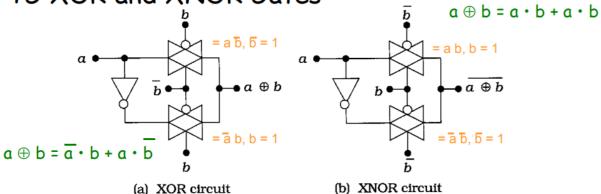

## XOR and XNOR

- Exclusive-OR (XOR)

- $-a \oplus b = \overline{a} \cdot b + a \cdot b$

- not AOI form

| а | b | a ⊕ b |  |

|---|---|-------|--|

| 0 | 0 | 0     |  |

| 0 | 1 | 1     |  |

| 1 | 0 | 1     |  |

| 1 | 1 | 0     |  |

- Exclusive-NOR

- $-\overline{a \oplus b} = a \cdot b + \overline{a} \cdot \overline{b}$

- inverse of XOR

- XOR/XNOR in AOI form

- XOR:  $a \oplus b = a \cdot b + a \cdot \overline{b}$ , formed by complementing XNOR above

- XNOR:  $\overline{a \oplus b} = \overline{a \cdot b} + a \cdot \overline{b}$ , formed by complementing XOR

thus, interchanging a and  $\overline{a}$  (or b and  $\overline{b}$ ) converts from XOR to XNOR

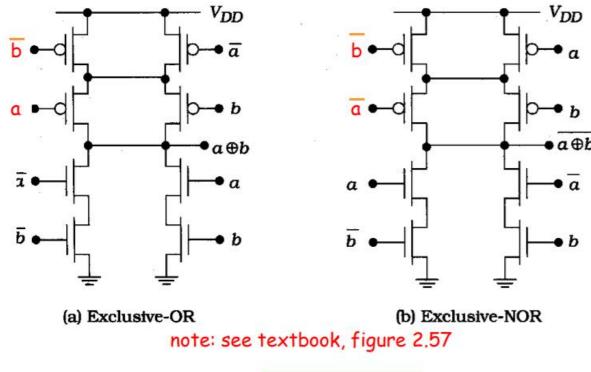

### XOR and XNOR AOI Schematic

-XOR:

$$a \oplus b = \overline{a \cdot b + \overline{a \cdot b}}$$

-XNOR:

$$\overline{a \oplus b} = \overline{a \cdot b + a \cdot \overline{b}}$$

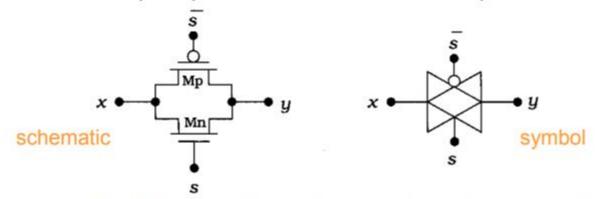

### **CMOS Transmission Gates**

Function

- recall: pMOS passes a good '1' and nMOS passes a good '0'

- gated switch, capable of passing both '1' and '0'

- Formed by a parallel nMOS and pMOS tx

- Controlled by gate select signals, s and  $\overline{s}$

- if s = 1, y = x, switch is closed, txs are on

- if s = 0, y = unknown (high impedance), y = x s, for s=1 switch open, txs off

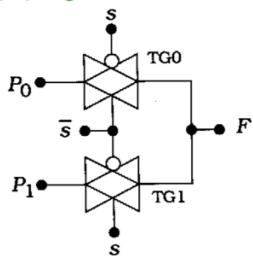

#### Transmission Gate Logic Functions

- TG circuits used extensively in CMOS

- good switch, can pass full range of voltage (VDD-ground)

- 2-to-1 MUX using TGs

$$F = Po \cdot \overline{s} + P1 \cdot s$$

| s | TG0 TG1     | F     |

|---|-------------|-------|

| 0 | Closed Open | $P_0$ |

| 1 | Open Closed | $P_1$ |

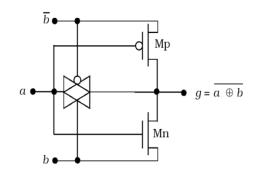

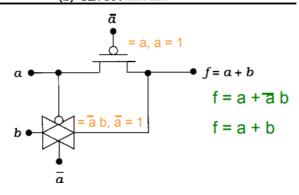

### More TG Functions

TG XOR and XNOR Gates

- Using TGs instead of "static CMOS"

- TG OR gate

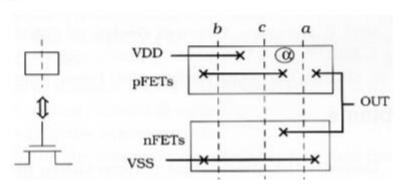

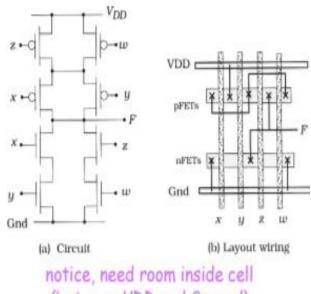

# Structured Layout

#### General Approach

- power rails

- horizontal Active

- vertical Poly (inputs from top/bottom)

- Metal1 connects nodes as needed in schematic

- Structured Layout

- AOI circuit figure

- useful for many logic functions

- see examples in textbook

- Disadvantages

- not optimized for speed

- large S/D regions = higher

#### capacitance

- interconnect paths could be shorter

- not optimized for area/size

notice, need room inside cell (between VDD and Ground) to route internal connections

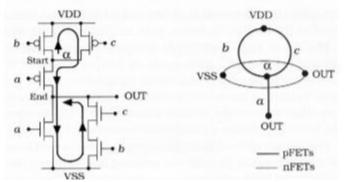

# **Euler Graphs**

- Euler Graph

- method for determining what order to layout txs

- assign each circuit node as a point

- assign each tx as a line between points

- Method

- locate starting point

- trace a loop from starting point through each transistor

- can only re-cross a point once, separate nMOS loop must cross each pMOS

- if above is possible, all tx can be in same Active

- if not, will require multiple Active regions