# Digital Systems ENCS2340 Chapters(1-5) قال تعالى "إِنْ أَحْسَنتُمْ أَحْسَنتُمْ لاَنِفُسِكُمْ فَوَإِنْ أَسَأْتُمٌ فَلَهَا <sup>""</sup>

STUDENTS-HUB.com

Popular Number Systems:

Binary:

Base (radix)=2

Ewo digit Values: O and I

humbers represented as Zeros and ones.

- · Base (vadix) = 8

- eight values: 0,1,2 .... 7.

• التوبل بين ectal,Binary • • Hexa,Binary سطل لانهم عبارة عن (z) مرفوعية لقوَّة.

### -> Hexadecimal:

- Base (vadix) = 16

- · sixteen values= 0,1,2 · -- 9, A --- F.

- · A=10, B= 11, C=12, D= 13, E= 14, F=15.

#### ----> Decimali

- Base (radix) = 10.

- Ten Values = 0,1 \_ \_ 9,

· Binary (Octal, Hexadecimal :

• من الـ (25B) كل 3 منازل Binary = منزلة (25B) • Hexa من الـ (25B) كل 4 منازل Binary = منزلة (25B)

Example: Convert 32 - bit number into octal and Hexa:

most 3 5 3 0 5 5 2 3 6 2 4 reast

STUDENTS-HUB.com

Pillo, bil, ool, allo bil bil bil doo

$$E = B + 6 + 7 + 9 + 14xa$$

Example: (3 B A 4),  $B \rightarrow ($  ).

$3x16^{3} + 11x16^{2} + 10x16^{4} + 9x16^{6} - (15269)a$

$(7204)_{B} \rightarrow ($  ).

$7x8^{2} + 2x8^{2} + 0x8^{2} + 4x8^{9} = 3716$

$(422)_{10} \rightarrow (1A6) 16$

$422/16 - 26 - 6$

$26/16 + 4 + 7$

$11/16 - a + 7$

$11/16 - 3 + 7$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 + 17$

$11/16 - 3 +$

-> what is the largest value using 3 digits in radix

$$r$$

?

$(111)_2 = 2^3 - 1$

$(777)_8 = 8^3 - 1$  (radik=r)  $r$  (radik=2) (radik=2)  $r$ ,

$(qqq)_{10} = 10^3 - 1$  (radik=r)  $r^n - 1 = 1$

• Representing Fractions:

Example:

$$(2409.87)_{10}$$

$2x_{10}^{3} + 4x_{10}^{2} + 0x_{10}^{1} + 9x_{10}^{1} + 8x_{10}^{1} + 7x_{10}^{2}$

18 200 - 10 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 2000 - 20000 - 2000 - 2

· converting Decimal Fraction to Binary:

Example: Convert 0.6875 to radix 2:

· Fractions Ji is (Hexa, Binary) (Octal, Binary) in integritions )

STUDENTS-HUB.com

Example: Convert 32 Binary bit to octal.

-> what is the largest fraction value if m Fraction digit is used in radix r?

in general 1-m<sup>-n</sup> -> How many Fraction values exist with m fraction bit ? Binary -> 2<sup>m</sup> . (res ) Taistan I want to change the construction

# Daminished radix complement: Complement = Largest number - N

Example: 9's complement of 546700 = (10-1) complement

999999 - 546700 = 453299

العفر = l's complement of 1011 000 = العفر واحد والولحم

1))(1)1 - 10(1000 = 0100())

STUDENTS-HUB.com

Uploaded By: Ahmad K Hamdan

صغر .

9's complement

$$\begin{array}{c} 72532\\ 9's complement \\ 9's complem$$

• في ال لمعنق الل عان ال علم من حيف لغاية (١-٣٣) هستًا ال Range رج بيفتس لسالي و موجب

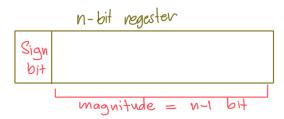

Disign magnitude Representation:

• إذا بدِّي أُمثَل الرُّقم في (tid-n) المقدار بمُله في (tid 1-n) وtid 1 جدر النَّامَة الرقم. الرقم.

Uploaded By: Ahmad K Hamdan

STUDENTS-HUB.com

-regative weight for MSB:

$$-128 \quad 64 \quad 32 \quad 16 \quad 8 \quad 4 \quad 21$$

$$-128 + 32 + 16 + 4 = -76$$

· Rounes of unsigned / signed Tutegers:

STUDENTS-HUB.com

$\rightarrow$  for n bit unsigned integenes: Range is 0 to (2<sup>n</sup>-1) -) for n-bit signed Integenes: Range is -2<sup>n-1</sup> 20 2<sup>n-1</sup>-1 -> Positive integers: 0 20 21-1-1 - negative integeres: -2" 20 -1

· Arithmetic Addition:

م اذا جمع عبدين ولحد منفم سالب (مممونات) ولحلج مع يسمه بهمله. إذا جمع عبدين (tidn) ولايج الجواب للفا (الحمل) بكون المحال المعن منفيين (tidn) ولايج الجواب للفا المعن المحمد إذا جمع عددين موجب (اخو tid = 0) إذا جمع عددين سالب (اخو tid = 1) و طلع الجواب سالب (آخر tid = 1) و طلع الجواب موجب (آخر tid = 0) رجني في worflow.

• بسكل عام عشان أعوى في سط معهم أو لا يتحل (XOR) بين آخر (z carry) .

STUDENTS-HUB.com

Example :

. -

• cawy = 1

• cawy = 1

• overflow = 0

$$| \oplus | = 0$$

1

STUDENTS-HUB.com

|      | 0110 | 0110 | 0110 | Ŧ |

|------|------|------|------|---|

| 0100 | 000  | 0000 | 0010 |   |

| Ч    | 8    | 0    | 2    |   |

| 3      | 0011 | 0011  | 1001                | 0 0 0  | 0110  |

|--------|------|-------|---------------------|--------|-------|

| 4      | 0100 | 000   | 20100               | 0 \ 00 | 0 [1] |

| 5      | 0101 | 1000  | 1010 lemen          | 1011   | 1000  |

| б      | 0110 | (00 ( | 00//00<br>6000 (10) | 1010   | 1001  |

| 7      | 0111 | 1000  | 0 110               | 1001   | 1010  |

| 8      | 1000 | 101   | L (110              | 000    | (011) |

| 9      | 1001 | 1100  | 1111                | [11]   | 1100  |

| unused |      |       |                     |        |       |

|        |      |       |                     |        |       |

• Self complementing codes: Code الحدث complements وجنت التا الحدث عفس الر abo مح يحونوا منسم بالر 3-exess و 1-2-24

STUDENTS-HUB.com

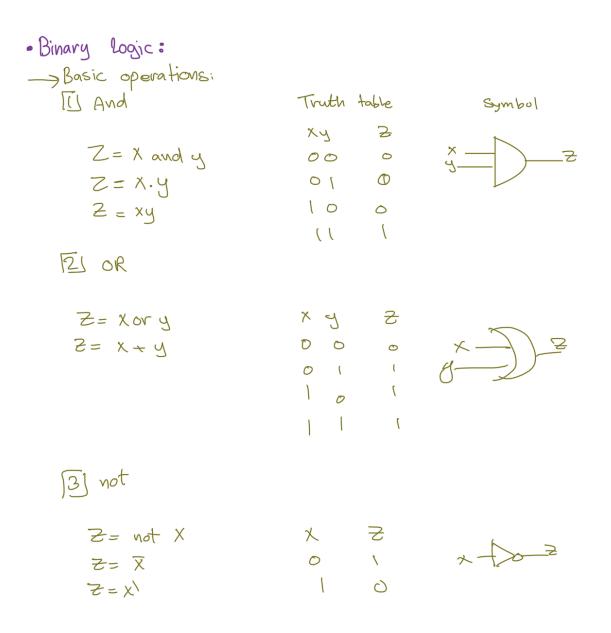

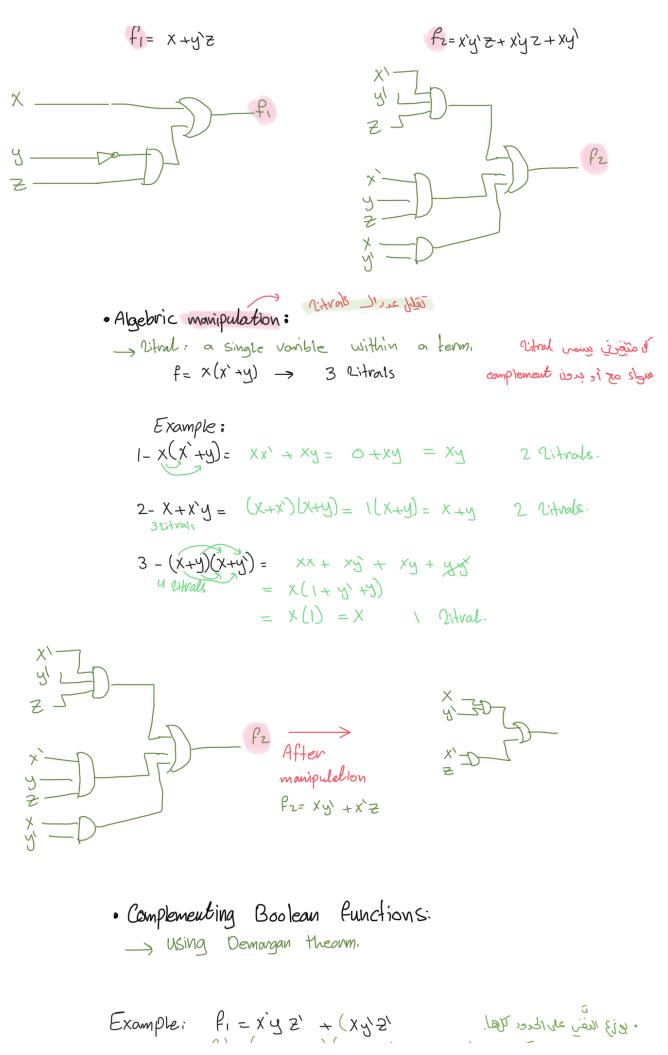

## Chapter [2]: Boolean Algebra and Logic gates:

#### **Basic Theorems**

| Postulate 2               | (a) | x + 0 = x                 | (b) | $x \cdot 1 = x$         |

|---------------------------|-----|---------------------------|-----|-------------------------|

| Postulate 5               | (a) | x + x' = 1                | (b) | $x \cdot x' = 0$        |

| Theorem 1                 | (a) | x + x = x                 | (b) | $x \cdot x = x$         |

| Theorem 2                 | (a) | x + 1 = 1                 | (b) | $x \cdot 0 = 0$         |

| Theorem 3, involution     |     | (x')' = x                 |     |                         |

| Postulate 3, commutative  | (a) | x + y = y + x             | (b) | xy = yx                 |

| Theorem 4, associative    | (a) | x + (y + z) = (x + y) + z | (b) | x(yz) = (xy)z           |

| Postulate 4, distributive | (a) | x(y+z) = xy + xz          | (b) | x + yz = (x + y)(x + z) |

| Theorem 5, DeMorgan       | (a) | (x + y)' = x'y'           | (b) | (xy)' = x' + y'         |

| Theorem 6, absorption     | (a) | x + xy = x                | (b) | x(x + y) = x            |

· Example: Prove Ahat Xy +x'Z + yz = Xy + x'Z.

$$\Rightarrow proof: Xy_{+} x'z_{+} yz$$

starting from the neft side

$$= Xy_{+} x'z_{+} + 1 \cdot yz$$

$yz_{-} = yz_{-1}$

$$= xy_{+} x'z_{+} + (x+x')(yz)$$

$1 = x + x'$

$$= xy_{+} x'z_{+} + x'yz_{+} + x'yz$$

Distributive • Over + ·

$$= xy_{+} + xyz_{+} + x'z_{-} + x'yz$$

associative commutative +

$$= xy_{-1} + xyz_{+} + x'z_{-1} + x'yz$$

$xy_{-} = xy_{-1}$   $x'z_{-} = x'z_{-1}$

$$= xy_{-1} + x'z_{-1} + x'z_{-1} + x'yz$$

$xy_{-} = xy_{-1}$   $x'z_{-} = x'z_{-1}$

$$= xy_{-1} + x'z_{-1} + x'z_{-1} + x'yz$$

$1+z_{-} = 1$   $1+y_{-1}$

$$= xy_{-1} + x'z_{-1} + x'z_{-1}$$

· Duality Principle:

Example: The dual of X(y+z') = X + (yz) The complement doesn't chang.

|              | Property         | Dual Property           |

|--------------|------------------|-------------------------|

| Identity     | x + 0 = x        | $x \cdot 1 = x$         |

| Complement   | x + x' = 1       | $x \cdot x' = 0$        |

| Distributive | x(y+z) = xy + xz | x + yz = (x + y)(x + z) |

• if a property is proven to be true, then its dual is also true.

STUDENTS-HUB.com

· Demorgan's Theorm.

| <b>v</b>                                           |                                       |       | . – |      |     |        |         |            |          |            |               |

|----------------------------------------------------|---------------------------------------|-------|-----|------|-----|--------|---------|------------|----------|------------|---------------|

| (                                                  | (complement) ( wiscolg light ( Ling ) |       |     |      |     |        |         |            |          |            |               |

| $- \frac{(X + Y)}{(X + Y)} = \frac{X' \cdot Y}{Y}$ |                                       |       |     |      |     |        |         | ,<br>San u |          |            |               |

|                                                    | → ()                                  | (7)   |     | X`+  | I,  |        |         |            |          | م_الكن الم |               |

|                                                    |                                       |       |     |      |     | بضوستن | Complem | ون المله   | ہاہ جے ہ | nal lian   | $\rightarrow$ |

|                                                    | 7                                     | Truth | +ab | le : |     |        |         |            |          |            |               |

|                                                    | x                                     | У     | х'  | у'   | x+y | (x+y)' | x'y'    | ху         | (x y)'   | x'+ y'     |               |

|                                                    | 0                                     | 0     | 1   | 1    | 0   | 1      | 1       | 0          | 1        | 1          |               |

|                                                    | 0                                     | 1     | 1   | 0    | 1   | 0      | 0       | 0          | 1        | 1          |               |

|                                                    | 1                                     | 0     | 0   | 1    | 1   | 0      | 0       | 0          | 1        | 1          |               |

|                                                    | 1                                     | 1     | 0   | 0    | 1   | 0      | 0       | 1          | 0        | 0          | J             |

Identical

- · Boolean functions:

- \_\_\_\_ could be described using;

- 1-expression. (Boolean Variables, Boolean constants and Boolean operators) 2-Truth Eable.

Identical

3- logic gates.

Operator precedence:

الحليات حسب الأولوية:

۱- Expressions within parentheses. (د الحليات داخل الأقواس)

2. Not

3. AND.

4. OR.

## .Truth Table:

| A truth table can represent                         |   |   |        |                |

|-----------------------------------------------------|---|---|--------|----------------|

| a Boolean Runction.                                 | x | y | z      | F <sub>1</sub> |

|                                                     | 0 | 0 | 0      | 0              |

| ) list all possible combinations                    | 0 | 0 | 1      | 1              |

| of o's and one's                                    | 0 | 1 | 0      | 0              |

|                                                     | 0 | 1 | 1      | 0              |

| - if a variables them 2 yours                       | 1 | 0 | 0      | 1              |

| -> If IN VANIABLES FREIN 2 VOUS                     |   | 0 |        | 1              |

| C                                                   | 1 | 1 | 0<br>1 | 1              |

| $f_1 = x + y^2 = f_2 = x^2 y^2 = x^2 y^2 = x^2 y^2$ | 1 | 1 | 1      | 1              |

|                                                     |   |   |        |                |

· Circuit diagram

STUDENTS-HUB.com

## Uploaded By: Ahmad K Hamdan

| x          | у | index | Minterm (m)                           | (Maxterm([\/i)  |  |

|------------|---|-------|---------------------------------------|-----------------|--|

| $\bigcirc$ | 0 | 0     | $m_0 = \underline{x}' \underline{y}'$ | $M_0 = x + y$   |  |

| 0          | 1 | 1     | $m_1 = x'y$                           | $M_1 = x + y'$  |  |

| 1          | 0 | 2     | $m_2 = xy'$                           | $M_2 = x' + y$  |  |

| 1          | 1 | 3     | $m_3 = xy$                            | $M_3 = x' + y'$ |  |

· Minterns: And terms, with each variable represented in either Eric or complement Porm.

· Maxterns: OR terms, with each variable represented in either Ence or complement form,

. For a variables there are 2 Maxterms and 2 Minterms.

· minterm is complement of max Zerm.

\*Sum of minterms (<u>SOM</u>), system and product of maxterms (POM) STUDENTS-HUB.com

|                                                                      | , - | - |

|----------------------------------------------------------------------|-----|---|

|                                                                      | 000 | 0 |

| $\rightarrow$ minterms; where function equals $\square$ .            | 001 | 0 |

| $f = m_1 + m_3 + m_5 + m_7$                                          | 010 | 1 |

| f = X'y z' + X'yz + Xy'z + Xyz                                       | 011 | 1 |

| $f = \leq (2,3,5,7)$                                                 | 100 | 0 |

|                                                                      | 101 | 1 |

|                                                                      | 110 | 0 |

| $f = \mathcal{M}_0 + \mathcal{M}_1 + \mathcal{M}_4 + \mathcal{M}_6.$ | 111 | 1 |

|                                                                      |     |   |

f = (X + y + z)(X + y + z)(X + y + z)(X + y + z)(X + y + z)f = TT(0, 1, 1, 1, 6).

Examples:

$$f(a_1b_1c_1d) = TT(1,3,11)$$

$f(a_1b_1c_1d) = TT(1,3,11)$

$f(a_1b_1c_1d) = TT(1,3,11)$

$f(a_1b_1c_1d) = TT(1,3,11)$

$f = (a_1b_1c_1d) = TT(1,3,11)$

- ج في ٥٥١ و ٩٥٢ (٩٥ د ٥٩١) ه الم ال ترم جدي على ال المقران. f= àbcd+àbcd + àbcd + àbcd + àbcd + àbcd + àbcd + àbcd + àbcd

- Conversions between Canonical forms: The Same Boolean Function can be expressed in two ways: → Sum of minterms. → Product of maxterms. To convert between them: → interchange the symbol (≤, TT) → list the missing numbers.

Example: f(a,b,c) = ≤ (1, 3, 7) o-7 interest in gives 3 variables = TT(0,2,4,5,6) o,2,4,5,6 = ction (1, 2, 4) - size this is a size the symbol (2, 1, 3, 7)

STUDENTS-HUB.com

[] interchange the symbol with Some numbers. [] Same symbol and the missing numbers.

Example:

$$f(x_1y_17) = \leq (o_12_13_1S_17)$$

.

$f'(x_yy_17) = \leq (1, 4, 6)$

$f'(x_1y_17) = T(o_12_13_1S_17)$

Example:

$$f(x_{1}y) = x + x'y'$$

$f(y + y') = x' + x'y'$

$f(y + y') + x'y'$

$f(y + y') + x'y'$  (SOM)

$f(y + y') + x'y'$  (SOM)

$f(y + y') + y'y'$  (SOM)

$f(y + y') + y'y'$  (SOM)

$f(y + y') + y'y'$

$f($

- Algebric conversion to (POM): distributive law النّوتين عن طريق ال wairidble ال يبج

Example:

$$f(a,b,c) = (ac' + bc) + a'b'$$

$f(a,b,c) = (ac' + bc + a')(ac'+bc + b')$

$ac'+a' = a'+c = (c'+a' + bc)(c+b' + ac')$

$bc+c' = b+c = (a'+b+c')(a+b'+b)$

$= (1 \circ 1) (o 1 \circ)$

$f(a,b,c) = T(2,8)$

• Standard forms: Verbining ic \_\_ Sum of product. ((1) - or There is in the two two som of product. Uploaded By: Ahmad K Hamdan STUDENTS-HUB.com (الفنى ال Product of Sum, (الفنكثن عجودين) بعد الغنكث به Product of Sum, (الفنى المنتجان Product of Sum, (الفني المنتجان موجودين) بعد المنتجان من مش من المنتجار عدم الخلك في من المنتجار عدم الخل من المنتجار عدم الخل من المنتجار المنتجا المنتجار المنتجار المنتجار المنتجام المنتجام المنتجام المنتجار المنتجام المنتجان المنتجام المنا المنجام الم

Example:

$$f = A'B'c + AB'c' + AB'c + AB'c + AB'c + AB'c' + AB'c' + AB'c' + AB'c' + AB'c' + AB'c' (SOM)$$

(POS) The second second of the second second second second second to the second secon

STUDENTS-HUB.com

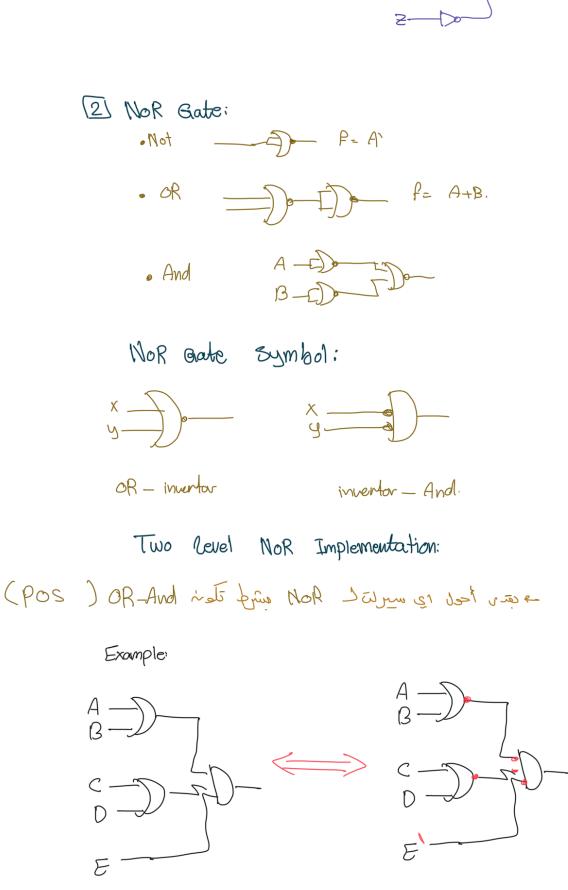

[2] Nor gate: (not OR)

| 2 symbols for non gate; |    |                    |

|-------------------------|----|--------------------|

| 6                       | xу | nor                |

| ×                       | 00 | ι                  |

| 3-20-                   | 01 | 6                  |

|                         | 10 | 0<br>0<br>1<br>Nov |

| ×                       | 11 | ٥                  |

|                         |    |                    |

| [3] XOR Gate:                 |            | ]   |

|-------------------------------|------------|-----|

| * D                           | X Y<br>0 0 | XOR |

| Symbol; y <sup>t</sup> →))X⊕y | 0 0        | 6   |

|                               | 0          | l   |

|                               | 10         | l   |

|                               | 1          | 0   |

|                               |            |     |

| [4] X NOR Gate:               |            |     |

|        | 10                      | хy         | XNOR         |

|--------|-------------------------|------------|--------------|

| Symbol | $(X \oplus Y)^{\prime}$ | 6 <i>Q</i> | $\backslash$ |

|        |                         | 0 \        | 0            |

|        |                         | ) 0        | Ø            |

|        |                         | ()         | 1            |

STUDENTS-HUB.com

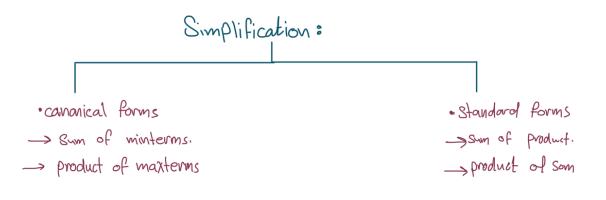

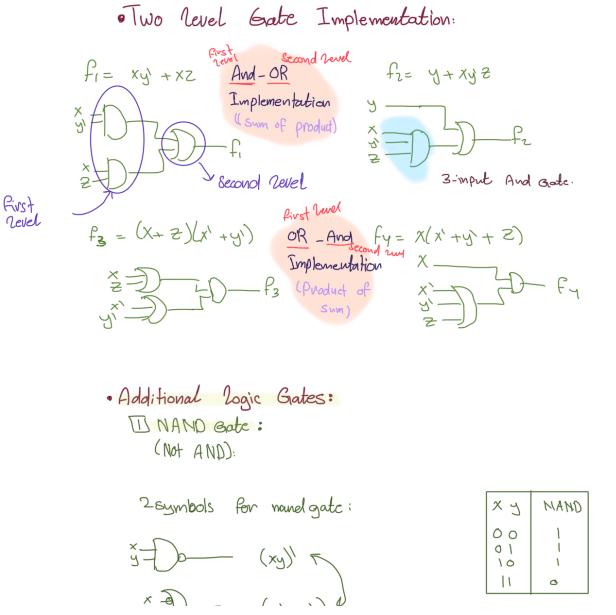

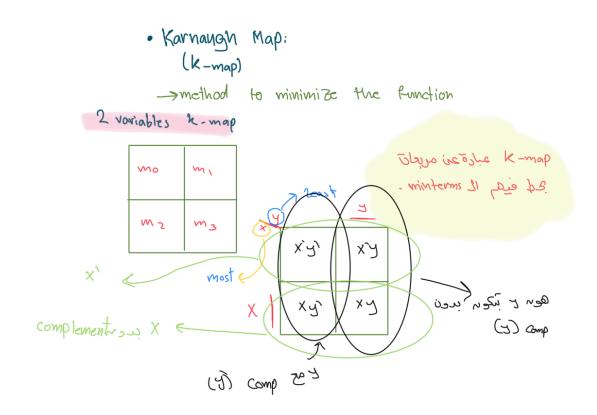

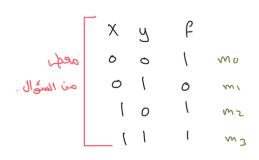

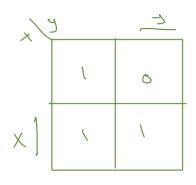

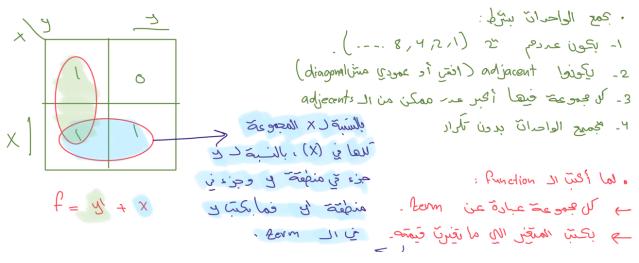

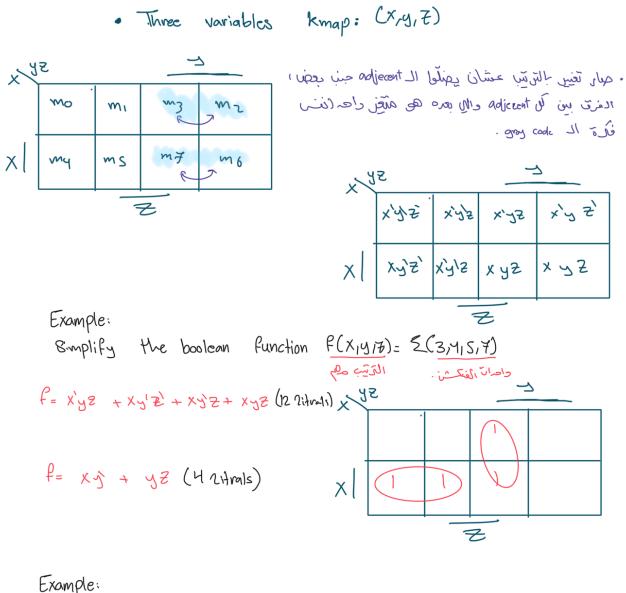

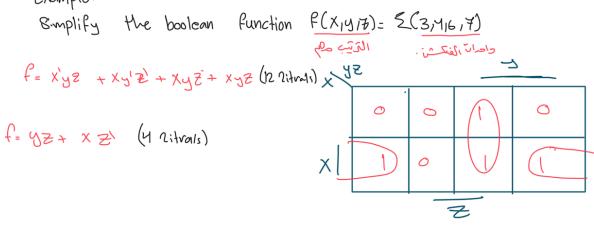

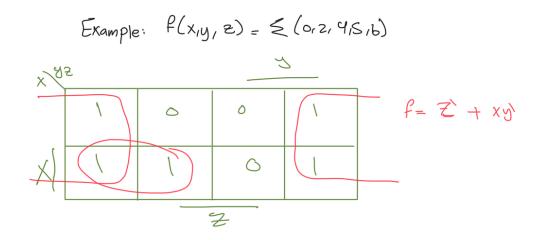

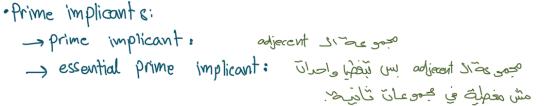

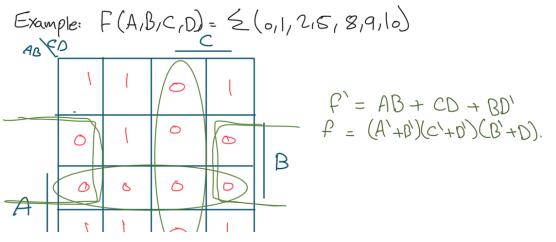

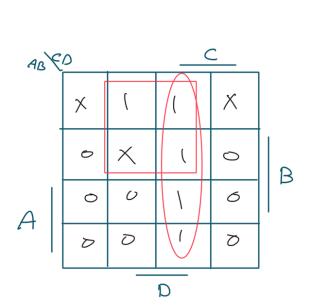

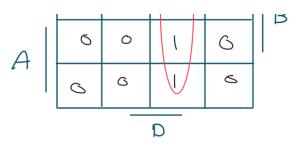

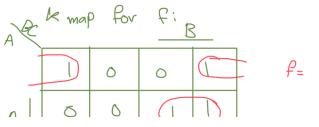

Chapter 31: Gate - Level minimization:

Example :

STUDENTS-HUB.com

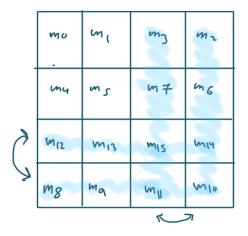

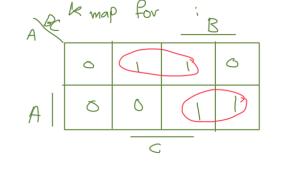

(الزمايا عبارة عن Adjacnt (بقد أ دخرم بنغب المجموعة)

STUDENTS-HUB.com

اذا أخدت مجموعة فيها لكا واحدان، اليترع بكوم فيه establis . اذا أخدت مجموعة فيها لكا واحدان، اليترع بكوم فيه establis 0 . ( يَتَوَم فَيْمَة ( الله عُ

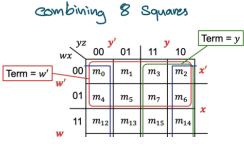

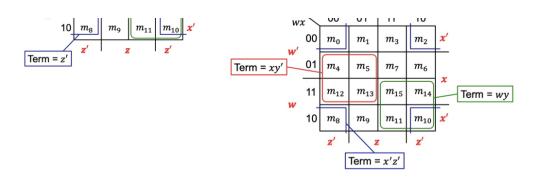

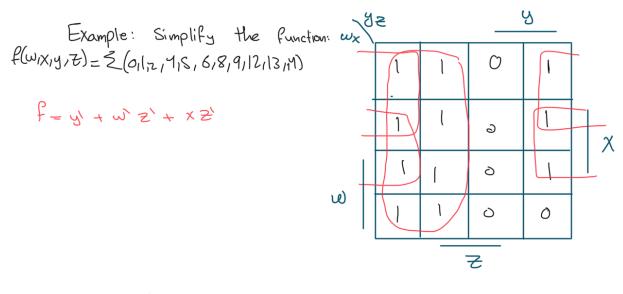

· Y variables Rmap Si is .

STUDENTS-HUB.com

Uploaded By: Ahmad K Hamdan

4 Squares.

combining

Uploaded By: Ahmad K Hamdan

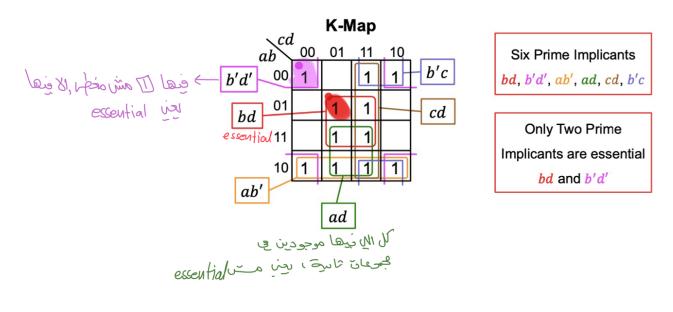

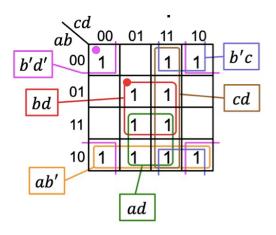

K-Map

STUDENTS-HUB.com

| ∟บนเ µบรอเมเ <del>ย</del> อบเนแบเเอ. |

|--------------------------------------|

| f = bd + b'd' + cd + ad              |

| f = bd + b'd' + cd + ab'             |

| f = bd + b'd' + b'c + ab'            |

| f = bd + b'd' + b'c + ad             |

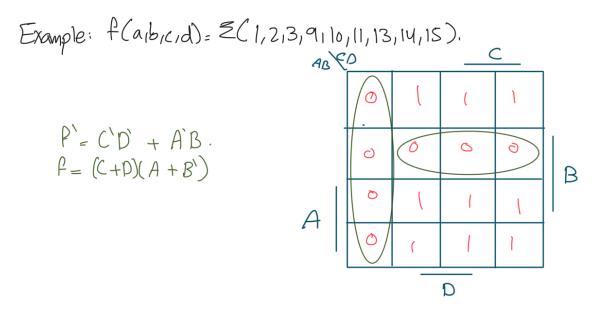

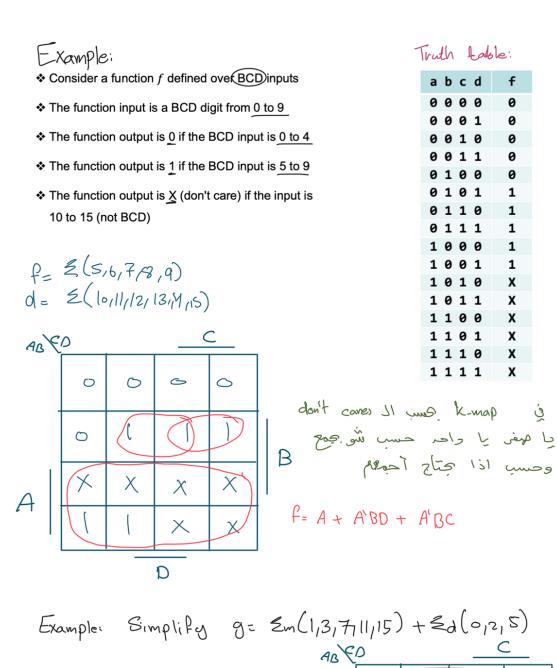

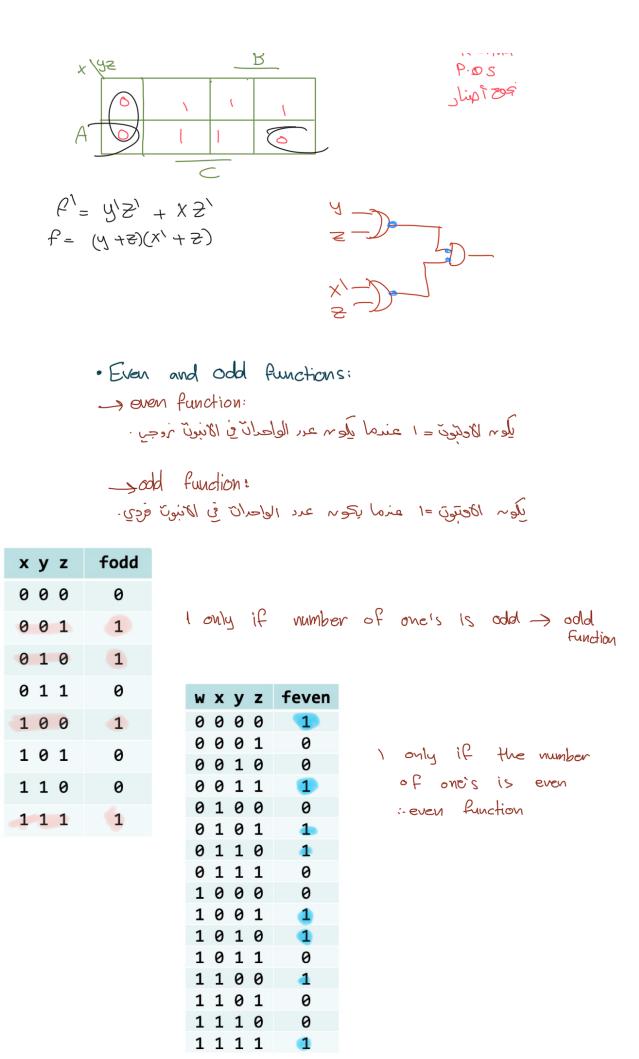

· Product of sum simplification.

. Sum of product جميني simplified Function بجبيغة K-map I. Land i product of Sum بجديغة product of Sum نافنكش بس بجديغة i product of Sum بجديغة بحون i product of Sum بجديفة (F as sop i product of Sum بجديفة بحون i complement بحق i complement لناج عستار أوطل ل

STUDENTS-HUB.com

، في حاليس لا يعده took : ١- يكوم الانبون عده took ع يعني مض ممكن بكوم أدتبون موجع -٢- يكون الارتون عده took ع يعني آوتين عني مترقع . مكام الرعده took بخط X ومعنا ع ممكن أحطها ا To O

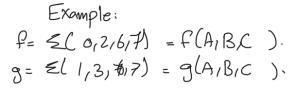

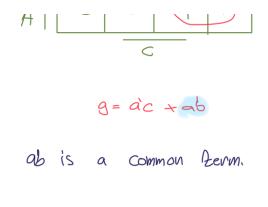

First solution: g= cd + A'B'

g= Cd + H'B

STUDENTS-HUB.com

Uploaded By: Ahmad K Hamdan

χ

X ( (

Second selution = g = cd + a'd

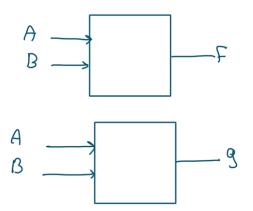

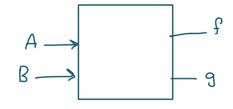

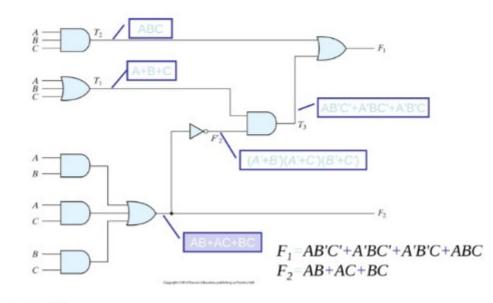

· Muttiple outputs -, Same in puts, with different outputs.

2 Separat circuits

one circuit with Two outputs

->minimize each Runction Separatly:

STUDENTS-HUB.com

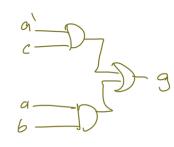

f = a'c' + ab

· Using Common Term (one circuit)

f:

C1

Ø

P

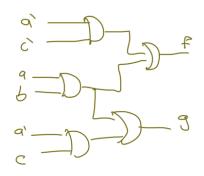

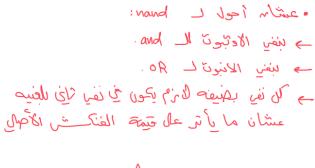

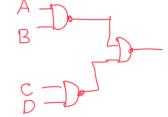

[] Nand Bate:  $A \longrightarrow f = A$ e not

8

$\left[ \right]$

[2]

Nand Gate Symbol:

invertor - And.

STUDENTS-HUB.com

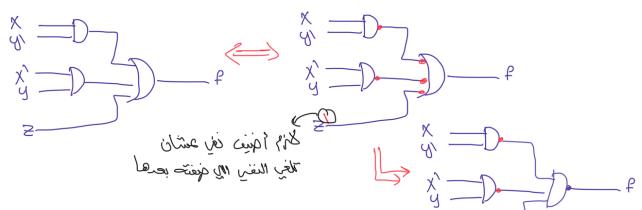

Two Level Nand Implementation: (Sop) And - OR is fing wind Jan of is in the (Sop)

Example:

STUDENTS-HUB.com

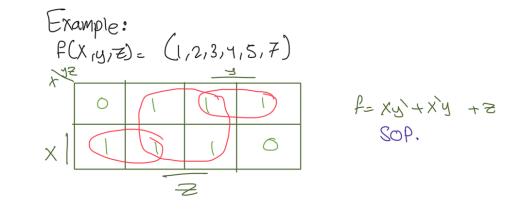

Example: F= Z(1,2,3,5,7) Implement using NoR Bates: OR - And

STUDENTS-HUB.com

STUDENTS-HUB.com

-

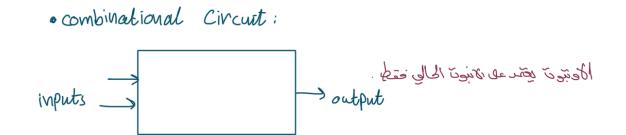

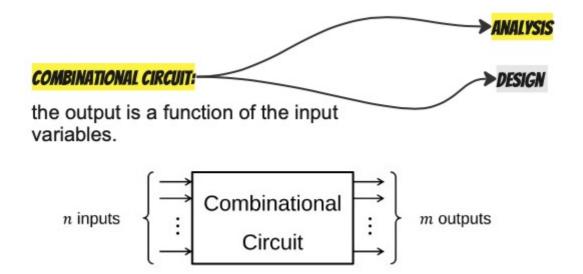

# : CHAPTER 4 COMBINATIONAL LOGIC DESIGN قال تعالى:"إِنْ أَحْسَنتُمْ أَحْسَنتُمْ لِأَنفُسِكُمْ <sup>ل</sup>َّ وَإِنْ أَسَاتُمُ فَلَهَا"

## إيمان الغلبان.

STUDENTS-HUB.com

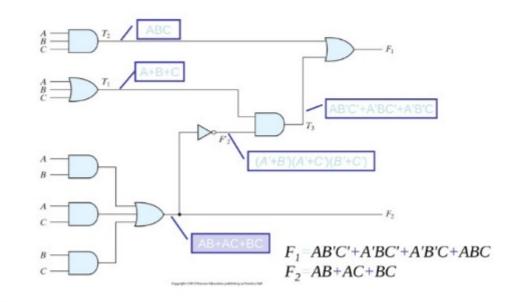

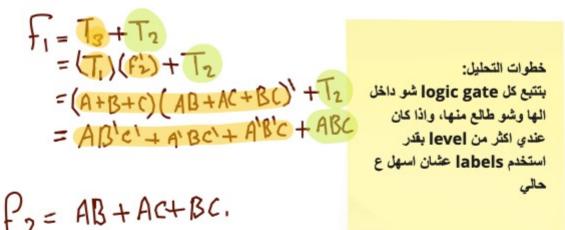

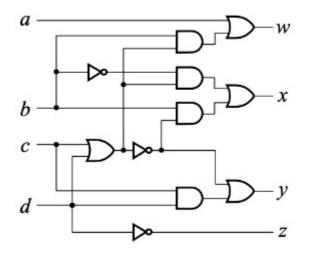

### ANALYSIS:

given a circuit, find out the function.

## DESIGN:

given a function, find out the circuit

القسم الثاني هو ،design بتكون functionالـ موجود، وانا بطلع circuit،

ينقسم التشابتر الى قسمين، القسم الاول هو ،analysis بتكون الدارة موجودة، وانا بطلع function،

ممکن اطلعه ع شکل اکسیرشن، او تروث تیبل

Uploaded By: Ahmad K Hamdan

عشان اطلع الـ simplified expression بقدر اسوي اول اشي الـ truth table وبعدين -<u>k</u> map واوصل بالاخر للـ expression

Upload BACAARTEK Hamdan

#### خطوات التصميم:

افهم شو وصف السيركت المطلوب. ٢- احدد الاوتيوت والانبوت وشو عددهم.

۲- احدد اللوجيك اللي بدي امشي عليه.

map - تروث تيبل و k ٥- اصمم السير كت حسب الفتكشن اللي

طلع معي.

٦- اتحقق من السيركت اذا شغالة صبح

Designing a BCD to Excess-3 Code Converter · 4 Bif input · Range = (0-9) . 4 Bit output · Excess-3 =

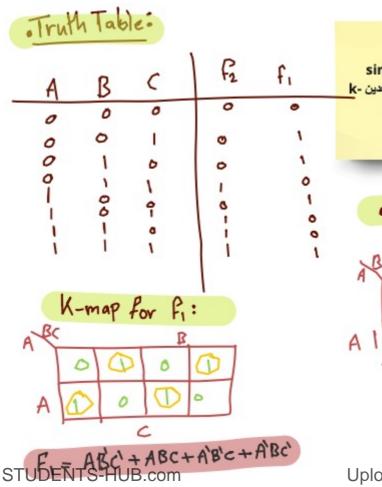

## .Truth Table:

| BCD          | Excess-3 | K-map for each output.                                                                                                                             |

|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| abcd         | w x y z  | K-map for w K-map for x K-map for y K-map for z                                                                                                    |

| 0000         | 0011     | 00 01 11 10 00 01 11 10 00 01 11 10 00 0                                                                                                           |

| 0001         | 0100     |                                                                                                                                                    |

| 0010         | 0101     | 01 1 1 1 1 1 1                                                                                                                                     |

| 0011         | 0110     | 11 X X X X X X X X X X X X X X X X X                                                                                                               |

|              |          | 10 1 1 X X 1 X 1 X X 1 X X                                                                                                                         |

| 0100         | 0111     | Minimal Sum-of-Product expressions:                                                                                                                |

| 0101         | 1000     | w = a + bc + bd, $x = b'c + b'd + bc'd'$ , $y = cd + c'd'$ , $z = d'$                                                                              |

| 0110         | 1001     |                                                                                                                                                    |

| 0111         | 1010     | · extract common term (c+d).                                                                                                                       |

| 1000         | 1011     | $w = a + b (c + d) \qquad $ |

| 1001         | 1100     | $X = b'(c+d) + b(c+d)' \qquad Z = d'$                                                                                                              |

| 1010 to 1111 | хххх     |                                                                                                                                                    |

Binary + 3.

Uploaded By: Ahmad K Hamdan

**Hierarchical Design**

يعنى استخدم دارات بسيطة عشان اوصل دارات معقدة

### BINARY ADDER-SUBTRACTOR

عشان اوصل لدارة تجمعلي او تطرحلي n bits انا بحاجة لدارة ابسط تجمع او تطرح bit 1

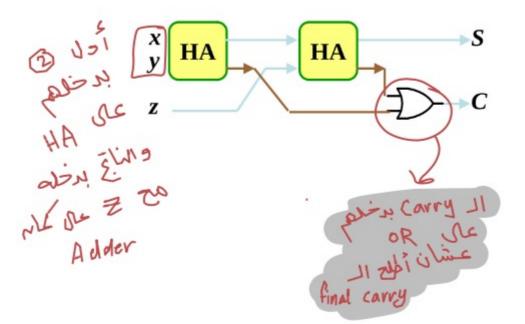

### Half Adder

- ♦ Adds 1-bit plus 1-bit → inputs.

- ♦ Produces Sum and Carry

| ху  | C S |

|-----|-----|

| 0 0 | 0 0 |

| 0 1 | 0 1 |

| 10  | 0 1 |

| 11  | 1 0 |

| x |               |

|---|---------------|

| y | L<br>L<br>D→c |

ontput

\* مالا حظرت: جعد الـ Bits في الاوتبون = عدد الـ Bit في الانبون +1

STUDENTS-HUB.com

Hierarchical Design

full adder:

۵۰ متر المتحد السام السلط

۹۰ مسل سيركن باتجمع

۹۰ ما ۹۰ ما ۹۰ (۱۹۹۰)

\* Adds 1-bit plus 1-bit plus 1-bit

Produces Sum and Carry

| xyz   | C S |

|-------|-----|

| 000   | 0 0 |

| 001   | 0 1 |

| 0 1 0 | 0 1 |

| 0 1 1 | 1 0 |

| 100   | 0 1 |

| 101   | 1 0 |

| 1 1 0 | 1 0 |

| 111   | 1 1 |

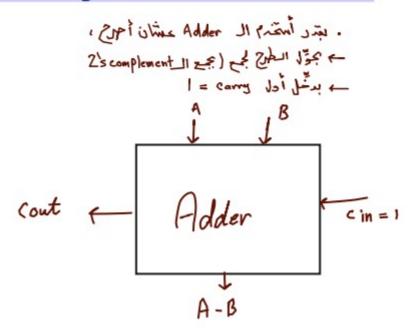

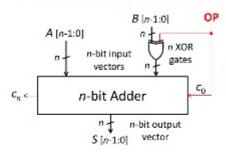

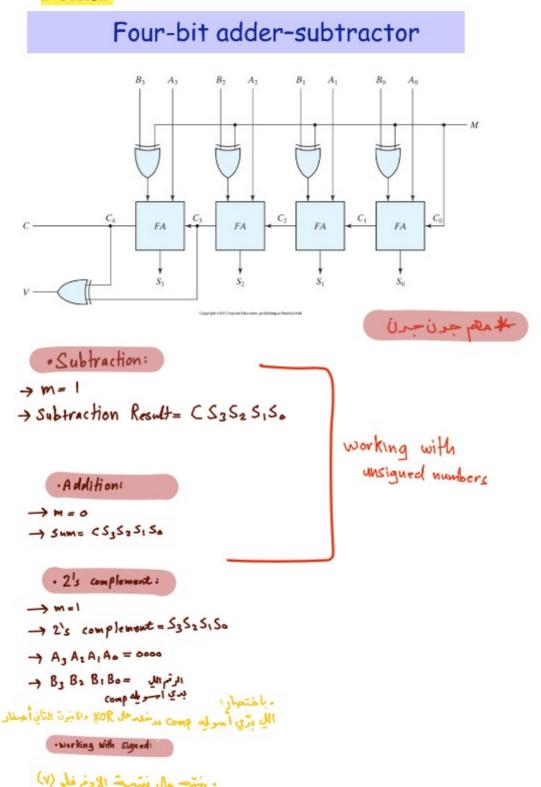

**Converting Subtraction into Addition**

Adder/Subtractor for 2's Complement

Two operations: OP = 0 (ADD), OP = 1 (SUBTRACT)

OP OP = 0 (ADD) → B XOR 0 = B S = A + B + 0 = A + B

#### OP = 1 (SUBTRACT)

B XOR 1 = 1's complement of B S = A + (1's complement of B) + 1 S = A + (2's complement of B) S = A - B

· عشان المتخدم ننس السيركت تجمع وتطرح : → بزيد البون ( qo) بتمام بال gamy مسب شو العملية. م بزيد Xor بدخل عليها (6) والعدرالثاني.

STUDENTS-HUB.com

STUDENTS-HUB.com

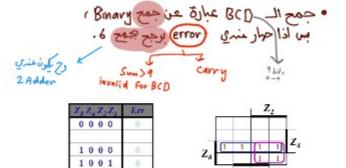

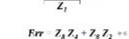

## DECIMAL ADDER (BCD Adder)

STUDENTS-HUB.com

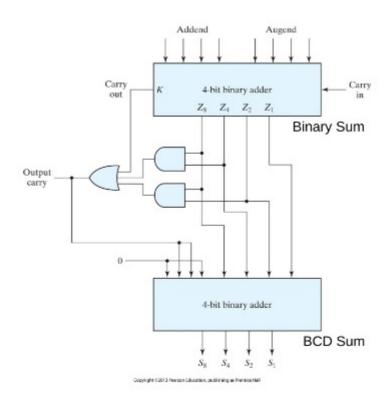

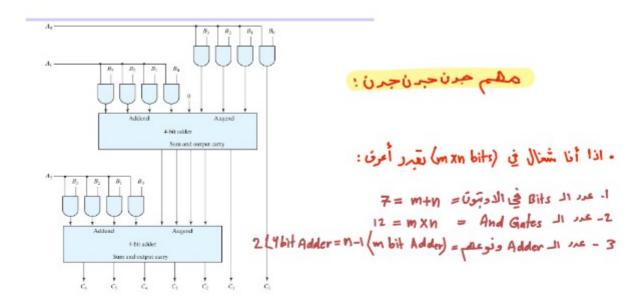

Four-bit by three-bit binary multiplier

STUDENTS-HUB.com

STUDENTS-HUB.com

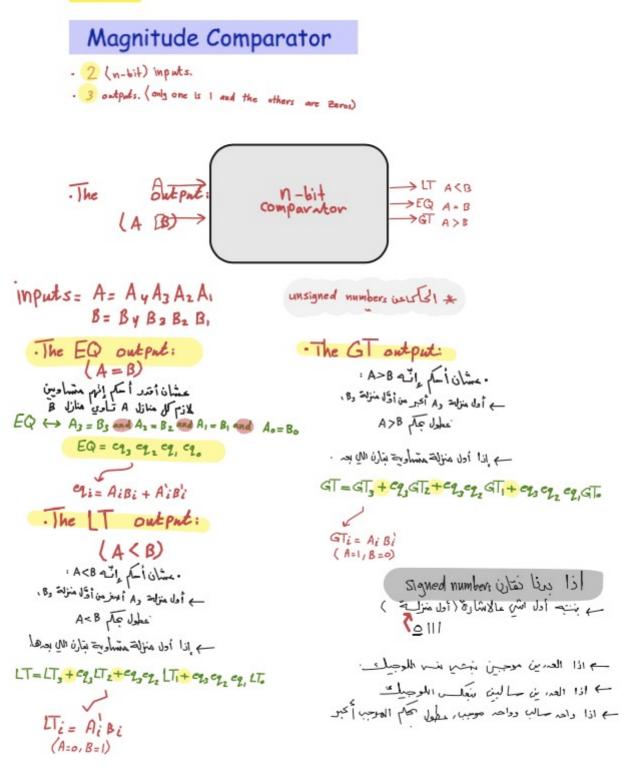

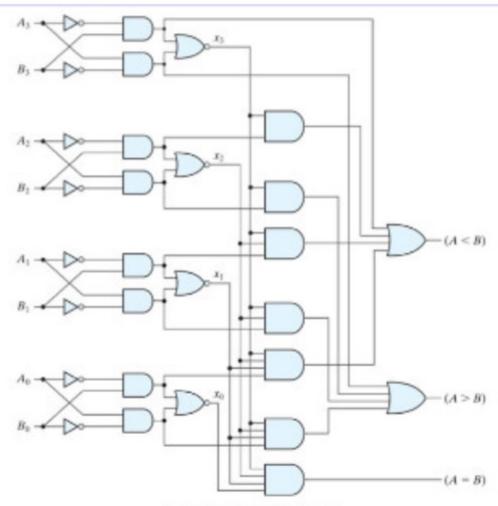

## Magnitude Comparator

Cappight 02011 Pearson Education, publishing as Presidential

STUDENTS-HUB.com

STUDENTS-HUB.com

\* ملاحظت مصب قرن: ب لوزم اختار اللي عدره أقل بين ال minterms/maxtorms

STUDENTS-HUB.com

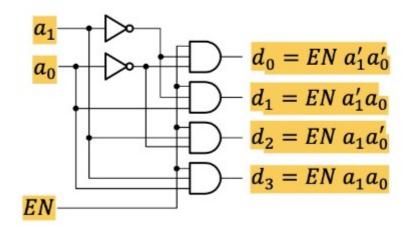

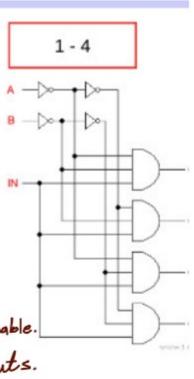

2-to-4 Decoder with Enable Input

· Additional input (En) En=0 output=000  $d_0$ 0 21  $a_1$ 2-to-4 1 · d1 En= 1 works. 20  $a_0$ Decoder 2 > d₂ EN • d<sub>3</sub> 3

| In | puts                          |                | Out   | puts  |       |

|----|-------------------------------|----------------|-------|-------|-------|

| EN | a <sub>1</sub> a <sub>0</sub> | d <sub>0</sub> | $d_1$ | $d_2$ | $d_3$ |

| 0  | хх                            | 0              | 0     | 0     | 0     |

| 1  | 0 0                           | 1              | 0     | 0     | 0     |

| 1  | 0 1                           | 0              | 1     | 0     | 0     |

| 1  | 10                            | 0              | 0     | 1     | 0     |

| 1  | 1 1                           | 0              | 0     | 0     | 1     |

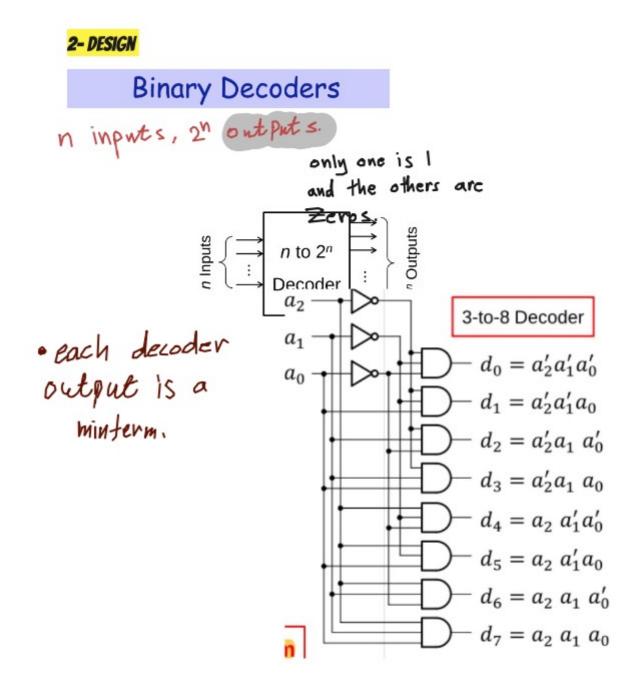

2- DESIGN

#### Using Decoders to Implement Functions

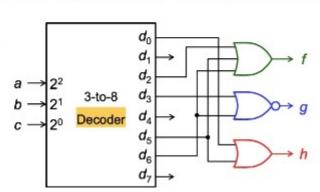

★ Example:  $f = \Sigma(2, 5, 6), g = \prod(3, 6) \rightarrow g' = \Sigma(3, 6), h = \Sigma(0, 5)$

| Inputs | 0 | utpu | ts |

|--------|---|------|----|

| abc    | f | g    | h  |

| 000    | 0 | 1    | 1  |

| 001    | 0 | 1    | 0  |

| 010    | 1 | 1    | 0  |

| 011    | 0 | 0    | 0  |

| 100    | 0 | 1    | 0  |

| 101    | 1 | 1    | 1  |

| 110    | 1 | 0    | 0  |

| 111    | 0 | 1    | 0  |

NOLO, UTO TUTIOLOTI THUSE HAS NO THITTING W

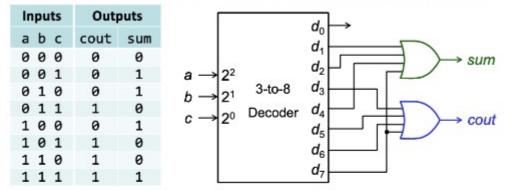

★ Example: Full Adder sum =  $\Sigma(1, 2, 4, 7)$ , cout =  $\Sigma(3, 5, 6, 7)$

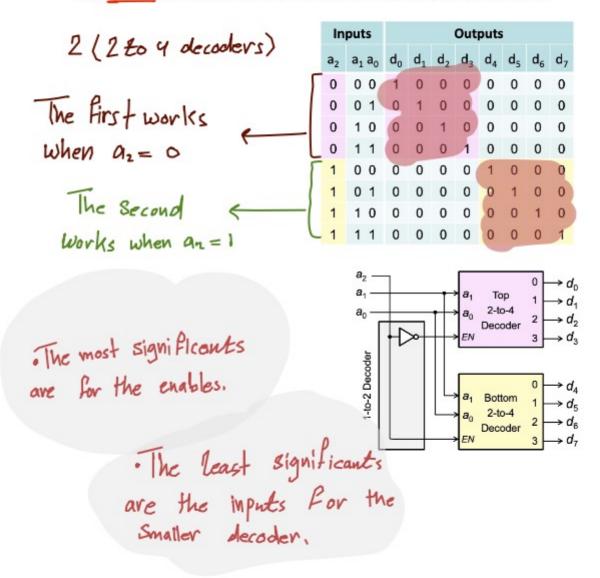

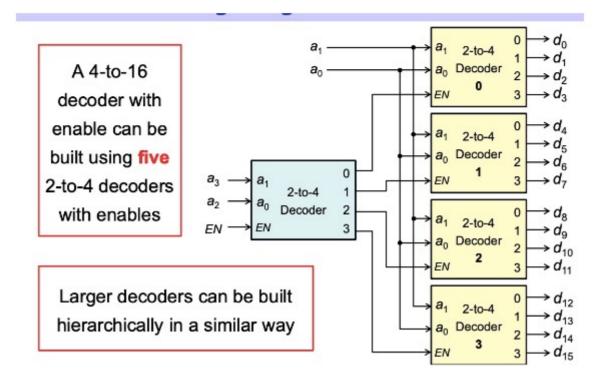

#### Building Larger Decoders

✤ A 3-to-8 decoder can be built using:

Two 2-to-4 decoders with Enable and an inverter (1-to-2 decoder)

## Building Larger Decoders

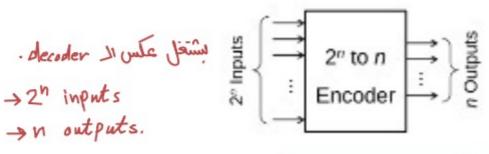

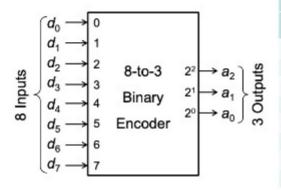

### Encoders

|                | Inputs |             |       |                |       |       |       |    |                | its            |

|----------------|--------|-------------|-------|----------------|-------|-------|-------|----|----------------|----------------|

| d <sub>7</sub> | $d_6$  | $d_{\rm S}$ | $d_4$ | d <sub>3</sub> | $d_2$ | $d_1$ | $d_0$ | a2 | a <sub>1</sub> | a <sub>0</sub> |

| 0              | 0      | 0           | 0     | 0              | 0     | 0     | 1     | 0  | 0              | 0              |

| 0              | 0      | 0           | 0     | 0              | 0     | 1     | 0     | 0  | 0              | 1              |

| 0              | 0      | 0           | 0     | 0              | 1     | 0     | 0     | 0  | 1              | 0              |

| 0              | 0      | 0           | 0     | 1              | 0     | 0     | 0     | 0  | 1              | 1              |

| 0              | 0      | 0           | 1     | 0              | 0     | 0     | 0     | 1  | 0              | 0              |

| 0              | 0      | 1           | 0     | 0              | 0     | 0     | 0     | 1  | 0              | 1              |

| 0              | 1      | 0           | 0     | 0              | 0     | 0     | 0     | 1  | 1              | 0              |

| 1              | 0      | 0           | 0     | 0              | 0     | 0     | 0     | 1  | 1              | 1              |

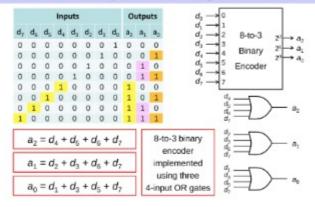

#### 8-to-3 Binary Encoder Implementation

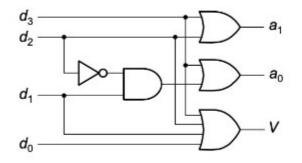

## Priority Encoder

-> a dolitional output [] to deal with errors

#### **Output Expressions:**

$$a_{1} = d_{3} + d_{2}$$

$$a_{0} = d_{3} + d_{1} d_{2}'$$

$$V = d_{3} + d_{2} + d_{1} + d_{0}$$

د هو اللي جد الادتون.

أذا الانبون فيص

STUDENTS-HUB.com

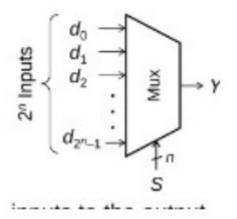

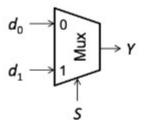

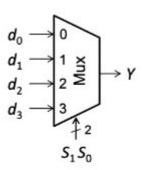

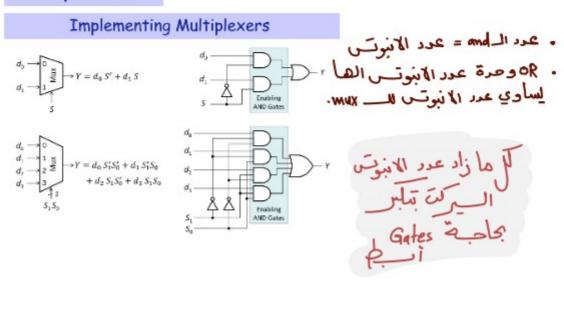

Multiplexers

- ·2" inputs.

- .n selection.

- · 1 output.

حسب الـ election واحد من الانبوتين بروح عسال الاد تبوت

oun machas.

| 1 | nput           | Output |                    |

|---|----------------|--------|--------------------|

| S | d <sub>o</sub> | $d_1$  | Y                  |

| 0 | 0              | Х      | $0 = d_0$          |

| 0 | 1              | Х      | $1 = d_0$          |

| 1 | х              | 0      | 0 = d <sub>1</sub> |

| 1 | х              | 1      | 1 = d <sub>1</sub> |

|       |                | Inp   |       | Output         |                |                    |

|-------|----------------|-------|-------|----------------|----------------|--------------------|

| $S_1$ | S <sub>0</sub> | $d_0$ | $d_1$ | d <sub>2</sub> | d <sub>3</sub> | Y                  |

| 0     | 0              | 0     | Х     | Х              | Х              | $0 = d_0$          |

| 0     | 0              | 1     | Х     | Х              | Х              | $1 = d_0$          |

| 0     | 1              | х     | 0     | х              | х              | 0 = d <sub>1</sub> |

| 0     | 1              | Х     | 1     | Х              | Х              | 1 = d <sub>1</sub> |

| 1     | 0              | Х     | Х     | 0              | Х              | 0 = d <sub>2</sub> |

| 1     | 0              | х     | Х     | 1              | Х              | 1 = d <sub>2</sub> |

| 1     | 1              | х     | Х     | Х              | 0              | 0 = d <sub>3</sub> |

| 1     | 1              | Х     | Х     | Х              | 1              | 1 = d <sub>3</sub> |

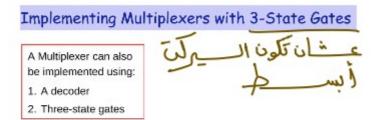

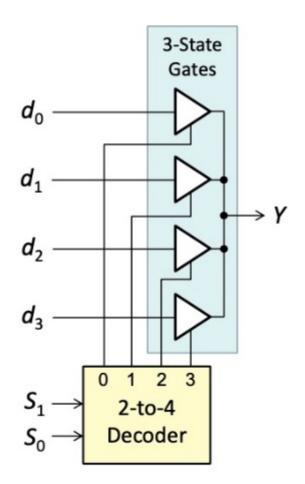

Multiplexers

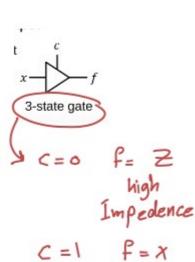

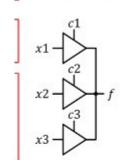

3-State Gate

| c1 | c2 | c3 | f    |

|----|----|----|------|

| 0  | 0  | 0  | z    |

| 1  | 0  | 0  | x1   |

| 0  | 1  | 0  | x2   |

| 0  | 0  | 1  | x3   |

| 0  | 1  | 1  | Burn |

| 1  | 0  | 1  | Burn |

| 1  | 1  | 0  | Burn |

| 1  | 1  | 1  | Burn |

|    |    |    |      |

limite 11 strate as each ج واحد منم بس الون ون (صف

STUDENTS-HUB.com

## Multiplexers

STUDENTS-HUB.com

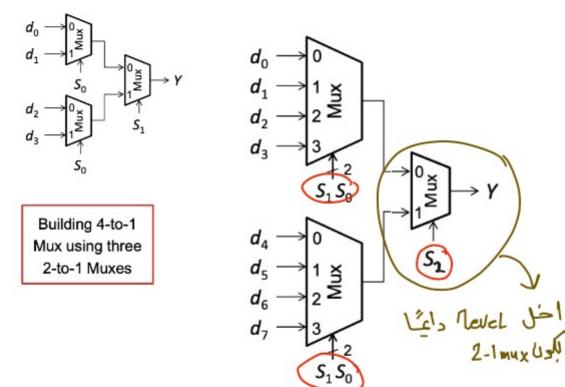

## Multiplexers

**Building Larger Multiplexers**

Least selections \_11.

· level Jeve Selection up most line .

STUDENTS-HUB.com

## Multiplexers

## Implementing a Function with a Multiplexer

| The inputs are<br>used as select<br>lines to a Mux.<br>An 8-to-1<br>because there<br>are 3 variables<br>a = 3 variables<br>a = b c = F<br>0 = 0 = 0<br>0 = 0 = 0<br>0 = 0 = 0<br>1 = 1<br>1 = 2<br>0 = 0<br>1 = 1<br>1 = 0<br>1 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

• المحريقة هاي مرج بس لل ما زار انبوتس الم الم الم ما راد انبوتس الم الم الم الم ما راد انبوتس الم الم

· بيسيط ال\_Implementation عن طريق تعليل عمر الـ Selections الآي رح أخليهم DENTS-HUB.com Uploaded By: Ahmad K Hamdan STUDENTS-HUB.com

## Multiplexers

## Implementing a Function with a Multiplexer

|   | In | put | s | Output | Comment      |                       |             |               |

|---|----|-----|---|--------|--------------|-----------------------|-------------|---------------|

|   | а  | b   | с | F      | F            |                       |             |               |

| ( | 0  | 0   | 0 | 0      | <b>F</b> = 0 | 1020                  |             |               |

| ( | 0  | 0   | 1 | 1      | F = c        | <i>c</i> →            | 0           | ٦             |

| ( | 0  | 1   | 0 | 1      | E = d        | <i>c</i> !            | 1 M         |               |

| ( | 0  | 1   | 1 | 0      | F = c'       |                       |             | $\rightarrow$ |

|   | 1  | 0   | 0 | 0      | F = 0        | $0 \longrightarrow$   | 2 4         |               |

| 1 | 1  | 0   | 1 | 0      | F = 0        | -                     | - 4         |               |

|   | 1  | 1   | 0 | 1      | F = 1        | 1>                    | 3           |               |

|   | 1  | 1   | 1 | 1      | F = 1        |                       |             |               |

|   |    |     |   |        |              | $\longrightarrow S_1$ | $S_0 = a b$ |               |

• هون استحر عنا mux أحيض لنفس ال\_function عن طريق تقليل عرد ال\_selections

· عدتان أحد المعلاقة بين المعلمان (الله ما أنتر) والمعام \* مالحجة معمة جدن جدن: Dents in this time is selections real imports si inputs on 18mg most significant 11 -> 1 is 1, Inputs - + Selections i rear in asmyx in us la Isl, @

Uploaded By: Ahmad K Hamdan

2- DESIGN

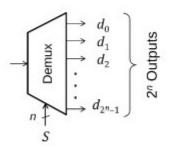

Demultiplexer Mux ال ال xmux input input n Selections م 2<sup>M</sup> outputs - حسب ال ۲ الانبوت. حدج علی احد الادتیوت

Demux Input I is equivalent to Decoder Enable EN

$I \xrightarrow{0} f_{1} \xrightarrow{0} d_{0}$ structure  $d_{1}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{3}$  $d_{3}$  $d_{3}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{3}$  $d_{1}$  $d_{1}$  $d_{2}$  $d_{2}$  $d_{3}$  $d_{1}$  $d_{2}$  $d_{3}$  $d_{3}$

$S_{1} = a_{1} \xrightarrow{2^{1}} 2^{2} \xrightarrow{2^{1}} 2^{-10-4} \xrightarrow{1} d_{1}$   $S_{0} = a_{0} \xrightarrow{2^{0}} 2^{0} \xrightarrow{2^{0}} d_{2}$   $I = EN \xrightarrow{3} d_{3}$ Think of a decoder as directing

the Enable signal to one output

decoder with enoble live ( ind demux \_1 , ind \*

demux input = decoders enable. demux selections = decoder's inputs. demux output = decoder outputs.

STUDENTS-HUB.com

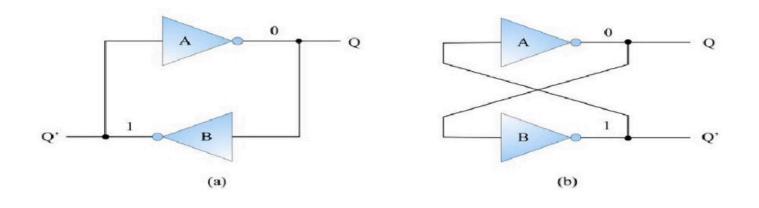

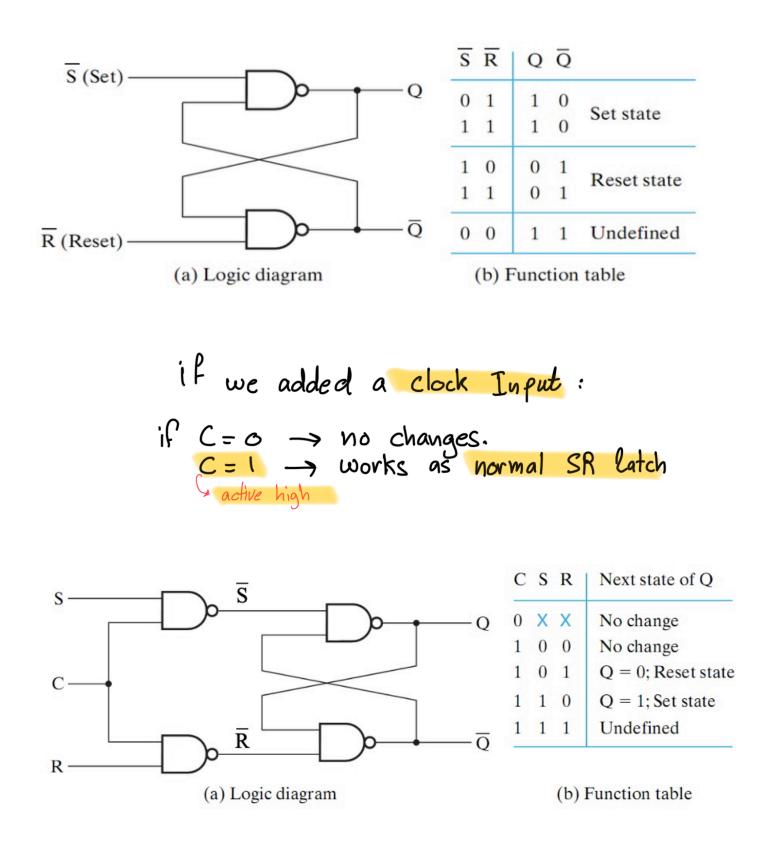

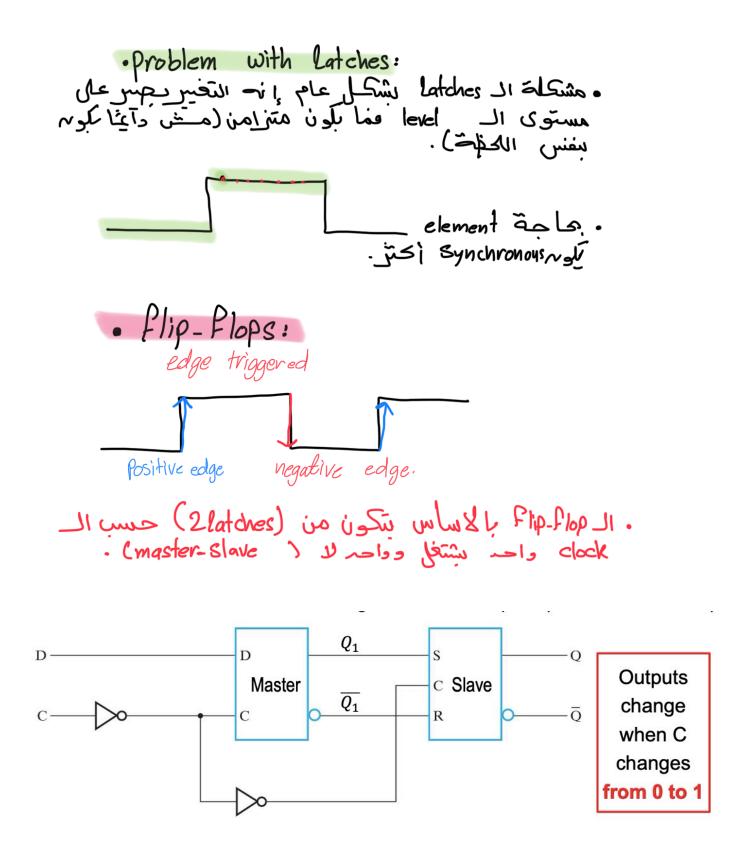

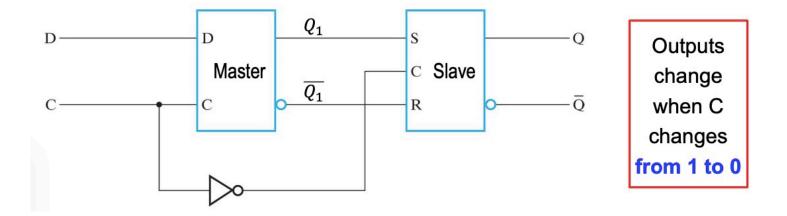

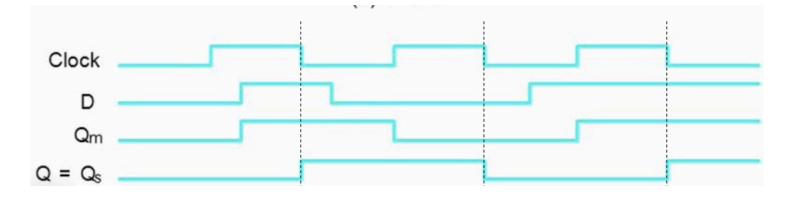

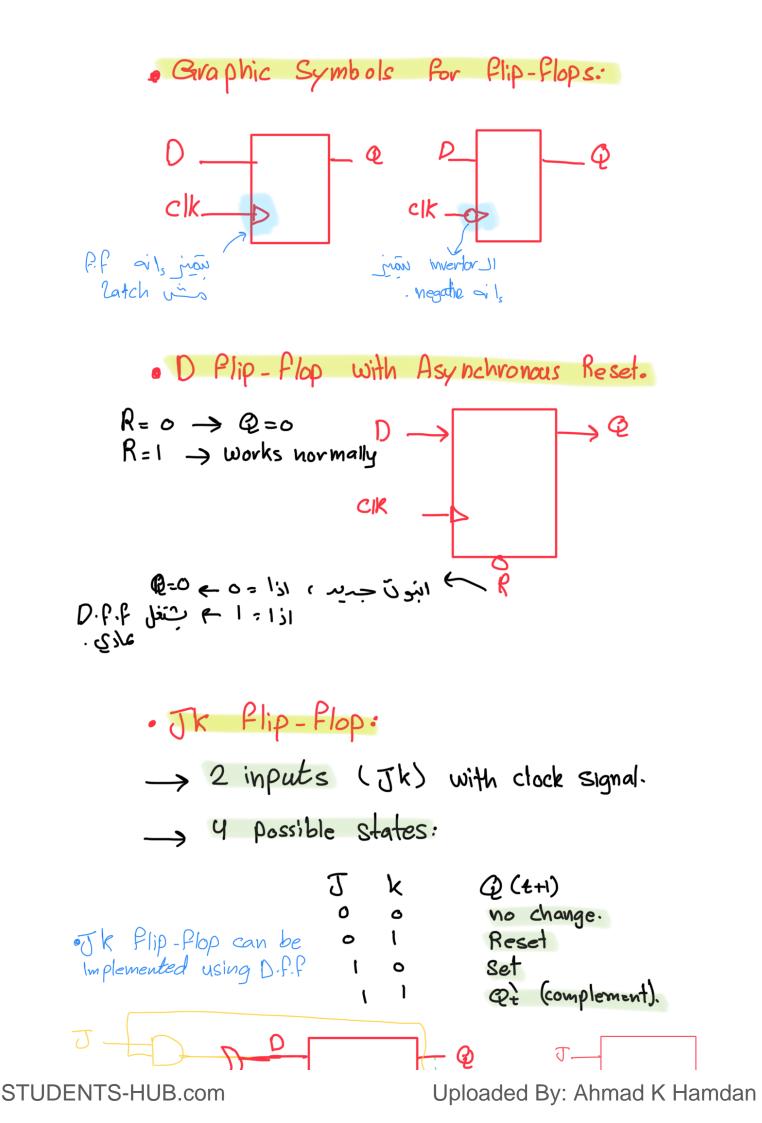

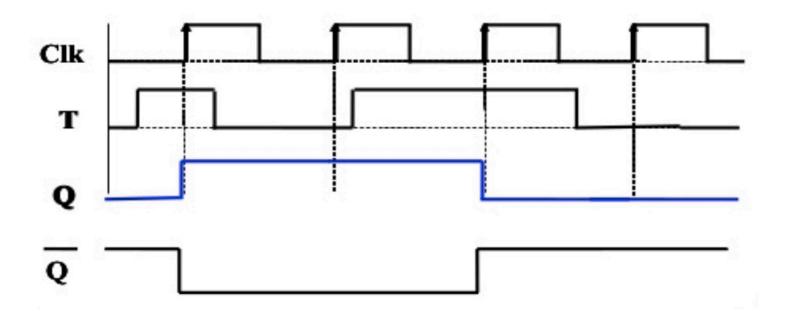

Chapter 5: Synchronous Sequential logic. ی عال memory elment in Combinational out logic IL Inquiro veries In pat + previous state. Memory Climent Sequential Circuit: Synchronous Asynchnonous. • additional input (clock) to control the changes in • no additional inputs, so the the memory elements. Changes may happen at any time. clock Signal: 4 The · level Sensitive. edge trigger. -> Positive edge - Positive pulse. > negative edge. \_\_\_\_ negative pulse. Latch flip-Flop. · latches:

STUDENTS-HUB.com

أول نوع من الـ latches عبارة عن Trivertor 2

الانبوت لكل واحد عبارة عن الاوتبوت للتّأني .

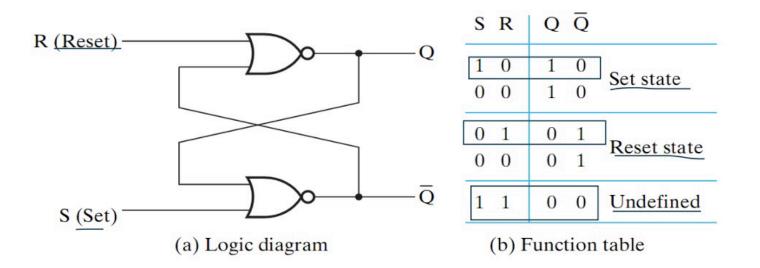

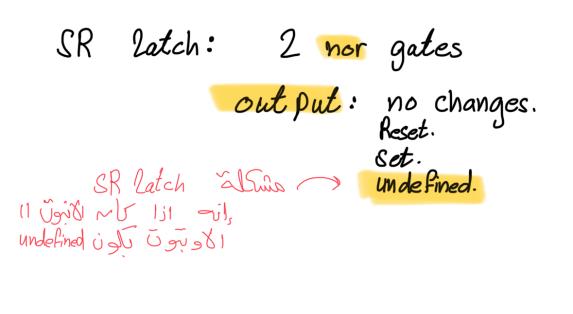

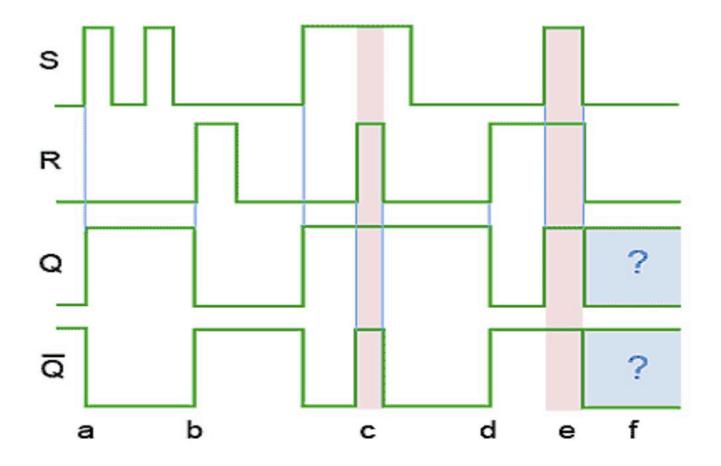

• SR Latches:

STUDENTS-HUB.com

ابما ,ا نح ال ماعلما عبارة عن العناد التعليما التعليم التعليم التعليم التعليم التعليم التعليم المعلى المعالي المعام المعالي المعالي المعام المعالي المعالي المعام المعالي المعام المعالي المعالي المعام المعالي المعام المعالي المعالي المعام المعالي المعالي المعام المعالي المعام المعالي المعام المعالي المعالي المعام المعالي الم المعالي

> • Characteristic Equation of the SR Latch: output ا بتربغ بين ا Present State وال Input ا

| Q(t) | S | R | Q(t + 1)      |

|------|---|---|---------------|

| 0    | 0 | 0 | 0             |

| 0    | 0 | 1 | 0             |

| 0    | 1 | 0 | 1             |

| 0    | 1 | 1 | Indeterminate |

| 1    | 0 | 0 | 1             |

| 1    | 0 | 1 | 0             |

| 1    | 1 | 0 | 1             |

| 1    | 1 | 1 | Indeterminate |

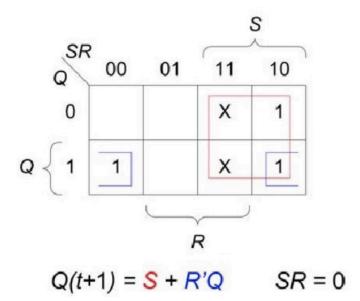

S'R' Latch with NaNd Gates:

Nand Gates.

Works active low, (when S=1 Q=0).

when inputs = oo -> Q is undefined.

STUDENTS-HUB.com

STUDENTS-HUB.com

- 0 Q = 0; Reset state

- 1 Q = 1; Set state

(b) Function table

(a) Logic diagram

R

R

STUDENTS-HUB.com

Uploaded By: Ahmad K Hamdan

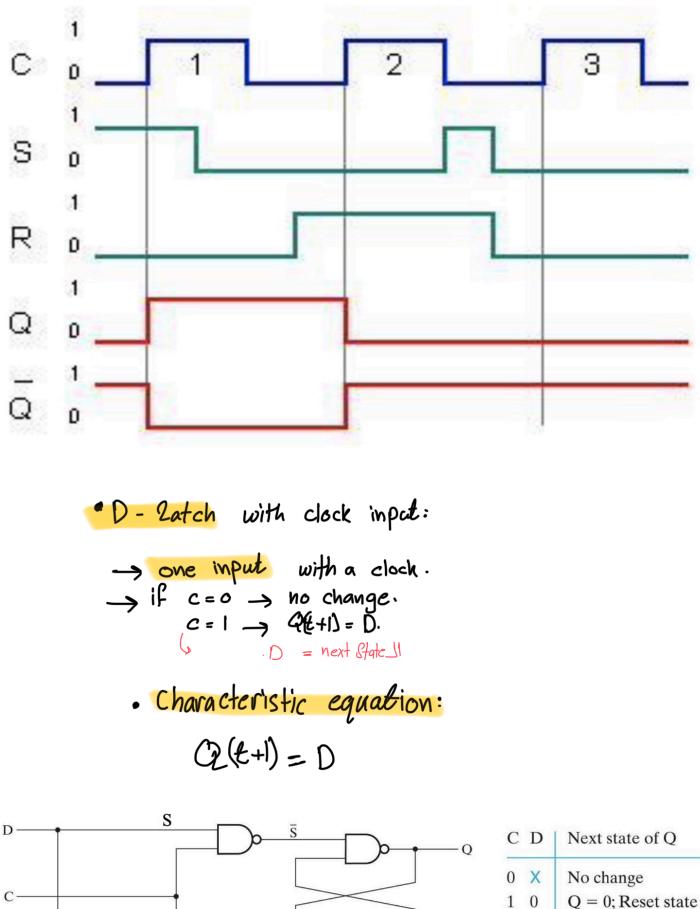

1

$\overline{Q}$

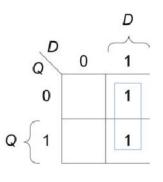

| D | Q(t + 1) |

|---|----------|

| 0 | 0        |

| 1 | 1        |

| 0 | 0        |

| 1 | 1        |

|   | 0        |

$$Q(t+1) = D$$

بما إنّ Posifive Edge - Triogerd معناته بسمح في التغيير من عند Rising edge بعن ب في كنهة الانتقال من عبقر إلى واحسر

• negative Edge - Triggerd D Flip-flop. · one invertor بس في Positive . • بسمح بالدقيس عند negative edge ، ديني ب لخراد الانتقال من الماى 0.

Uploaded By: Ahmad K Hamdan

STUDENTS-HUB.com

· Characteristic equation :

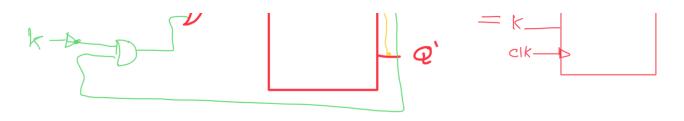

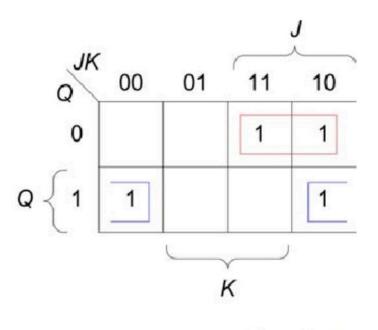

| Q(t) | J | K | Q(t + 1) |

|------|---|---|----------|

| 0    | 0 | 0 | 0        |

| 0    | 0 | 1 | 0        |

| 0    | 1 | 0 | 1        |

| 0    | 1 | 1 | 1        |

| 1    | 0 | 0 | 1        |

| 1    | 0 | 1 | 0        |

| 1    | 1 | 0 | 1        |

| 1    | 1 | 1 | 0        |

Q(t+1) = JQ' + K'Q

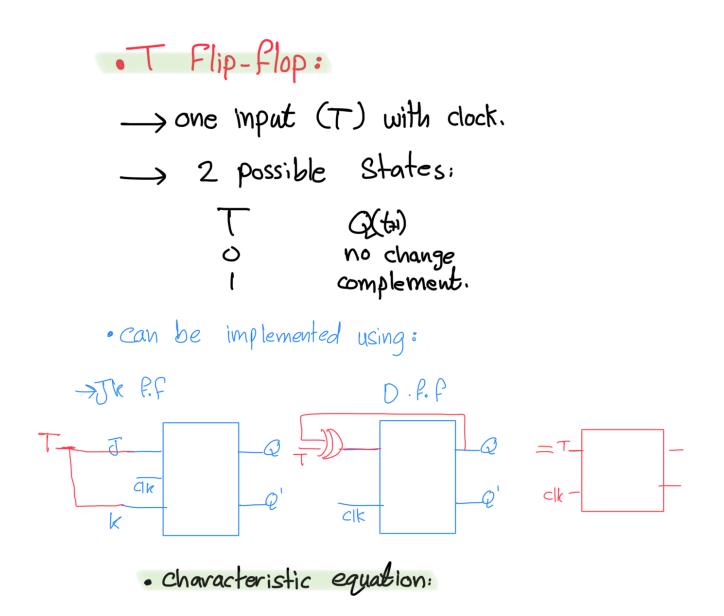

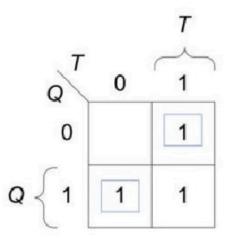

T = togale

STUDENTS-HUB.com

| Q(t) | Т | Q(t + 1) |

|------|---|----------|

| 0    | 0 | 0        |

| 0    | 1 | 1        |

| 1    | 0 | 1        |

| 1    | 1 | 0        |

Q(t+1) = TQ'+T'Q

STUDENTS-HUB.com

• ملام جدن جدن :

-> Plip Plops charasteristic equations:

- D Flip Flop: Q(t+1) = D

- · Jk Flip flop: Q(t+1) = JQ' + KQ.

- · T Flip Flop: Q(E+1) = T @ Q(E)

| DF | D Flip-Flop |     |   | JK Flip-Flop |       |            |   | T Flip | -Flop           |

|----|-------------|-----|---|--------------|-------|------------|---|--------|-----------------|

| D  | Q(t+1       | )   | J | K            |       | Q(t+1)     | Τ | Ç      | ?( <i>t</i> +1) |

| 0  | 0 Re        | set | 0 | 0            | Q(t)  | No change  | 0 | Q(t)   | No change       |

| 1  | 1 Se        | t i | 0 | 1            | 0     | Reset      | 1 | Q'(t)  | Complement      |

|    |             |     | 1 | 0            | 1     | Set        |   |        |                 |

|    |             |     | 1 | 1            | Q'(t) | Complement |   |        |                 |

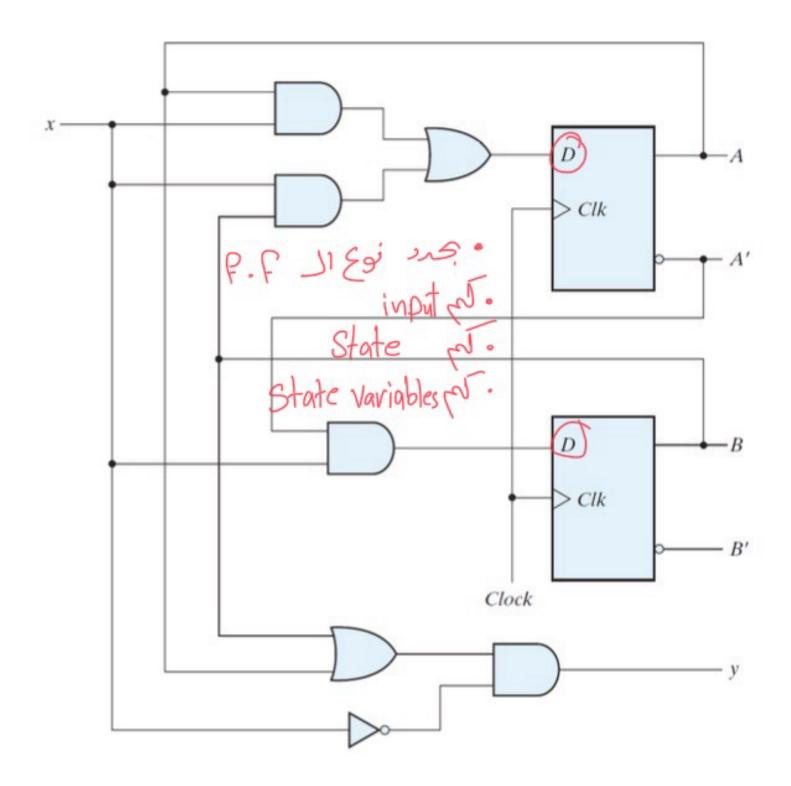

• Analysis of clocked sequential Circuits: State table المعالم أدعل لا موجودة ، بدي أدعل لا : analysis ال ال . - Inputs محادلة ال output . Next State JI ZJSLas State table State dlagram.

· Analysis Example:

STUDENTS-HUB.com

| Present<br>State |   |   |   | ext<br>ate | Output |

|------------------|---|---|---|------------|--------|

| A                | B | x | A | B          | Y      |

| 0                | 0 | 0 | 0 | 0          | 0      |

| 0                | 0 | 1 | 0 | 1          | 0      |

| 0                | 1 | 0 | 0 | 0          | 1      |

| 0                | 1 | 1 | 1 | 1          | 0      |

| 1                | 0 | 0 | 0 | 0          | 1      |

| 1                | 0 | 1 | 1 | 0          | 0      |

| 1                | 1 | 0 | 0 | 0          | 1      |

| 1                | 1 | 1 | 1 | 0          | 0      |

# Another form of the state table

| Present |     | N            | ext | Stat         | Output |       |              |

|---------|-----|--------------|-----|--------------|--------|-------|--------------|

|         | ate | x = <b>0</b> |     | <i>x</i> = 1 |        | x = 0 | <i>x</i> = 1 |

| A       | В   | A            | В   | A            | B      | Y     | Y            |

| 0       | 0   | 0            | 0   | 0            | 1      | 0     | 0            |

| 0       | 1   | 0            | 0   | 1            | 1      | 1     | 0            |

| 1       | 0   | 0            | 0   | 1            | 0      | 1     | 0            |

| 1       | 1   | 0            | 0   | 1            | 0      | 1     | 0            |

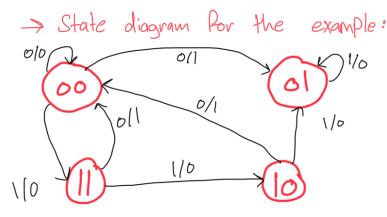

# · State diagram:

• State diagram if there is no output: diagramic is no output:

· mealy and moore sequential circuits:

-> mealy machine: output depends on present State and inputs.

STUDENTS-HUB.com

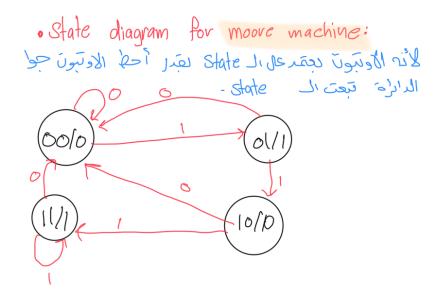

moove machine: output depends on present state only - p.s ما الد عمر بر عال ال

· State Reduction: تقال عدد ال States عشان اخل عدر ال P.f أوعشان combinational circuit JI from

### $\rightarrow$ Example:

| Present   | n   | ex+ | output | t  |

|-----------|-----|-----|--------|----|

|           | X=0 | X=1 | X=0    | X= |

| 9         | 9   | 6   | Ø      | 8  |

| 6         | С   | 0   | 0      | 0  |

| $\subset$ | q   | ol  | 0      | 0  |

| d         | C   | F   | Õ      | (  |

| 2         | a   | f   | 6      | 1  |

| F         | 9   | F   | 0      | 1  |

| 9         | 9   | f   | 0      | 1  |

•from the table; e and g have some output and Btate, so they are equivalent and I can Replace e by g.

#### STUDENTS-HUB.com

- بدور على equivelent states

بجدها نجتر احذف وحدة منهن

و أقل عدر ال states

- experient l'an unit l'equivelent l'an unit of the next state l'and the prime is the state of t

جرن: Same output and same Q(t+1): eq الحد different output and Q(t+1): eq الحدث Same output but different Qt+1): (State a) أكبر لخارة ما زاكر من ال

Uploaded By: Ahmad K Hamdan

output

next

Present

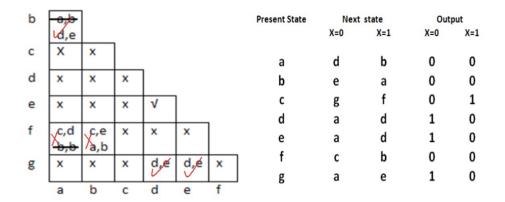

| b |          |       |     |   | 10 |                              | esent State | Next | state | Out | put |

|---|----------|-------|-----|---|----|------------------------------|-------------|------|-------|-----|-----|

| С | x        | x     | ]   |   |    | since outputs not equivalent |             | X=0  | X=1   | X=0 | X=1 |

| d | x        | x     | x < | 7 |    | d and e are                  | а           | d    | b     | 0   | 0   |

|   |          | 10000 |     |   | -  | the same                     | b           | е    | а     | 0   | 0   |

| e | х        | х     | х   | V | *  |                              | с           | g    | f     | 0   | 1   |

| f | $\vdash$ |       | ~   | ~ | ~  | Г                            | d           | а    | d     | 1   | 0   |

|   |          |       | x   | x | X  |                              | e           | а    | d     | 1   | 0   |

| g | х        | х     | x   |   |    | x                            | f           | с    | b     | 0   | 0   |

|   | a        | b     | L   |   | e  |                              | g           | а    | е     | 1   | 0   |

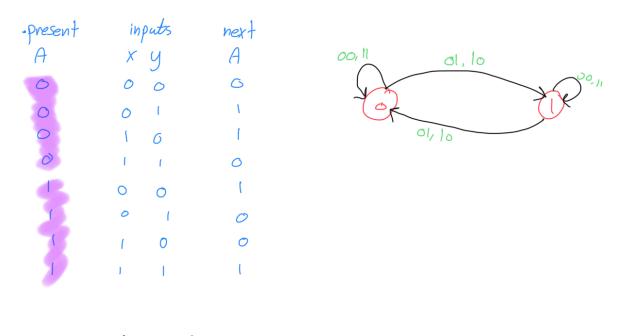

Sequential Circuit design: · design 1. idesign . · state table in state diag das is on the dis on the diag das is on the diag das is on the dis on the di

Chavacteristic I Je excitation JI. Sum next State JIs present state Jisite no st e flip Flop input i

| Present<br>State | Next<br>State  | F.F.<br>Input |

|------------------|----------------|---------------|

| Q(t)             | <b>Q</b> (t+1) | D             |

| 0                | 0              | 0             |

| 0                | 1              | 1             |

| 1                | 0              | 0             |

| 1                | 1              | 1             |

| Present<br>State | Next<br>State | F.F.<br>Input |   |                             |

|------------------|---------------|---------------|---|-----------------------------|

| Q(t)             | Q(t+1)        | J             | K | 0 0 (No change)             |

| 0                | 0             | 0             | X | 0 1 (Reset)<br>1 0 (Set)    |

| 0                | 1             | 1             | X | <11 (Toggle)                |

| 1                | 0             | x             | 1 | 0 1 (Reset)<br>1 1 (Toggle) |

| 1                | 1             | x             | 0 | O (No change)               |

|                  |               |               |   | 1 0 (Set)                   |

| <b>Q(t)</b> | <b>Q</b> (t+1) | T |

|-------------|----------------|---|

| 0           | 0              | 0 |

| 0           | 1              | 1 |

| 1           | 0              | 1 |

| 1           | 1              | 0 |

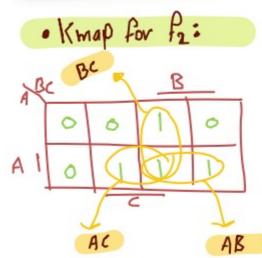

| <ul> <li>Design Exam</li> <li>→ Detect 3 or ma</li> <li>D Plip Plop.</li> </ul> | ple:<br>some consecutive i's using<br>licit and should be along the set of the s                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •State diagram. State 0<br>Solo 0 5+/0<br>Salo 5+/0                             | state 15 $z_{2}$ , $z_{2}$ , $z_{3}$ , $z_{2}$ , $z_{2}$ , $z_{3}$ , $z_{2}$ , $z_{3}$ , $z_{2}$ , $z_{3}$ , $z$                                                                     |

|                                                                                 | y<br>c f.f ]<br>c lient ai<br>c teritation<br>c teri |

| K map for DA<br>A B<br>A C<br>A C<br>C<br>A C<br>STUDENTS-HUB.com               | <ul> <li>k maps joint with the second s</li></ul>                                                                                                                                                                                                                                                                                                  |

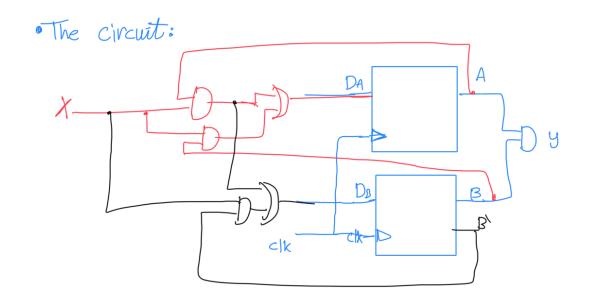

UA= HX + BX PR= AX+ B'x y = AB (From the table).

: in ãols ãos do · ك الامتلك نفس طريقة الخل ونف الحطوان، يتطل الفكرة إي أفهم المطوب حيح د أعامل اله mangallo حيح وباتي الخطوري . als row

- State diagram

binary assignment

State table

- · equations for F.F inputs, and for the output.

- · circuit

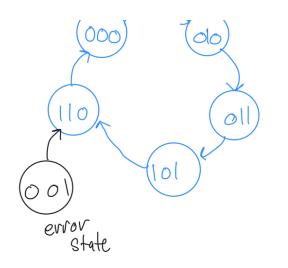

· Dealing with Unused States: ے ادا کام عندی states مش مستخدمة فی السيرلين تبعين بدّي أعرف احدر اذا ومهلتكها فشو next state 11 ~ at la

· Example:

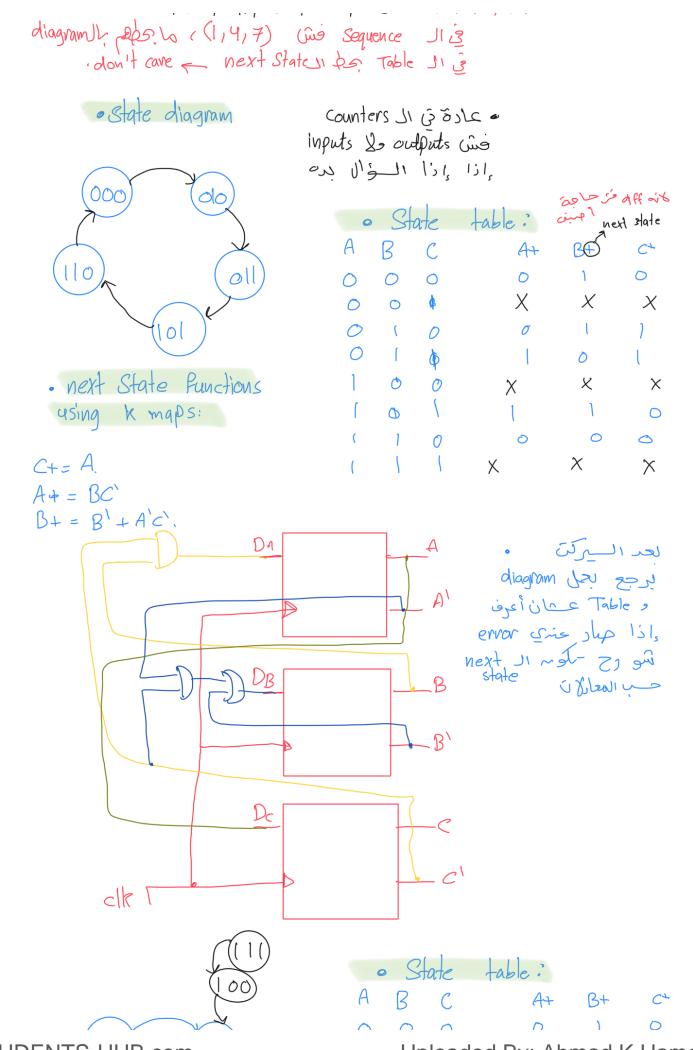

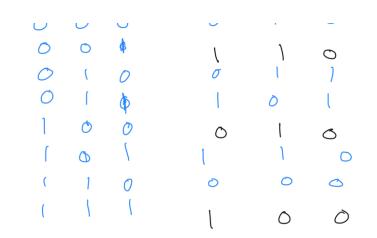

design repeats 5 states in sequence: "using d f.f.) 000,010,011, 101, 110,000 (0,2,3,5,6,0)

STUDENTS-HUB.com