# ENCS 2340 Summary Chapter 5

By: Malak Obaid

STUDENTS-HUB.com

Sequential circuits :- previous outputs cutput derais

Sequential circuit عر مترا من ٢ متر امن Asynchronous Synchronous sequential Circuit 1 Sequential circuit output inpu Combinational next step Flip Flop circuit present step seed back Positive level Clock > CALISLERE clock cycle 1 positive < of the negative edge 401 edge - Cycle - Cycle - negative level Time here on seconds = clock cycle = L = Hz Frequence Synchronouns is elis de 1 bit cija Flip Flop US memory يعنى مكند يكونه عنا عبد كبير من الكنه بيكونوا المشبوكن edge UI che are EX Given the clock cycle = 0.5ns = 0.5x10-9 sec Find the clock frequency = 1 = 2×109 HZ = 2GHz STUDENTS-HUB.com Uploaded By: Malak Dar Obaid

equiphial circuits & previous noted output  $ms = 10^{-3} sec$ 10 Seci MS sequentia 10-9 sec ns Sec 100psn=10 equertical circuit SWFPW IRPL Sec Sec 1 Hz finonio Present step Seedback  $1 \text{ KHz} = 10^3 \text{ Hz}$ G 1 MHz = 10° Hz Positive level G G 1 6 DO 51 1100 389 CAPE" = 109 regative level 9-1 CYC CUCIC ock cycle nere DCC ri me us is tic a Gon D ail-125.05 ME Vern 2 A. wen the clock eyele tois (equel) 1001 6 0.5210-9 STUDENTS-HUB.com Uploaded By: Malak Dar Obaid

4

-Asynchonous Sequential Circuit -1 latch = 1 bitinput 1 output Com binitional circuit next step. latch present ste 0 0 0 o'clock Uton Se clock JIs level Ut de dénie latch JI edge Ulde are sin Flip Flop JI Ge all Synchonous with latch it is demart FIP => 2 bits Flop FIP Flop Notes Sula \* Ich Die aning Zi Out اسملت هن واحد is ver enp - et viero / lei coias, Ill a made in and black 0 bubble by 71 un 160,1 0,0 1, 1,0 1,0,1 Flip Flopulais دالالمعلم الم تعير أو ١,١ (متحل جدة فعَلَ تَعْبِر) DENTSJEUB. GOM? Uploaded By: Malak Dar Obaid

SOM latch = 1 bit Flip Flop=1 bi (asynchon our (Synchonomous) 0 = edge d'ine and new level I) is 0 0 lenel. negative positive W/ edg edge e V Then us & alle Sec Using MA W 5N P cycle 1 win is jei a) 51 edge OPP ( CL/100 edge SI V V T T \* Storage dement (latch) -Latch with nor gate SR (1)-5 active ( high 1 R (reset 7 SR 0 200 alda Latch SUDRACK S - block diagram 0 5( sel Uploaded By: Malak Dar Obaid JDENTS-HUB.com

NOR Id B T I lated 20 110 A f = 00 2 B sen listo sin 1/4 0 D is I he per lo land, Witapon USI NOR UI R ()0 31000 MAN SUZI 0 Ou memory = () O no change 0 9/211 0 10 OI invalid operation < 1 forbiblin 0 0/90 function tables in latch Il cize dup or eemerit 9 DC R (reset)o Atin Q =1 PN 71 & gund dec 0 (Q) =0 =0 O MORO = 1 pbb aix D=O S(set) ی Norgate عنا انون = 1 اذا اکواں مین R=0 S=1 viel ell and all of it رج سخط اللع توت و يول الم عنة اللي بعد (النم في كلة للي بعد all bit Sol lised lie = R=0 / S=0 من الرينوت = 0 فالاسوت الثاني رح لكونه اوتون الكلمة الن STUDENTS HUBICON I LAN 193 LAN BUD Aded Bps: Malak Dar Oba

(memory) no change all with is the input s=0 is two R=0 المال الاستوت الج مطل نفسو NOR gale is aix R=0, S=0 is allo us Filder لا عكنا الحكم من المعر عنه العار esplisher hui (Unknown State) Jei is is in The dise in 173 W T haracteristic Equation of the SR Latch QL++1) V R 13 0 C. Jadala Figure to be 0 0 0 Indeterminate (dont cares) 0 0 0 15 5 Indeterminate ( dont mes) SR Q X  $\phi'$ Q X RI RI R Q(++1) = SUpleaded By: Malak Dar Obaid STUDENTS-HUB.com

Gated SR Latch with Clock Enable R (reset) CR Clock SCY CS SLOCET State NUR Next State R No Change Х 0 0 Nochange 111 17.97 Q=0 Reset State 0 1 Q=1 Set State 0 Undefined terminate 0 1 0.3 Uploaded By: Malak Dar Obar STUDENTS-HUB.com D

SR Latch with NAND gates, (active low) (S)Set P  $\overline{Q}$ (R) reset- $\bigcirc$ R ()O Set State 0 0 Reset State 0 Undefined 0 0 5 5 Gala SR Latch with clock Enable 1 5 C (clock) 5 R 0 Q R Next stak of Q S R P X No change 0 X No change 1 0 0 Q= 0 Reset 1 0 1.4 Q=1 Set 1 0 Undefined Uploaded By: Mal **SUDENTS-HUB.com**

2222 )-Latch with Clock Enable (1 100 100 R, Szic (20) D C. Next State of Q No change X NIA Q=0 Reset 0 V Q=1 Set Stale 5 3 5 5 0 C 4 Q(t+1) 0 Q(E) D D  $\bigcirc$ 0 01 0 0 0 0  $\mathcal{O}$ 9 Q(++1) = 0 () D . STUDENTS-HUB.com Uploaded By: Malak Dar Obaid

Graphic Symbols for latches SR latch SR latch D Latch A bubble appears at the complemented output Q Indicates that Q is the complement of A bubble also appears at the inputs of an SR & Latch Indicates that logic-O is used (not 1) to set or Reset the latch fin the NAND latch -Implemintation) **TUDENTS-HUB.com** Uploaded By: Malak Dar Obaid

Problem with latches - A latch is level sensitive (sensitive to the level of the clock) As long as the clock signal is high. Any change in the value of entry in put D appears in the output q Output Q Keeps Changing its value during a clock Cyc le Final value of actput Q is uncertain due to this uncertainity, latches are Not used as memory elements in synchronous circulits X=1 Latch Clock high of all & gra  $\bigcirc \oplus 1$ Uploaded By: Malak Dar Obaid JDENTS-HUB.com

1 77 Flip-Flops & is a better memory element for synchronous circuits 1000 solves the problem of latches in synchronous sequential circuits, A latch is sensitive to the level of the clock but Flip-Flop is sensitive to the edge of the clock -A Flip-Flop is also called edge\_triggered memory element - It changes it outputy value at the edge of the clock D Flip-Flop - Built using 2 latches in a master-slave configural 5 - A master latch (D-type) receives external inputs - A slave latch (SR-type) receives inputs from the master latch - only one latch is enabled at any given time when CIK=0 the master is enabled & the D input latened (Slave disable) STUDENTS-HUB.com Uploaden Bate Matak Dar Obaid

Qm Ð C P Master slave C Qm CIK R output change when clk changes from 0 to 1 Negative Edge-Triggered D Flip Flop -13 when CIK = 1 the master is enabled and the D'input is latched -10 (slave disabled) when clK=0 the slave is enabled to generate the autputs (master is disabled) 1 ---Qm D 5 -Q master 4 C slave CIK m R 1 output changes when CIK Changes 9 from 1 to 0 9 3 Uploaded By: Malak Dar Obaid STUDENTS-HUB.com

-3 3 Graphic Symbols for Flip Flop 1 1 1 Data 30 FLIP Flip FLOP FLOP CIK CIK negative edge positive edge 10 U with Asynchronous Set & Reset D-FF - when Flip Flops are powered their initial State is Unknown -10 15 - Some Flip-Flops have an Asynchronous Set and/or Reset input -3 15 - Set forces Q to become 1 Independently of the clock -- Reset forces Q to become O Independently of the clock inputs Set 4 Set Reset Data Clk 2 Data 2 Q 0 CIK 0 R 0 active bu rising edge Reset Uploaded By: Malak Dar Obaid TUDENTS-HUB.com

3 3 3 7 Jok Flip Ebp & withup = pitingtonal) - The D Flip Flop is the most commonly Used type - The JK is another type of Elip Flop with inputs: J, K, C/K - when JK = 10 -> Set, when JK = 01 -> Reset When JK= OU -> NU charge when JK=11 > Inverted output 10 - JK can be implemented using DFF and gates. -C Q(L+1) C T OK 1 QUE 0 0 0 0 0 15 1 5 Q(t) 1 -5 JQ  $D = 2\dot{\Phi} + \kappa, \dot{\Phi}$ 9 CIK K'Q TUDENTS-HUB.com Uploaded By: Malak Dar Obaid

Characteristic Equation of the JK Fip Flop Q(L) bost Jula Kamo, Q(L+1) / 21 gol 7 custor type do Flip Flop with inter 0 arth MARIN MTS implemented whips DFFO or XT 90 ap ()11.11 K-map de latilio gl سنج لدر ان  $Q(HI) = J\overline{Q} + K\overline{Q}$ Q= JQ+KQ D.X

STUDENTS-HUB.com

T Flip Flop! (Toggle) in printing on the - has I and clk inputs (1++) - when T=0 > No change -when I=1 -> Invert outputs T Flip Flop can be implemented using JK FF lo i viali 12 111- 5 it can be also implemented using D-Flip Flop & XOR JQ'+K'QT -> (T@ 9)> 6 0 0 0 gale Q(++1) = 14-010-23 T CIK 3 K CIK 6 (1) 2 D T 0 0 0 0 0 0 CIK 3 Q(t+1) 3 Q(t)0(4)

STUDENTS-HUB.com

Characterisitic Equation of T-Flip Flop dugni xlo Q(++ 16 T per Tress implemer 90 Flop Can -map JU 9) ĐG  $(\mathbf{I})$ 6666 -

STUDENTS-HUB.com

## Analysis of Clocked Sequential Circuits

Analysis is describing what a given circuit will do

The output of a clocked sequential circuit is determined by

- 1. Inputs

- 2. State of the Flip-Flops

#### Analysis Procedure:

- 1. Obtain the equations at the inputs of the Flip-Flops

- 2. Obtain the next state and the output equations

- 3. Fill the state table for all possible input and state values

- 4. Draw the state diagram

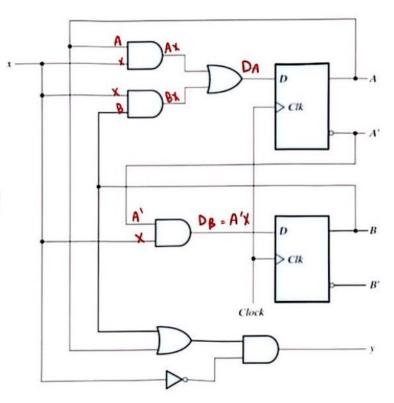

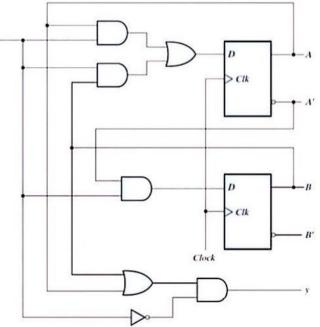

## Example 1 =-

Is this a clocked sequential circuit?

#### YES!

What type of Memory?

#### D Flip-Flops

How many state variables?

Two state variables: A and B

What are the Inputs?

One Input: x

What are the Outputs?

One Output: y

Made with Goodnotes STUDENTS-HUB.com

- What are the equations on the D inputs of the flip-flops?

- $D_A = A x + B x$

$$D_B = A' x$$

\* A and B are the current state

$$A(t) = A, \ B(t) = B$$

- \*  $D_A$  and  $D_B$  are the **next state**  $A(t+1) = D_A$ ,  $B(t+1) = D_B$

- The values of A and B will be  $D_A$ and  $D_B$  at the next clock edge

The next state equations define the next state

At the inputs of the Flip-Flops

Next state equations?

$A(t+1) = D_A = A x + B x$

$B(t+1)=D_B=A'x$

- There is only one output y

- What is the output equation?

$$y = (A + B) x'$$

Made with Goodnotes

STUDENTS-HUB.com

❖ State table shows the Next State and Output in a tabular form

❖ Next State Equations: A(t + 1) = A x + B x and B(t + 1) = A' x

❖ Output Equation: y = (A + B) x'

|   | sent            | Input                             |   | ext<br>ate | Output             |  |

|---|-----------------|-----------------------------------|---|------------|--------------------|--|

| A | B               | x                                 | A | B          | Y                  |  |

| 0 | 0               | 0                                 | 0 | 0          | 0                  |  |

| 0 | 0               | 1                                 | 0 | 1          | 0                  |  |

| 0 | 1               | 0                                 | 0 | 0          | 1                  |  |

| 0 | 1               | 1                                 | 1 | 1          | 0                  |  |

| 1 | 0               | 0                                 | 0 | 0          | 1                  |  |

| 1 | 0               | 1                                 | 1 | 0          | 0                  |  |

| 1 | 1               | 0                                 | 0 | 0          | 1                  |  |

| 1 | 1               | 1                                 |   | 0          | 0                  |  |

| 1 | A.X-<br>1 - 1 - | +B.X K<br>+I-I<br>, I = I<br>, So |   | (A-        | لا<br>(#B)<br>ونعو |  |

| L   | Anoth | er foi     | m    | of t       | he st | tate tab     | le           |

|-----|-------|------------|------|------------|-------|--------------|--------------|

| Dro | sent  | N          | lext | Stat       | e     | Out          | put          |

|     | ate   | <b>x</b> = | 0    | <b>x</b> : | = 1   | <i>x</i> = 0 | <i>x</i> = 1 |

| A   | B     | A          | B    | A          | B     | Y            | Y            |

| 0   | 0     | 0          | 0    | 0          | 1     | 0            | 0            |

| 0   | 1     | 0          | 0    | 1          | 1     | 1            | 0            |

| 1   | 0     | 0          | 0    | 1          | 0     | 1            | 0            |

| 1   | 1     | 0          | 0    | 1          | 0     | 1            | 0            |

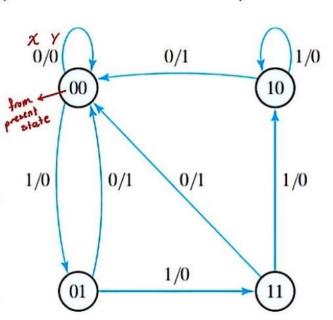

State diagram is a graphical representation of a state table

- The circles are the states

- \* Two state variable  $\rightarrow$  Four states (ALL values of A and B)

- Arcs are the state transitions

Labeled with: Input x / Output y

| Dro | sent | N          | ext | Stat       | e   | Out          | put          |

|-----|------|------------|-----|------------|-----|--------------|--------------|

|     | ate  | <b>x</b> = | 0   | <b>x</b> : | = 1 | <i>x</i> = 0 | <i>x</i> = 1 |

| A   | B    | A          | B   | A          | B   | Y            | Y            |

| 0   | 0    | 0          | 0   | 0          | 1   | 0            | 0            |

| 0   | 1    | 0          | 0   | 1          | 1   | 1            | 0            |

| 1   | 0    | 0          | 0   | 1          | 0   | 1            | 0            |

| 1   | 1    | 0          | 0   | 1          | 0   | 1            | 0            |

Made with Goodnotes

#### STUDENTS-HUB.com

#### Combinational versus Sequential Analysis

#### Analysis of Combinational Circuits

- Obtain the Boolean Equations

- Fill the Truth Table

#### Analysis of Sequential Circuits

- Obtain the Next State Equations

- Obtain the Output Equations

- Fill the State Table

- Draw the State Diagram

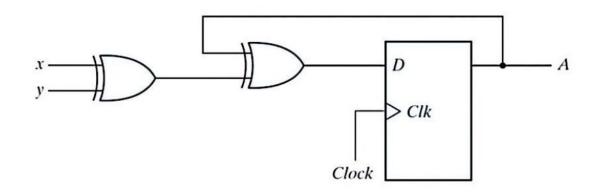

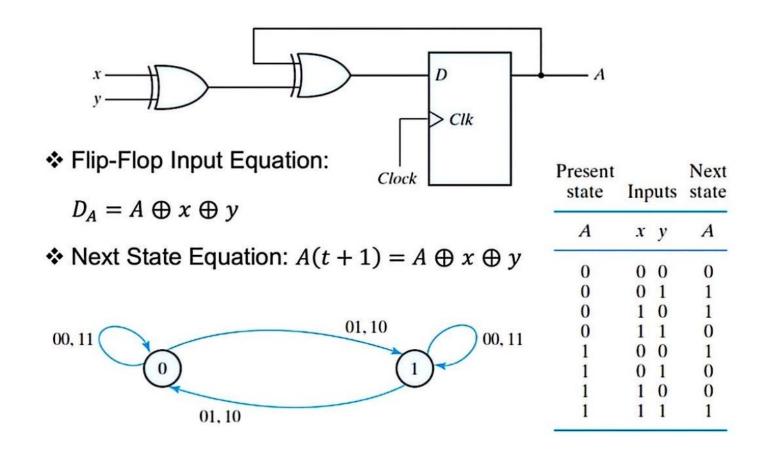

#### Example with Output = Current State

- Analyze the sequential circuit shown below

- Two inputs: x and y

- One state variable A

- ✤ No separate output → Output = current state A

- Obtain the next state equation, state table, and state diagram

Made with Goodnotes

Output is a function of input only

Next state is a function of input and current state

Output is a function of input and current state

STUDENTS-HUB.com

Example 3?

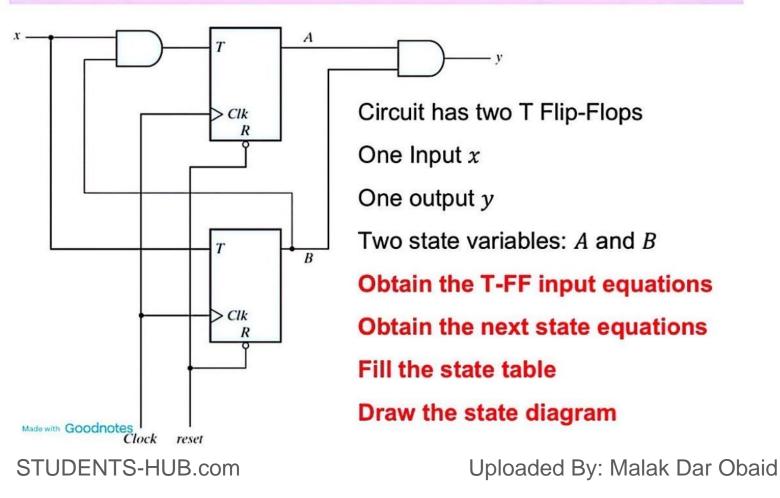

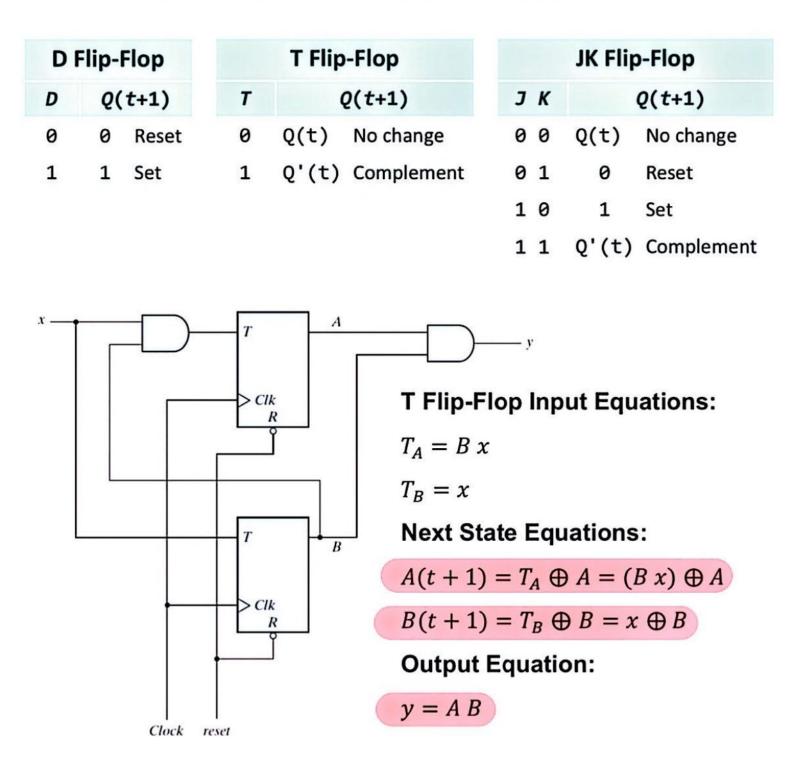

## Sequential Circuit with T Flip-Flops

• For D Flip-Flop: Q(t+1) = D

♦ For T Flip-Flop:  $Q(t+1) = T \oplus Q(t)$

These equations define the Next State

• For JK Flip-Flop:

$$Q(t+1) = J Q'(t) + K' Q(t)$$

Made with Goodnotes

T Flip-Flop Input Equations:

## State Table

| $T_A$ | = | В | x |  |

|-------|---|---|---|--|

| n     |   |   |   |  |

$T_B = x$

Next State Equations:

$A(t+1) = (B x) \oplus A$

$B(t+1) = x \oplus B$

**Output Equation:**

y = A B

|   | sent<br>ate | Input |   | ate | Output |

|---|-------------|-------|---|-----|--------|

| A | B           | x     | A | B   | Y      |

| 0 | 0           | 0     | 0 | 0   | 0      |

| 0 | 0           | 1     | 0 | 1   | 0      |

| 0 | 1           | 0     | 0 | 1   | 0      |

| 0 | 1           | 1     | 1 | 0   | 0      |

| 1 | 0           | 0     | 1 | 0   | 0      |

| 1 | 0           | 1     | 1 | 1   | 0      |

| 1 | 1           | 0     | 1 | 1   | 1      |

| 1 | 1           | 1     | 0 | 0   | 1      |

Notice that the output is a function of the present state only. It does **NOT** depend on the input *x*

|   | sent | Input |   | ate | Output | فقط محتبنا فتمة x x فا<br>moore مرولا نحتقد<br>machine 1 على الإسوت |

|---|------|-------|---|-----|--------|---------------------------------------------------------------------|

| A | B    | x     | A | В   | y      | (00/0)                                                              |

| 0 | 0    | 0     | 0 | 0   | 0      | y see                                                               |

| 0 | 0    | 1     | 0 | 1   | 0      | 3                                                                   |

| 0 | 1    | 0     | 0 | 1   | 0      | 1                                                                   |

| 0 | 1    | 1     | 1 | 0   | 0      | 1                                                                   |

| 1 | 0    | 0     | 1 | 0   | 0      |                                                                     |

| 1 | 0    | 1     | 1 | 1   | 0      | $\downarrow$                                                        |

| 1 | 1    | 0     | 1 | 1   | 1      | (11/1)                                                              |

| 1 | 1    | 1     | 0 | 0   | 1      |                                                                     |

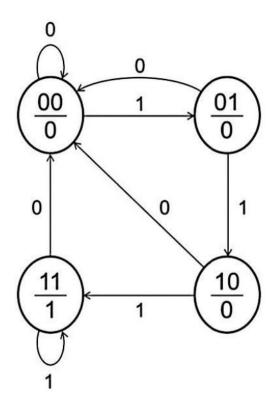

Four States: AB = 00, 01, 10, 11 (drawn as circles)

• Output Equation: y = AB (does not depend on input x)

• Output y is shown inside the state circle (AB/y)

Made with Goodnotes

STUDENTS-HUB.com

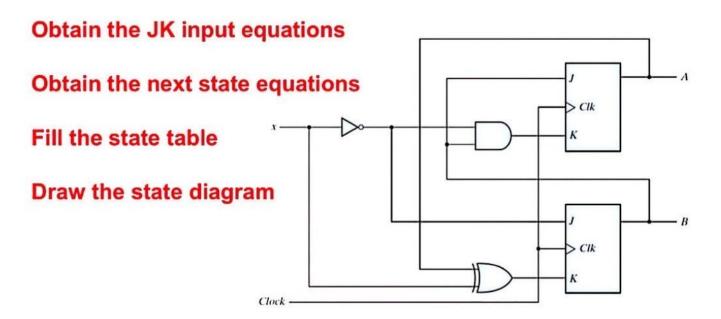

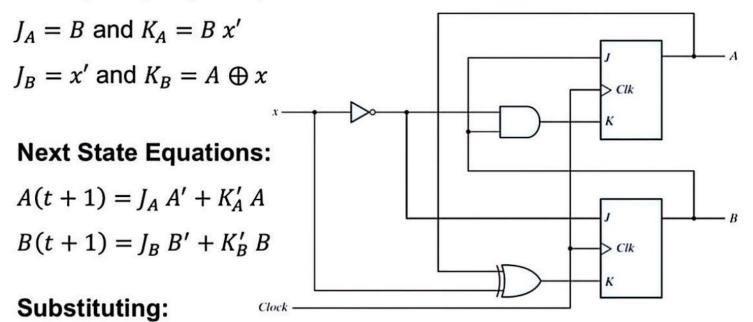

## Sequential Circuit with a JK Flip-Flops

One Input x and two state variables: A and B (outputs of Flip-Flops)

No separate output

Output = Current state A B

#### JK Flip-Flop Input Equations:

A(t+1) = B A' + (Bx')'A = A'B + AB' + Ax

$B(t+1) = x'B' + (A \oplus x)'B = B'x' + A B x + A'B x'$

Made with Goodnotes

STUDENTS-HUB.com

#### From JK Input Equations to State Table

|   | sent<br>ate | Input |   | ate |    | Flip-<br>Inp   | Flop<br>uts    |                |

|---|-------------|-------|---|-----|----|----------------|----------------|----------------|

| A | B           | x     | A | B   | JA | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> |

| 0 | 0           | 0     | 0 | 1   | 0  | 0              | 1              | 0              |

| 0 | 0           | 1     | 0 | 0   | 0  | 0              | 0              | 1              |

| 0 | 1           | 0     | 1 | 1   | 1  | 1              | 1              | 0              |

| 0 | 1           | 1     | 1 | 0   | 1  | 0              | 0              | 1              |

| 1 | 0           | 0     | 1 | 1   | 0  | 0              | 1              | 1              |

| 1 | 0           | 1     | 1 | 0   | 0  | 0              | 0              | 0              |

| 1 | 1           | 0     | 0 | 0   | 1  | 1              | 1              | 1              |

| 1 | 1           | 1     | 1 | 1   | 1  | 0              | 0              | 0              |

**JK Input Equations:**  $J_A = B$ ,  $K_A = B x'$ ,  $J_B = x'$  and  $K_B = A \oplus x$

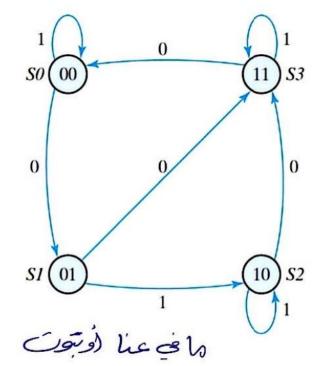

#### From State Table to State Diagram

Four states: AB = 00,01,10,and 11 (drawn as circles) Arcs show the input value *x* on the state transition

| Present<br>State |   |   |   | Next<br>State |  |  |

|------------------|---|---|---|---------------|--|--|

| A B              |   | x | Α | B             |  |  |

| 0                | 0 | 0 | 0 | 1             |  |  |

| 0                | 0 | 1 | 0 | 0             |  |  |

| 0                | 1 | 0 | 1 | 1             |  |  |

| 0                | 1 | 1 | 1 | 0             |  |  |

| 1                | 0 | 0 | 1 | 1             |  |  |

| 1                | 0 | 1 | 1 | 0             |  |  |

| 1                | 1 | 0 | 0 | 0             |  |  |

| 1                | 1 | 1 | 1 | 1             |  |  |

Made with Goodnotes

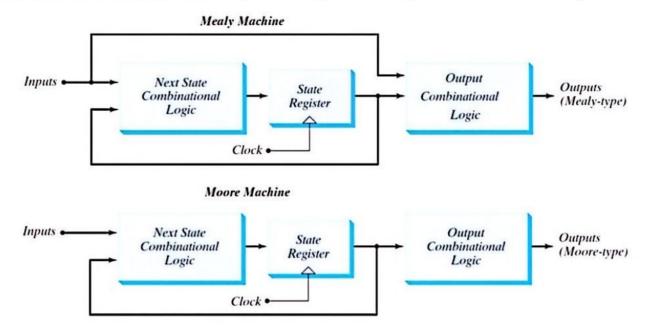

## Mealy versus Moore Sequential Circuits

There are two ways to design a clocked sequential circuit: **1. Mealy Machine:** Outputs depend on present state and inputs **2. Moore Machine:** Outputs depend on present state only

Made with Goodnotes

### Mealy Machine

- The outputs are a function of the present state and Inputs

- The outputs are NOT synchronized with the clock

- The outputs may change if inputs change during the clock cycle

- The outputs may have momentary false values (called glitches)

- The correct outputs are present just before the edge of the clock

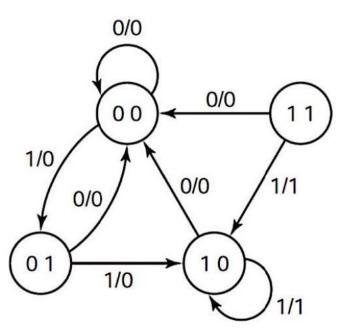

## Mealy State Diagram

- An example of a Mealy state diagram is shown on the right

- Each arc is labeled with: Input / Output

- The output is shown on the arcs of the state diagram

- The output depends on the current state and input

- Notice that State 11 cannot be reached from the other states

Made with Goodnotes

## Moore Machine

- The outputs are a function of the Flip-Flop outputs only

- The outputs depend on the current state only

- The outputs are synchronized with the clock

- Glitches cannot appear in the outputs (even if inputs change)

- A given design might mix between Mealy and Moore

#### Moore State Diagram

- An example of a Moore state diagram is shown on the right

- Arcs are labeled with input only

- The output is shown inside the state: (State / Output)

- The output depends on the current state only

Made with Goodnotes

# Summary

- To analyze a clocked sequential circuit:

- 1. Obtain the equations at the Inputs of the flip-flops

- 2. Obtain the Next State equations

- ♦ For a D Flip-Flop, the Next State = D input equation

- ♦ For T and JK, use the characteristic equation of the Flip-Flop

- 3. Obtain the Output equations

- 4. Fill the State Table

- ♦ Put all the combinations of current state and input

- ♦ Fill the next state and output columns

- 5. Draw the State Diagram

- Two types of clocked sequential circuits: Mealy versus Moore

Made with Goodnotes