# DEPARTMENT OF COMPUTER SYSTEM ENGINEERING

Digital Integrated Circuits - ENCS333

Dr. Khader Mohammad Lecture #0- Introduction

Integrated-Circuit Devices and Modeling

# Integrated circuits (ICs)

- Integrated circuits (ICs) are a keystone of modern electronics

- IC is a collection of electronic components –

resistors, transistors, capacitors

- All stuffed into a tiny chip, and connected together to achieve a common goal

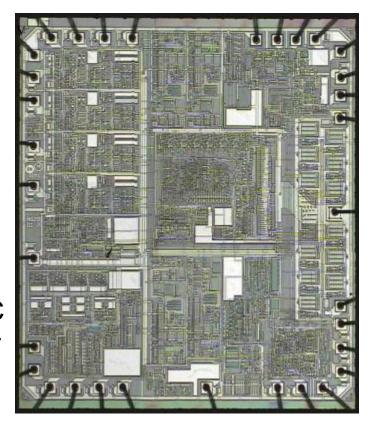

- Inside the IC: "The real "meat" to an IC is a complex layering of semiconductor wafers, copper, and other materials, which interconnect to form transistors, resistors or other components in a circuit."

- IC Packages: The package is what encapsulates the integrated circuit die and splays it out into a device we can students-Hub comity connect to.

Uploaded By: anonymous

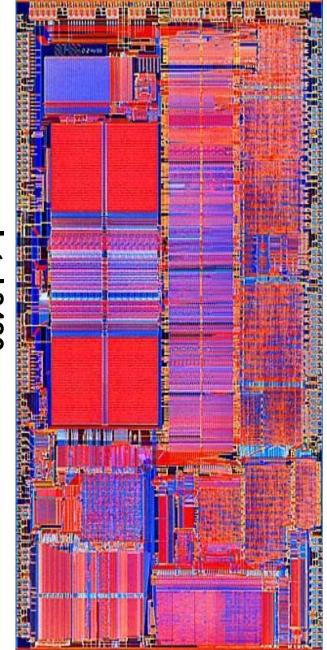

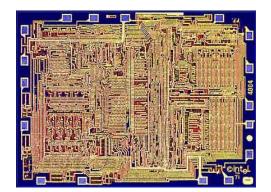

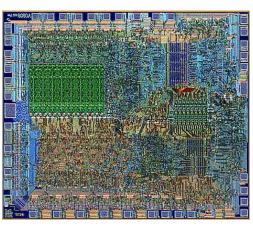

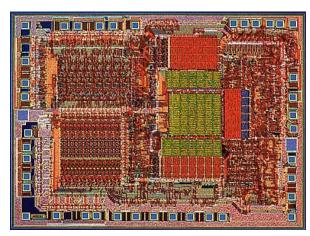

## Technology Evolution: Intel CPU Chips

Intel 4004 ('71)

**Intel 8080**

**Intel 8085**

Intel 8286

Lec 1

Courtesy Intel

Intel 8486 Poloaded By: anonymous

STUDENTS-HUB.com

- 1. Multi-Core Technology

- 2. CPU Sockets

- 3. Chipsets

- 4. Frequency (Clock Rate)

data arrival time

library setup time data required time data required time

clock CLKCORE (rise edge) clock network delay (ideal)

0.00

3.05 F

0.04 0.00 2.95 r

Opioadeu by, anonymous

```

U18579/A1 (OR4D1BWP35HVT)

U18579/Z (OR4D1BWP35HVT)

0.00 \\ 0.10

0.08 f

0.18 f

clock CLKCORE (rise edge)

clock network delay (ideal)

clock network delay (ideal)

rxb/rxb link list/g gate ff count_vll/ps_reg[i]/CP (SDFKCNQUNDIBWP3SHVT)

rxb/rxb link list/g gate ff count_vll/ps_reg[i]/Q (SDFKCNQUNDIBWP3SHVT)

rxb/rxb link list/count_vll_ps[i] (net) 0.00

0.05

0.00 r

0.08 f

0.08 f

0.08

0.00

0.00

0.00

0.00

0.00

0.00

Fanout

Trans

Derate

Path

Path Type: max

Path Group: CLKCORE

Startpoint: rxb/rxb link list/g gate ff count vllyps reg[l]

(rising edge-triggered flip-flop clocked by CLKCORE)

Endpoint: rxb/rxb arbiter/rxb arbiter portll/rxb arbiter update/rxb arbiter dwrr update/current weight3_reg[4]

(rising edge-triggered flip-flop clocked by CLKCORE)

Path Group: CLKCORE

Operating Conditions: ss0p9vm40c

Mire Load Model Mode: segmented

Library: tcbn28hpmbwp35hvtss0p9vm40c

slack (MET)

0.00

```

rxb/rxb\_arbiter/rxb\_arbiter\_port1/rxb\_arbiter\_update/rxb\_arbiter\_dwrr\_update/current\_weight3\_reg[4]/CP\_(SDFKCNQUNDIBWP35CD3NM)

rbb/rxb\_arbiter/rxb\_arbiter\_porti/rxb\_arbiter\_update/rxb\_arbiter\_dvrr\_update/n248 (net) 1 0.00 0.00 2.95 f rxb/rxb\_arbiter/rxb\_arbiter\_porti/rxb\_arbiter\_update/rxb\_arbiter\_dvrr\_update/current\_weight2\_egi4j/CH (SDFKCNQUNDIBMP33CD3NN) data\_arrival\_time 2.35

## Course Content

### **Lecture 0: Introduction**

### **Lecture 1: Circuits & Layout**

- Review: Basic R, L, and C

- IC Manufacturing and Design Metrics CMOS -Ch1 Sec 1.3, Ch2 Sec 2.2

### **Lecture 2: Design Flow AND Cad Tools**

#### Lecture 3,4:

- **Transistor Theory**

- Semiconductor material: PN-junction, NMOS, PMOS -Ch3

#### Lecture 5:

- DC & Transient Response

- Device modeling parameterization from I-V curves. Ch5.2 and ch5.3

### **Lecture 6:** Logical Effort

Lecture 7: Power

**Lecture 8: Simulation and Timing Ch7.2-7.5**

SPICE models and parameters

### Lecture 9: Combinational Circuit Design

- The CMOS inverter- Ch3, Ch5

- The layout of an Inverter and basic gates **ch2.3-ch7**

- Combinational / static logic structures Ch6.1-2

### Lecture 10: Circuit/Logic Families

### Lecture 11: Sequential Circuit Design

Sequential logic gates; Latches and Flip-Flops ch7.4- Ch10.3

## Lecture 12: Clock/Wires/Interconnect Wire modeling - Ch4

Lecture 13: Introduction to: Packaging, Power, & Clock

Lecture 14: Introduction to: Design for Testability

Lecture 15: Datapaths, Adders, SRAM Lecture 16: ROMs, CAMs, & PLAs Lecture 17: Scaling , Pitfalls & Reliability STUDENTS representations of the state of the state

## References

- Some Good video to watch :

- What is Integrated circuit :

- https://www.youtube.com/watch?v=UWPxa6N7VvA

- Evolution of the Microchip)

- https://www.youtube.com/watch?v=XA8TLOF010w

- Google's Chip Designing AI

- https://www.youtube.com/watch?v=zR9lusOpEzk

- How are chips made?

- https://www.youtube.com/watch?v=g8Qav3vlv9s

- Watch Nvidia Reveal H100 AI Chip

- How does AI apply to chip design Nvidia did it in this way?

- https://www.youtube.com/watch?v=BD25ZW1HaQw

- https://www.youtube.com/watch?v=n\_oXA7Xe3ZM

- BZU student Vedio:

https://www.youtube.com/watch?v=YKL\_KD6nE6A&feature=youtu.be&fbclid=IwAR3ONoaCT5ULm\_xQ145kgZ6m4qYS1ebOR5tCxTwhULjMshNxs\_s4HM260dM

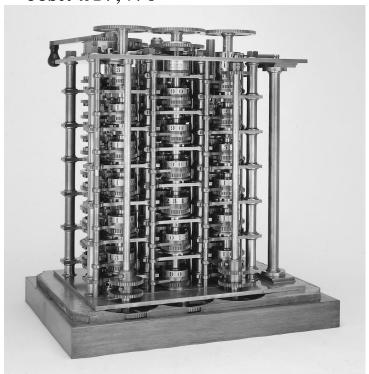

## The First Computer

The Babbage Difference Engine (1832)

**25,000** parts

**cost:** £17,470

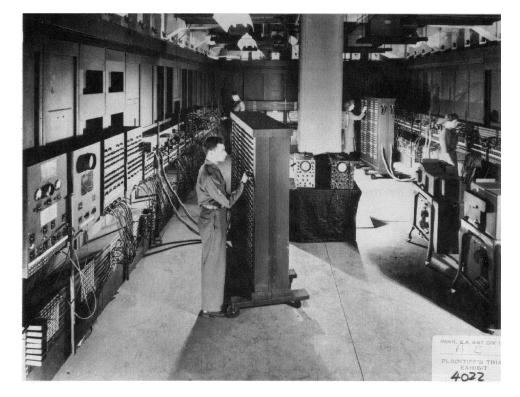

ENIAC - The first electronic computer (1946)

## History - Evolution in Complexity

Medium Scale Integration Introduced in 1967 MSI Logic Block per chip 20-200 Large Scale Integration Introduced in 1972 LSI Logic Block per chip 200-2000 Very Large Scale Integration Introduced in 1978 VLSI Logic Block per chip 2000-20000 Ultra Large Scale Integration Introduced in 1989 ULSI . Logic Block per chip 20000 >>

| Year | Component                      | Name                 | Number of MOSFETs<br>(in billions)                               |

|------|--------------------------------|----------------------|------------------------------------------------------------------|

| 2022 | microprocessor<br>(commercial) | M1 Ultra             | 114 (dual-die SoC; entire M1 Ultra is a multi-chip module)       |

| 2022 | GPU                            | Nvidia H100          | 80                                                               |

| 2020 | DLP                            | Colossus Mk2 GC200   | 59.4                                                             |

| 2020 | any IC chip                    | Wafer Scale Engine 2 | 2600 (wafer-scale design consisting of 84 exposed fields (dies)) |

| 2022 | Flash memory                   | Micron's V-NAND chip | 5333 (stacked package of 16 232-layer 3D NAND dies)              |

Uploaded By: anonymous

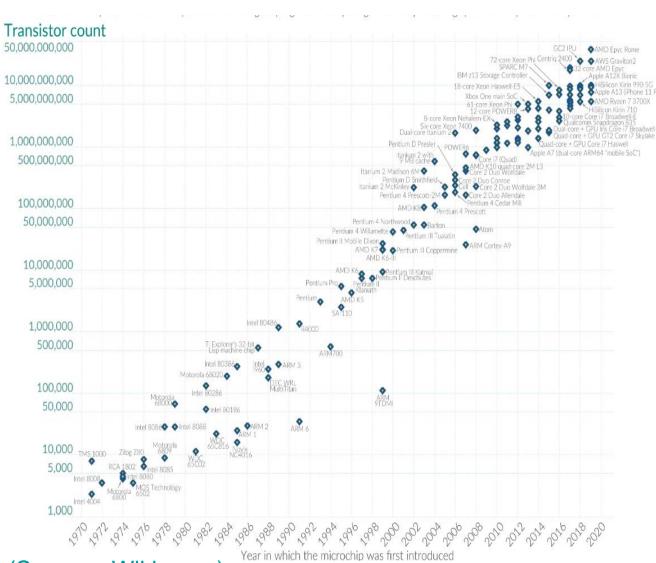

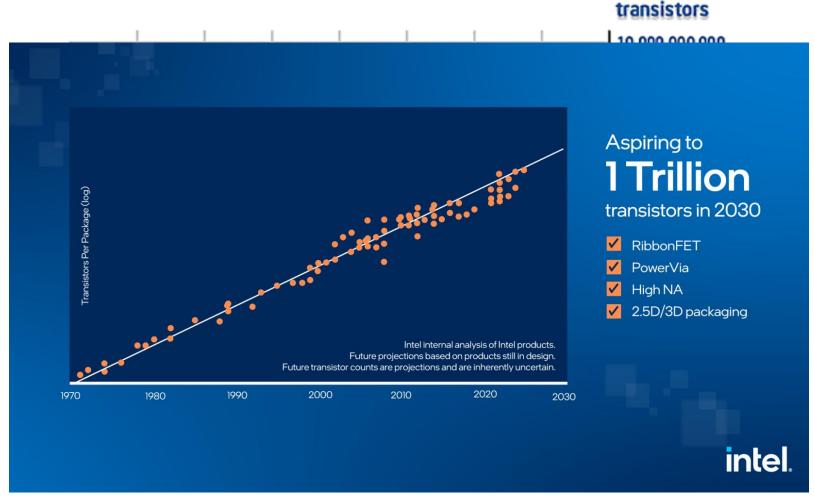

## **Evolution in Transistor Count**

•Process:10 µm -1971 •6 um – 1974 •3 µm – 1977 • 1.5 µm – 1981 •1 µm – 1984 •800 nm - 1987 •600 nm – 1990 •350 nm - 1993 •250 nm - 1996 •180 nm - 1999 •130 nm - 2001 •90 nm - 2003 •65 nm – 2005 •45 nm – 2007 •32 nm - 2009 •22 nm – 2012 •14 nm – 2014 •10 nm - 2016 •7 nm - 2018 •5 nm - 2020 •3 nm - 2022 •Future2 nm ~ 2024

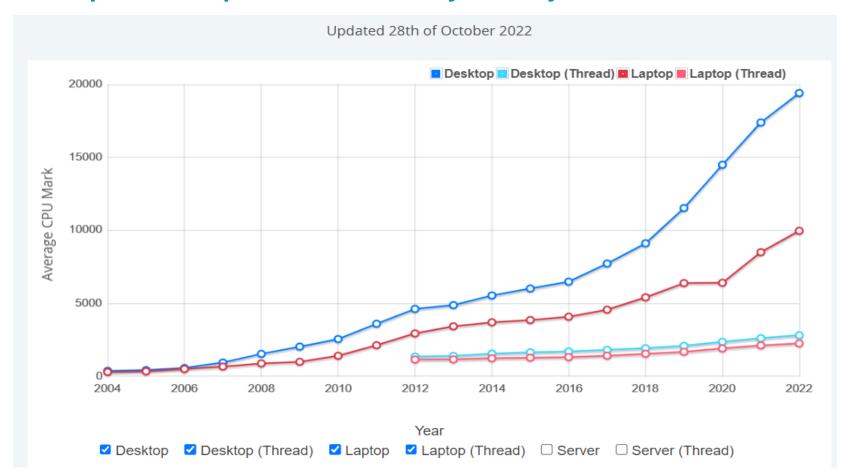

## Evolution in Speed/Performance

Year on Year Performance Of Intel CPU Benchmark: <a href="https://www.cpubenchmark.net/year-on-year.html">https://www.cpubenchmark.net/year-on-year.html</a>

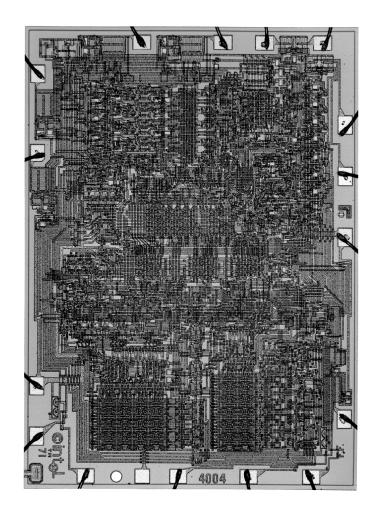

## Intel 4004 Micro-Processor

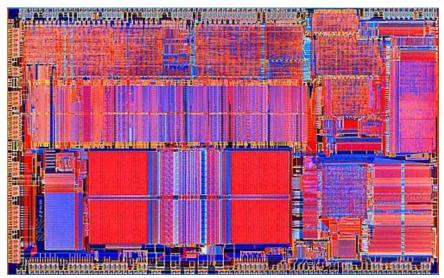

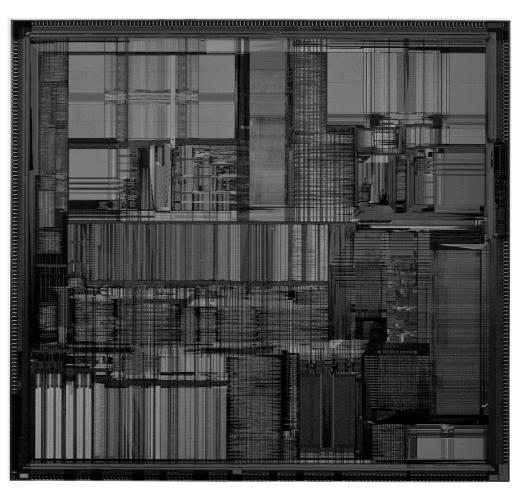

## Intel Pentium (II) microprocessor

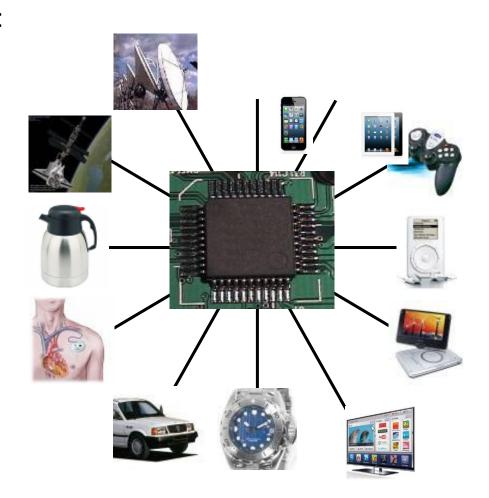

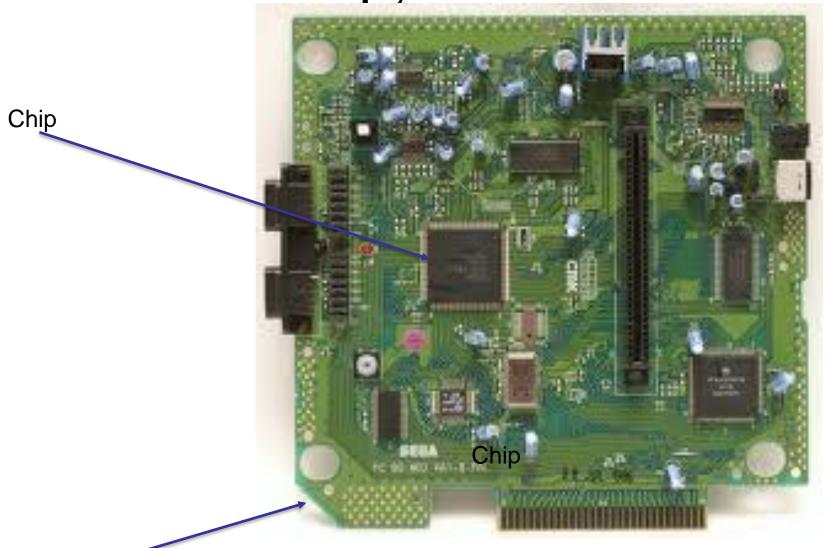

# Digital Chips & Integrated Circuits)

- Chips are used everywhere:

- Computers

- Cellular phones

- iPADs

- iPhones

- Gaming systems

- DVD players, TVs

- Watches

- Cars

- Medical devices

- Pacemakers and coffee pots

- Space stations

- Greeting cards

- . . .

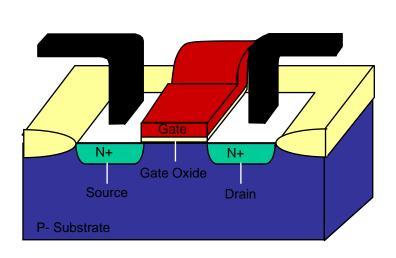

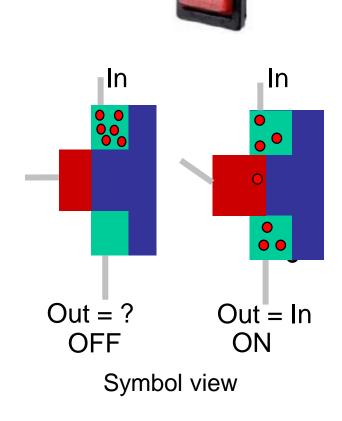

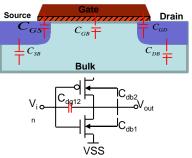

## **Basic Element**

CMOS Transistor is a switch

Cross section

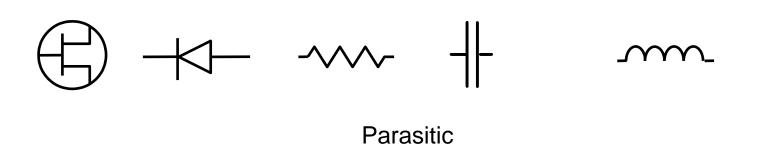

# Basic Elements of Electronic Circuits

| Transistor – is the switch                                       |             |

|------------------------------------------------------------------|-------------|

| Diode – is the rectifier                                         |             |

| Resistor - slows down electricity                                |             |

| Capacitor - stores electricity                                   | <del></del> |

| Inductor - determines the magnitude of the electromagnetic force |             |

| Connecting them with interconnects, an IC is obtained.           |             |

<sup>\*</sup>The elements, being prepared by discrete technology, are shown.

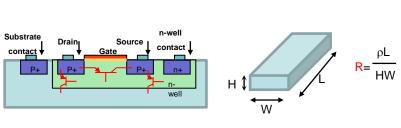

# Types of IC Elements

## Useful

Resistances

Inductances

## Elements in IC

STUDENTS-HUB.com

17

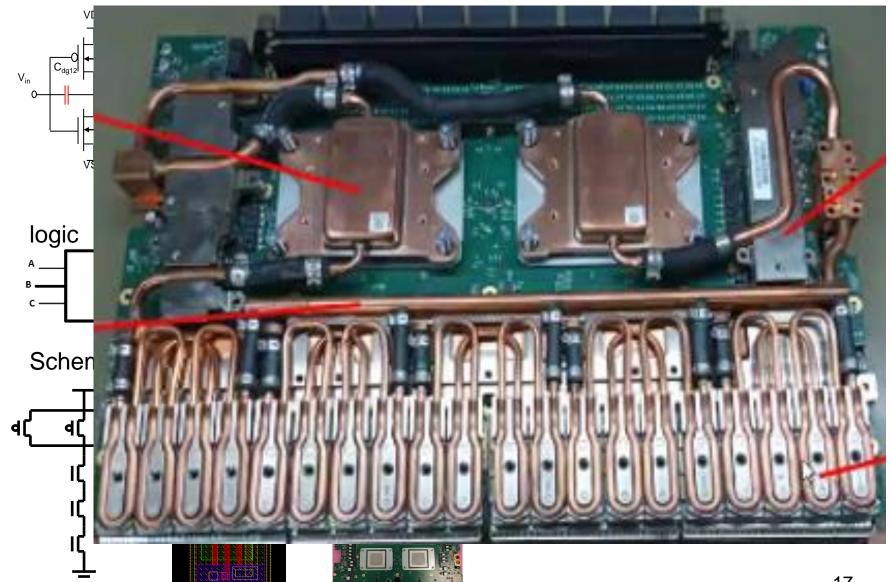

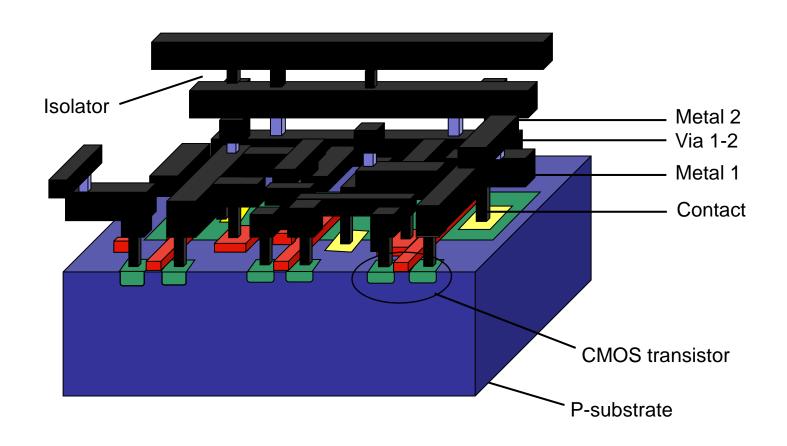

# IC as a Multi Layer Structure

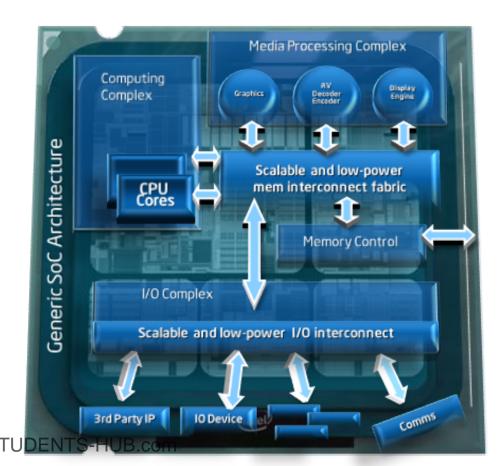

# IC Component Types

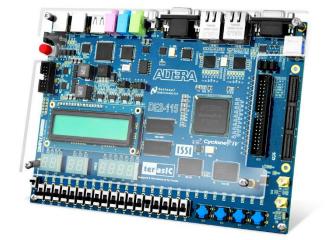

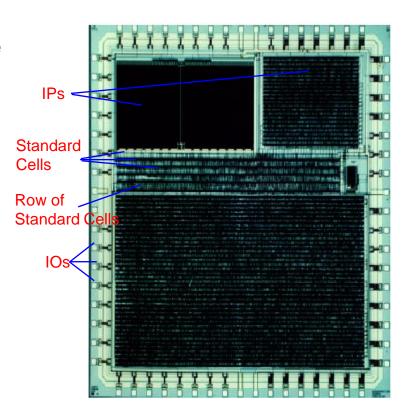

## Digital Standard Cells

Basic cells performing simplest functions (e.g. AND, OR, etc.) or more complex functions (Multiplexers, Latches, Flip-Flops, etc.) used as building blocks for large digital circuits

## Intellectual Property (IP) Blocks

Large blocks performing completed functions (DAC, ADC, PLL, etc), used in large designs

## Input/Output (I/O) Cells

Implement the connection between IC inner circuitry and external environment (PCB)

## Digital ICs

Large ICs (e.g. processor, GPU, etc.), distributed to end-users STUDENTS-HUB.com

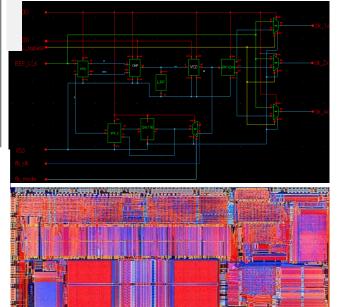

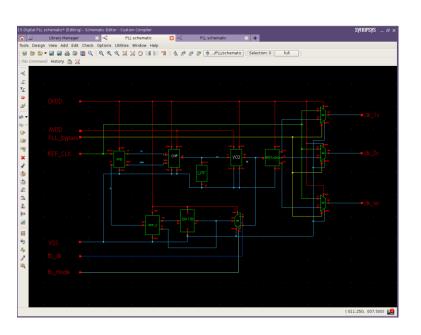

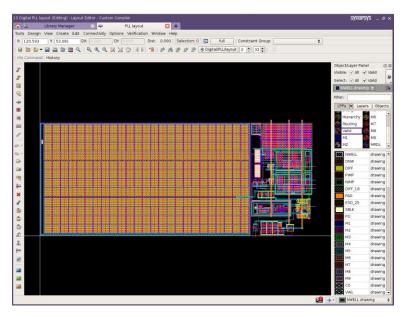

# IP Example

## **PLL**

Circuit Layout

# Technology Scaling: Moore's Law

https://www.intel.com/content/www/us/en/silicon-innovations/moores-law-technology.html

21

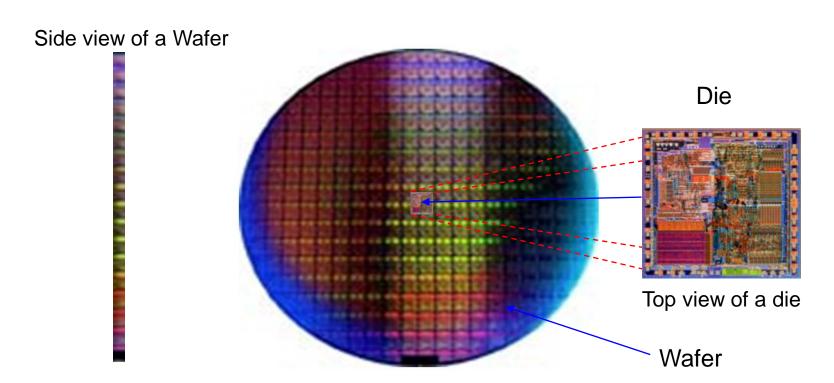

## Wafer and Die

- CMOS ICs are fabricated on circular slices of silicon called wafers.

- Wafer contains various identical dies.

https://www.youtube.com/watch?v=aWVywhzuHnQ

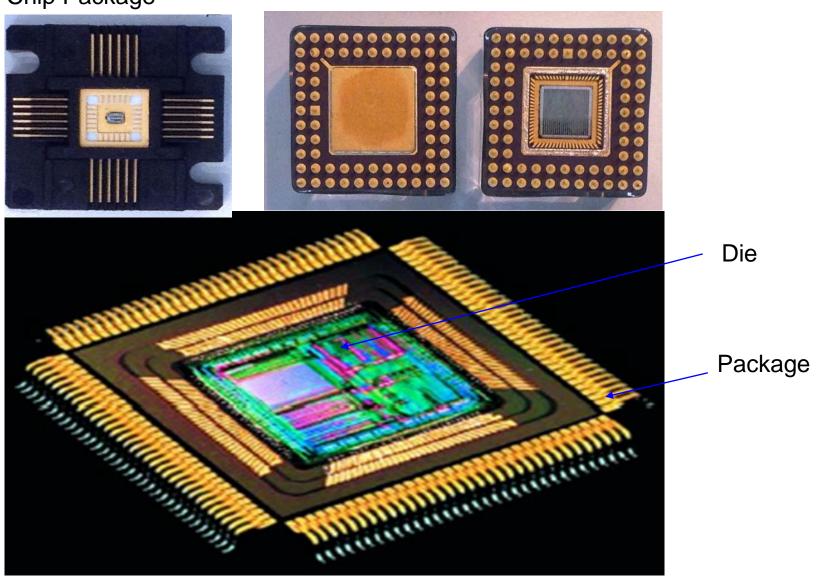

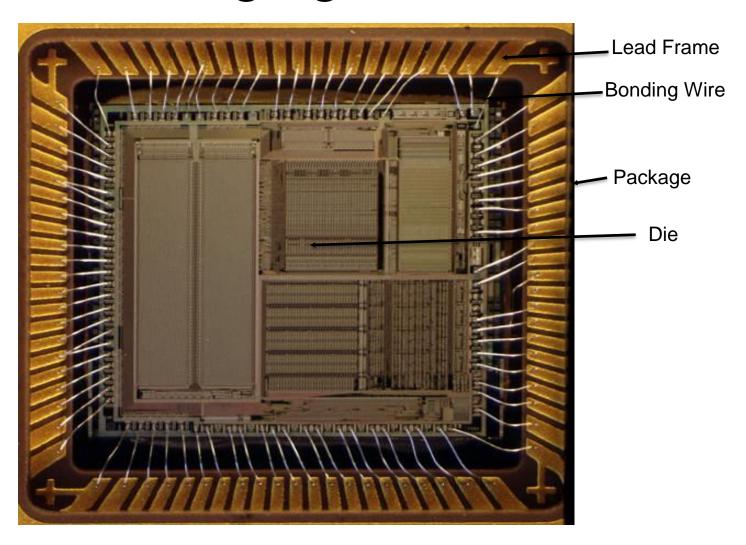

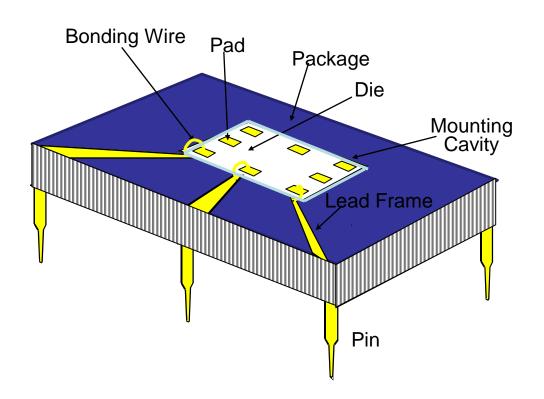

# Die and Package

Chip Package

# Packaging of Real IC

https://www.tipranks.com/news/intel-presents-new-transistor-technology-to-boost-chip-performance-by-20/?ref=blog

US chipmaker Intel Corp. last week revealed a new technology for making transistors which is said to improve the performance of its next round of processors by as much as 20%.

Intel (INTC) disclosed the so-called SuperFin technology for its existing 10-nanometer (nm) chip process node, describing it as its largest single, intra-node enhancement in the company's history, which promises to deliver performance improvement comparable to a full-node transition. The 10nm SuperFin technology combines Intel's with Super metal insulator metal capacitor, the company saidonymous

# Chip Packaging

- Bonding wires connect the package to the chip.

- Pads are arranged in a frame around the chip.

Chip, PCB

Printed circuit board (PCB)

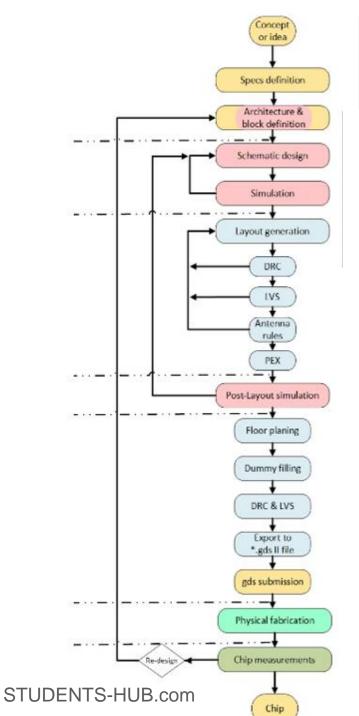

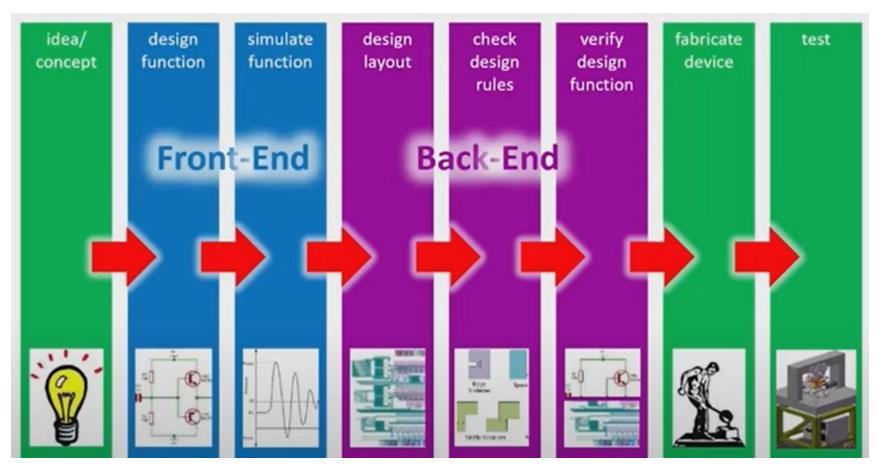

# Design Flow

Source : Photonic Integrated Circuit Design - PhotonHUB Europe Online Course 2022 https://www.youtube.com/watch?v=Zcle3hNmblg

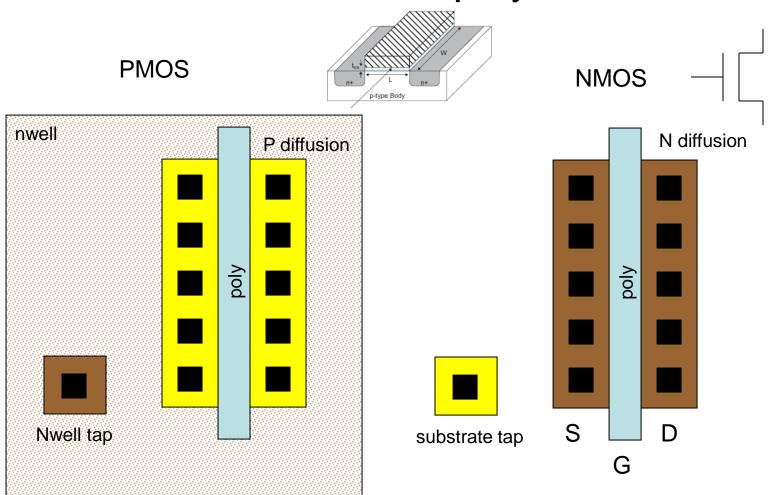

# Layout

Transistor defined as poly over diffusion

# Suggested Reading

- What is a Circuit

- Polarity

- Semiconductor

- Resistors

- Diodes

- Capacitors

- Transistors