# Basic Electronics An Introduction to Electronics for Science Students

Curtis A. Meyer Carnegie Mellon University

16 August, 2007

#### COPYRIGHT ©2006 Curtis A. Meyer

ALL RIGHTS RESERVED. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means—graphic, electronic, mechanical, including but not limited to photocopying, recording, taping, web distribution, information networks, or information storage and retrieval systems—without written permission of the author.

For permission to use material from this text, contact the author via

Email: cmeyer@curtismeyer.com

Web: http://www.curtismeyer.com

# Preface

This book has been written to support a one-semester laboratory course in electronics that is taught at Carnegie Mellon University (CMU). Physics majors typically take this course during the second semester of their sophomore year. The course as taught at CMU consists of two one-hour lectures and two three-hour labs per week. Students taking this course are expected to have completed three semesters of introductory physics courses. This includes an introduction to modern physics as well as a first course on mathematical methods in physics. While in principle this course should be accessible to students after completing one year of study, the additional math from the sophomore level courses helps with understanding of the math used in electronics—in particular complex numbers. However, I have tried to write the book as a self contained package with sufficient review of this math that it should be accessible. However, some of the optional topics may not be appropriate.

The material in this book has been developed from lecture notes that were used throughout the course. It also includes material that is not normally covered in the course, but is felt to show some of the diversity in the topic. The purpose of this book is not to train expert electronic designers, but rather to expose science students to basic electronics concepts in conjunction with hands-on laboratory experience that closely matches the material in the book. When possible, I have tried to present the material in context with other physics courses, as well as trying to analyze equations the way that scientists view them. Students completing such a course should be ready to use a more-sophisticated text in designing circuits for use in other laboratory environments.

In writing this book, I have drawn on handouts from and discussion with my colleagues at CMU. In particular, I would like to acknowledge course handouts written by Bob Suter. I would also like to thank Brian Quinn for his careful reading of the original sets of lecture notes and Roy Briere for many discussions on the presentation of material. I also deeply appreciate the careful reading the manuscript by Ted LaPage. His comments have made the book substantially clearer. However, even with all this help, there will certainly still remain errors in the text. For those, I must take personal responsibility. Finally, I would like to thank the several years of CMU sophomores who finally managed to make me believe that a more appropriate text needed to be developed for the course and my wife Annette and daughter Allison for convincing me to take the plunge and actually write this book.

iv

# Contents

| 1        | Dire | ect-Current Circuits                           | 1  |

|----------|------|------------------------------------------------|----|

|          | 1.1  | Introduction                                   | 1  |

|          | 1.2  | Electricity and Magnetism                      | 1  |

|          |      | 1.2.1 Coulomb's Law                            | 1  |

|          |      | 1.2.2 Voltage                                  | 2  |

|          |      | 1.2.3 Current                                  | 3  |

|          |      | 1.2.4 Conductivity, Resistivity and Resistance | 4  |

|          |      | 1.2.5 Power                                    | 6  |

|          |      | 1.2.6 Capacitance and Capacitors               | 6  |

|          |      |                                                | 8  |

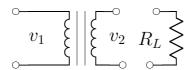

|          |      | 1.2.8 Transformers                             | 9  |

|          | 1.3  | Simple Circuits                                | 1  |

|          |      | 1.3.1 Time scales                              | 1  |

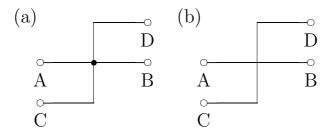

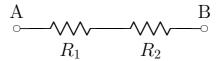

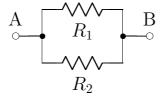

|          |      | 1.3.2 Resistors in Series and Parallel         | 2  |

|          |      |                                                | 3  |

|          |      |                                                | 5  |

|          | 1.4  |                                                | 7  |

|          | 1.5  |                                                | 7  |

|          |      | •                                              | 7  |

|          |      |                                                | 8  |

|          |      |                                                | 20 |

|          |      | •                                              | 21 |

|          | 1.6  |                                                | 25 |

|          |      |                                                | 27 |

|          |      |                                                | 28 |

|          |      |                                                |    |

| <b>2</b> | Alte | ernating-Current Circuits 3                    | 5  |

|          | 2.1  |                                                | 35 |

|          | 2.2  | ±                                              | 36 |

|          | 2.3  | Characterizing Time-dependent Voltages         | 39 |

|          |      | 2.3.1 Power Dissipation in AC Circuits         | 10 |

|          |      | 2.3.2 Time-dependent Circuits                  | 11 |

|          | 2.4  | The Gain of a Circuit                          | 12 |

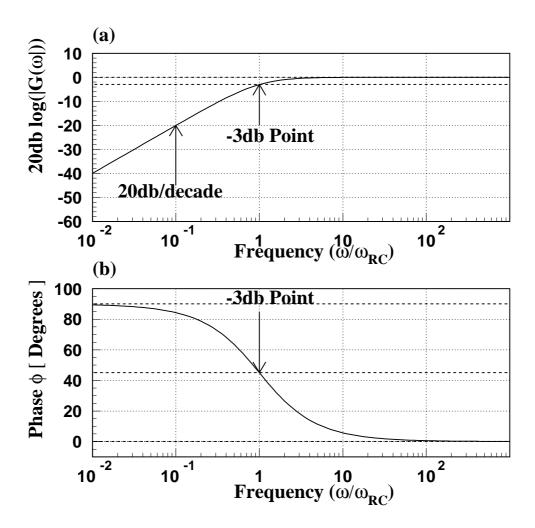

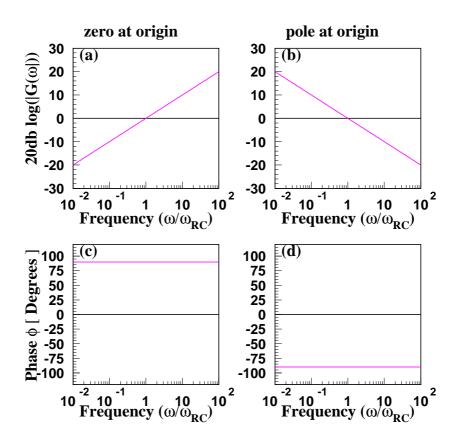

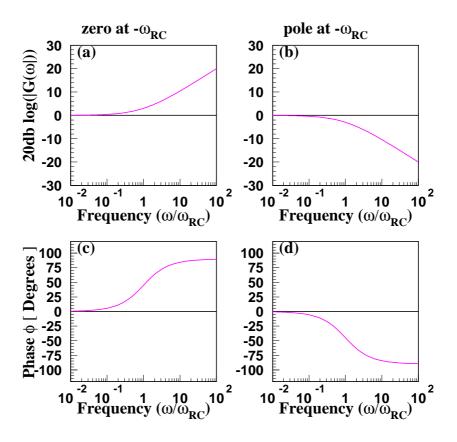

|          | 2.5  | Bode Plots                                     | 13 |

|          | 2.6  | The Impedance of Circuit Elements              | 15 |

|          |      | 2.6.1 Power Dissipation                        | 51 |

|          | 2.7  | Time Domain Analysis                           | 51 |

|          |      | 2.7.1 The <i>RC</i> Circuit                    | 51 |

|          |      | 2.7.2 The $RL$ Circuit                         | 53 |

|          |      | 2.7.3 Characteristic Times                     | 64 |

vi CONTENTS

|   |                                        | 2.7.4 The $LC$ Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                                |

|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|   | 2.8                                    | Fourier Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                                                                                                |

|   |                                        | 2.8.1 Filtering Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                                                                                                |

|   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| 3 | $\mathbf{Filt}$                        | ering Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                                                                                |

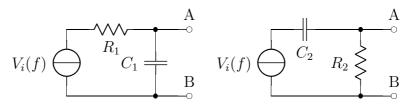

|   | 3.1                                    | Circuit Analysis in the Frequency Domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                                                                                                                                |

|   | 3.2                                    | The Low-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69                                                                                                                                |

|   |                                        | 3.2.1 The Gain of the Low-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69                                                                                                                                |

|   |                                        | 3.2.2 The Output Impedance of the Low-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                                                                |

|   |                                        | 3.2.3 The Input Impedance of the Low-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72                                                                                                                                |

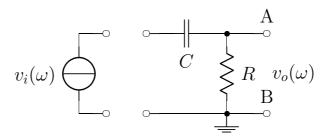

|   | 3.3                                    | The High-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                                                                |

|   | 0.0                                    | 3.3.1 The Gain of the High-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                                                                |

|   |                                        | 3.3.2 Input and Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73                                                                                                                                |

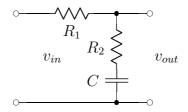

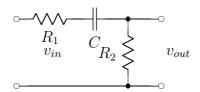

|   | 3.4                                    | Integrating and Differentiating Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7:                                                                                                                                |

|   | -                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

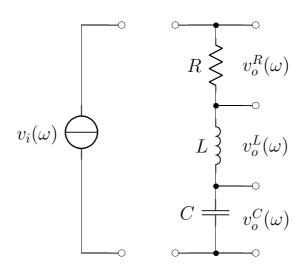

|   | 3.5                                    | RLC Circuit Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                                                                                                                |

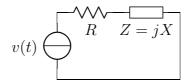

|   |                                        | 3.5.1 The series RLC circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77                                                                                                                                |

|   |                                        | 3.5.2 The LC-parallel RLC circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                                                                                                |

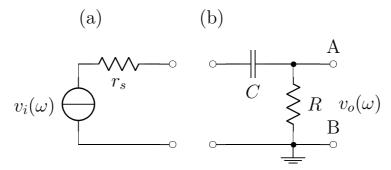

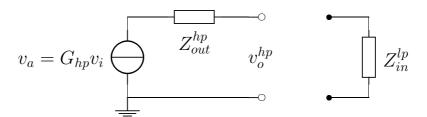

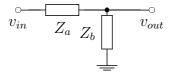

|   | 3.6                                    | Driving Loads with Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84                                                                                                                                |

|   | 3.7                                    | Chaining Filters Together                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86                                                                                                                                |

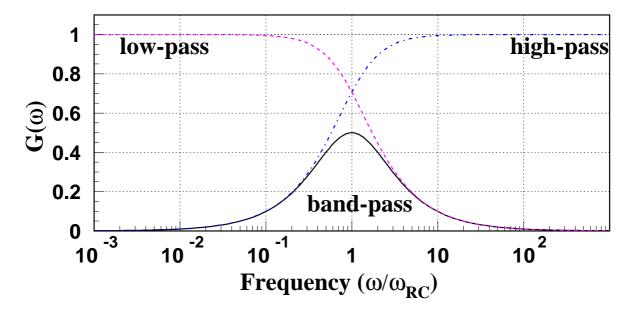

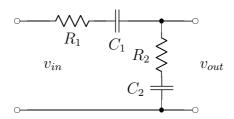

|   |                                        | 3.7.1 The Band-pass Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86                                                                                                                                |

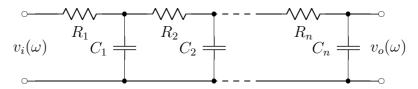

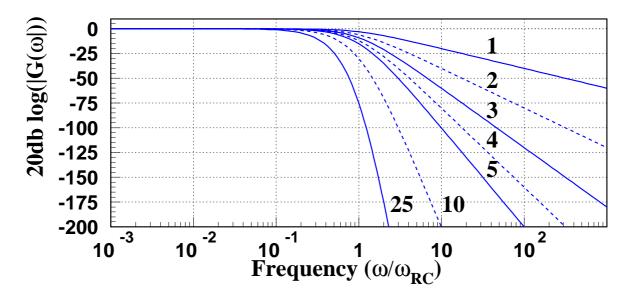

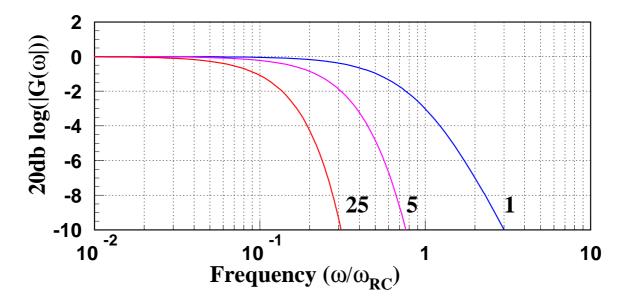

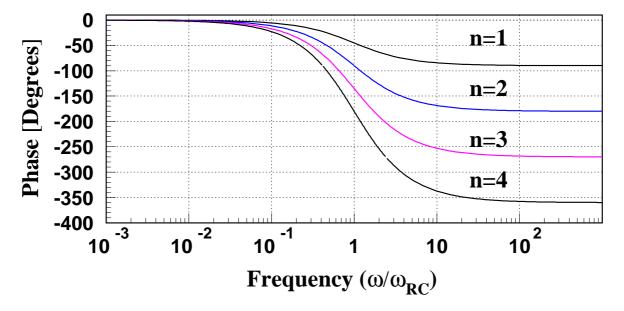

|   | 3.8                                    | Building Better Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91                                                                                                                                |

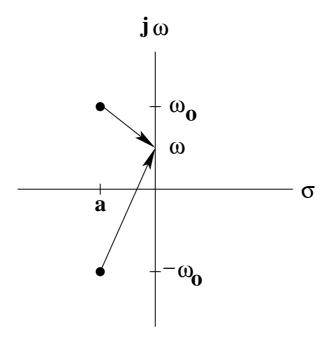

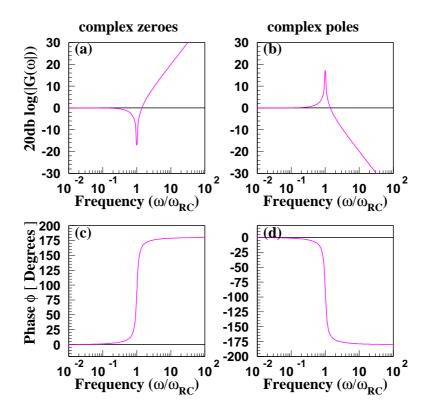

|   | 3.9                                    | Theoretical Considerations (Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                                                                                                                                |

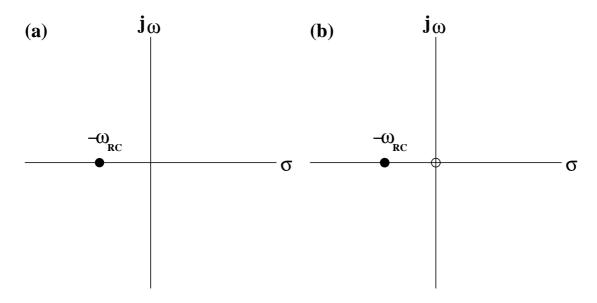

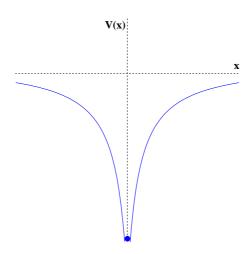

|   |                                        | 3.9.1 Complex Frequencies and Transfer Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93                                                                                                                                |

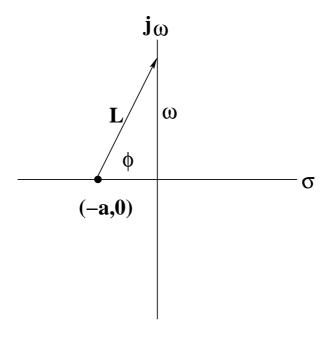

|   |                                        | 3.9.2 Graphical Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 94                                                                                                                                |

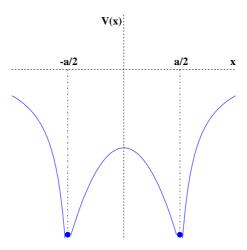

|   |                                        | 3.9.3 Pole-Zero Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98                                                                                                                                |

|   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|   |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| 4 | Intr                                   | roduction to Semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105                                                                                                                               |

| 4 | Intr<br>4.1                            | Poduction to Semiconductors Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105<br>105                                                                                                                        |

| 4 |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| 4 | 4.1                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                                                                               |

| 4 | 4.1<br>4.2                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105<br>105                                                                                                                        |

| 4 | 4.1<br>4.2<br>4.3                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105<br>105<br>108                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105<br>105<br>108<br>110                                                                                                          |

| 4 | 4.1<br>4.2<br>4.3                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105<br>105<br>108<br>110<br>112<br>114                                                                                            |

| 4 | 4.1<br>4.2<br>4.3<br>4.4               | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105<br>105<br>108<br>110<br>112<br>114<br>116                                                                                     |

| 4 | 4.1<br>4.2<br>4.3<br>4.4               | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105<br>108<br>108<br>110<br>112<br>114<br>116<br>118                                                                              |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .                                                                                                                                                                                                                                                                                                                                                                                                         | 105<br>108<br>108<br>110<br>112<br>114<br>116<br>118                                                                              |

| 4 | 4.1<br>4.2<br>4.3<br>4.4               | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .                                                                                                                                                                                                                                                                                                                                                                                | 105<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>118                                                                       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .                                                                                                                                                                                                                                                                                                                                              | 105<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120                                                                       |

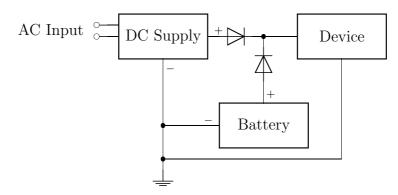

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup                                                                                                                                                                                                                                                                                                       | 105<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124                                                                |

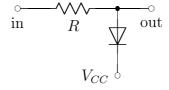

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup .  4.6.3 Diode Voltage Clamp                                                                                                                                                                                                                                                                          | 105<br>105<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124                                                         |

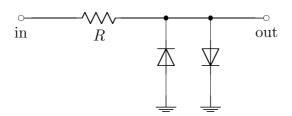

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup .  4.6.3 Diode Voltage Clamp .  4.6.4 Diode Voltage Limiter .                                                                                                                                                                                                                                         | 105<br>105<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>124                                           |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup .  4.6.3 Diode Voltage Clamp                                                                                                                                                                                                                                                                          | 105<br>105<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124                                                         |

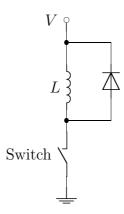

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Introduction . Energy Bands in Materials . Conduction in Materials . Semiconductor Materials . 4.4.1 Doped Semiconductors . 4.4.2 The pn Junction . Diodes . 4.5.1 Limitations on Diode Voltages . 4.5.2 Zener Diodes . Simple Diode Circuits . 4.6.1 Conversion from AC to DC . 4.6.2 Diode-controlled Battery Backup . 4.6.3 Diode Voltage Clamp . 4.6.4 Diode Voltage Limiter . 4.6.5 Inductive Kick Blocker .                                                                                                                                                                                                                       | 105<br>105<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>125                                           |

| 5 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials 4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes 4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker                                                                                                                                                                                                                                                     | 109<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>128<br>128                                    |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials  4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes  4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker  msistors Introduction                                                                                                                                                                                                                            | 109<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>125<br>127<br>127                             |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup .  4.6.3 Diode Voltage Clamp .  4.6.4 Diode Voltage Limiter .  4.6.5 Inductive Kick Blocker .  msistors  Introduction .  Bipolar Junction Transistors .                                                                                                                                               | 109<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124<br>124<br>125<br>127<br>127                                    |

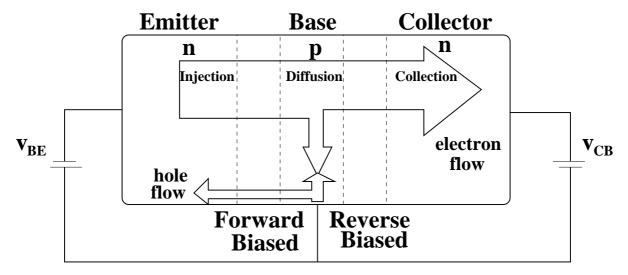

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials  4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes 4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker  msistors  Introduction Bipolar Junction Transistors 5.2.1 Overview of Operation                                                                                                                                                                   | 109<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>125<br>127<br>128<br>128                      |

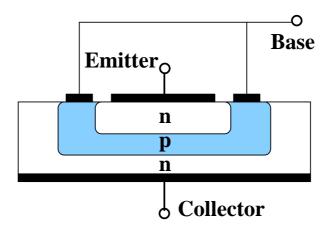

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials 4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes 4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker  Introduction Bipolar Junction Transistors 5.2.1 Overview of Operation 5.2.2 Bipolar Transistor Semiconductor Structure                                                                                                                             | 109<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>125<br>127<br>127<br>128<br>128<br>129        |

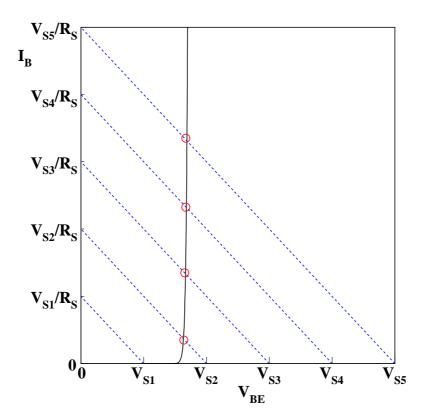

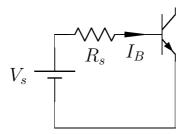

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials 4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes 4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker  sistors Introduction Bipolar Junction Transistors 5.2.1 Overview of Operation 5.2.2 Bipolar Transistor Semiconductor Structure 5.2.3 Transistor Operation                                                                                          | 109<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124<br>124<br>125<br>128<br>128<br>128<br>133                      |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction .  Energy Bands in Materials .  Conduction in Materials .  Semiconductor Materials .  4.4.1 Doped Semiconductors .  4.4.2 The pn Junction .  Diodes .  4.5.1 Limitations on Diode Voltages .  4.5.2 Zener Diodes .  Simple Diode Circuits .  4.6.1 Conversion from AC to DC .  4.6.2 Diode-controlled Battery Backup .  4.6.3 Diode Voltage Clamp .  4.6.4 Diode Voltage Limiter .  4.6.5 Inductive Kick Blocker .  msistors  Introduction .  Bipolar Junction Transistors .  5.2.1 Overview of Operation .  5.2.2 Bipolar Transistor Semiconductor Structure .  5.2.3 Transistor Operation .  5.2.4 The Eber-Moll Model . | 109<br>108<br>108<br>110<br>112<br>114<br>116<br>118<br>119<br>120<br>124<br>124<br>125<br>127<br>128<br>128<br>128<br>131<br>133 |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction Energy Bands in Materials Conduction in Materials Semiconductor Materials 4.4.1 Doped Semiconductors 4.4.2 The pn Junction Diodes 4.5.1 Limitations on Diode Voltages 4.5.2 Zener Diodes Simple Diode Circuits 4.6.1 Conversion from AC to DC 4.6.2 Diode-controlled Battery Backup 4.6.3 Diode Voltage Clamp 4.6.4 Diode Voltage Limiter 4.6.5 Inductive Kick Blocker  sistors Introduction Bipolar Junction Transistors 5.2.1 Overview of Operation 5.2.2 Bipolar Transistor Semiconductor Structure 5.2.3 Transistor Operation                                                                                          | 109<br>108<br>110<br>112<br>114<br>116<br>118<br>118<br>120<br>124<br>124<br>125<br>128<br>128<br>128<br>133                      |

|   | JN 1 I | ENIS                                                     | V11               |

|---|--------|----------------------------------------------------------|-------------------|

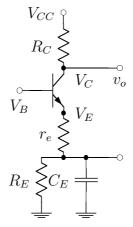

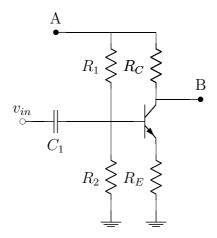

|   |        | 5.3.1 The Emitter-follower Circuit                       | 137               |

|   |        |                                                          | 143               |

|   |        |                                                          | 148               |

|   | 5.4    |                                                          | 153               |

|   | 5.4    |                                                          | 153               |

|   |        |                                                          | -                 |

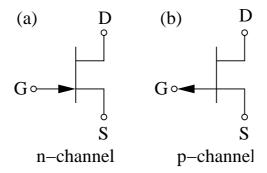

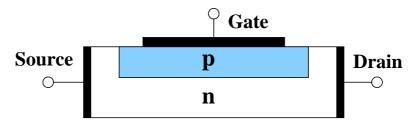

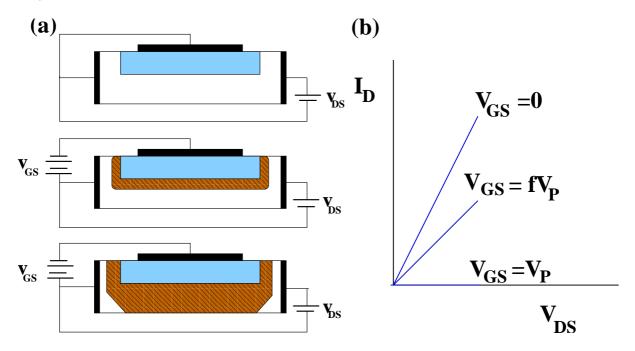

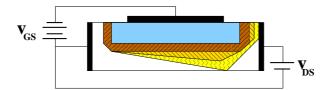

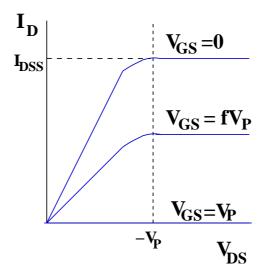

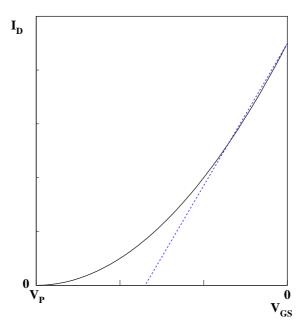

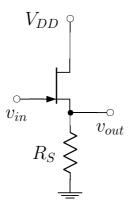

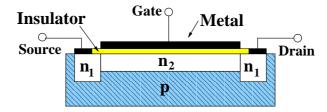

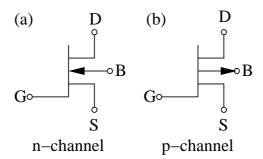

|   |        | 5.4.2 Metal-Oxide-Semiconductor Field Effect Transistors | 157               |

| 6 | Fee    | dback and Operational Amplifiers                         | 167               |

|   | 6.1    | Introduction                                             | 167               |

|   | 6.2    | Negative Feedback                                        | 167               |

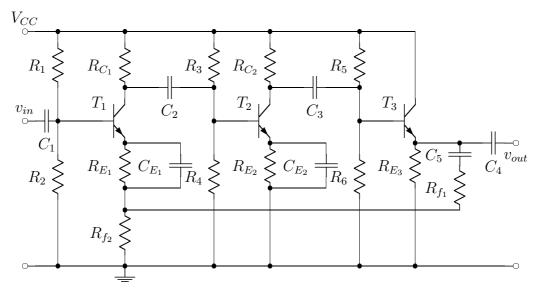

|   |        | 6.2.1 A High-Gain Amplifier                              | 170               |

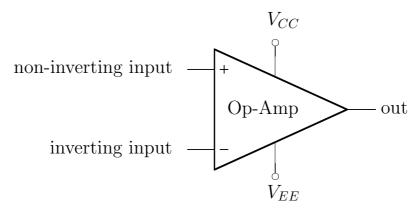

|   | 6.3    | Op-Amps                                                  | 170               |

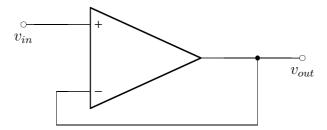

|   |        | 6.3.1 The Op-Amp Follower Circuit                        | 172               |

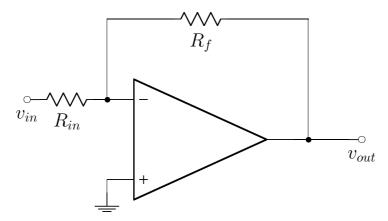

|   |        | 6.3.2 An Inverting Amplifier                             | 173               |

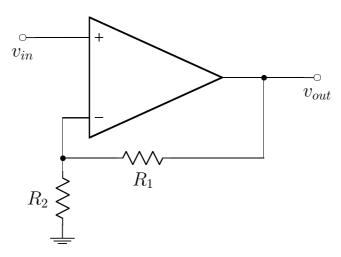

|   |        | 6.3.3 A Non-inverting Amplifier                          | 173               |

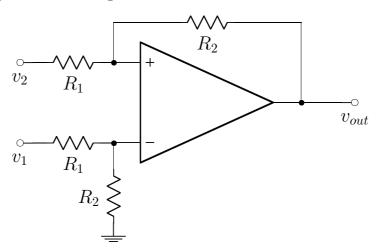

|   |        |                                                          | 175               |

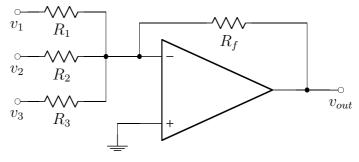

|   |        | •                                                        | 176               |

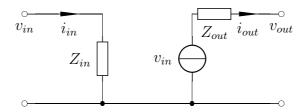

|   | 6.4    |                                                          | 176               |

|   |        |                                                          | 177               |

|   |        | · · · · · · · · · · · · · · · · · · ·                    | 177               |

|   |        |                                                          | 178               |

|   |        |                                                          | 178               |

|   |        |                                                          | 178               |

|   |        |                                                          | 178               |

|   |        |                                                          | 179               |

|   |        |                                                          | $179 \\ 179$      |

|   | c r    | 1 1 1                                                    |                   |

|   | 6.5    |                                                          | 181               |

|   |        |                                                          | 181               |

|   | c c    | O 1                                                      | 183               |

|   | 6.6    |                                                          | 184               |

|   | 6.7    | v                                                        | 185               |

|   |        |                                                          | 185               |

|   |        | v                                                        | 187               |

|   | 6.8    | •                                                        | 188               |

|   |        |                                                          | 188               |

|   |        | 6.8.2 The Schmitt Trigger                                | 188               |

| 7 | Dig    | ital Electronics                                         | 199               |

|   | 7.1    |                                                          | 199               |

|   | 7.2    | ~                                                        | 199               |

|   | 7.3    |                                                          | 201               |

|   | 7.4    |                                                          | 201               |

|   | 1.1    |                                                          | $\frac{201}{202}$ |

|   |        | ě                                                        | $\frac{202}{203}$ |

|   |        |                                                          | $\frac{205}{206}$ |

|   | 7.5    |                                                          | $\frac{200}{208}$ |

|   | 1.0    |                                                          |                   |

|   |        | 1 1                                                      | 208               |

|   |        | 1 1                                                      | 210               |

|   | 7.0    | 1 1                                                      | 211               |

|   | 7.6    |                                                          | 213               |

|   |        | · · · · · · · · · · · · · · · · · · ·                    | 213               |

|   |        | 7.6.9 A Clask Duka Consector                             | ·) 1 4            |

| vii | i                                      | CC                                                                                    | ONTEN | TS                                     |

|-----|----------------------------------------|---------------------------------------------------------------------------------------|-------|----------------------------------------|

|     |                                        | 7.6.3 A Gate Generator                                                                |       | 216                                    |

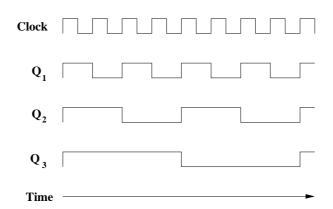

|     | 7.7                                    | Counter Circuits                                                                      |       | 216                                    |

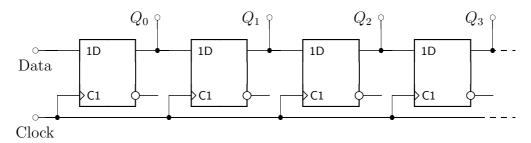

|     | 7.8                                    | Shift Registers                                                                       |       | 217                                    |

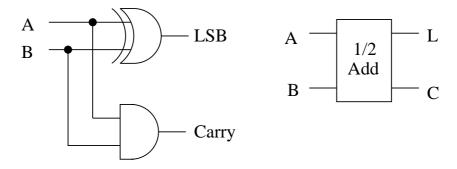

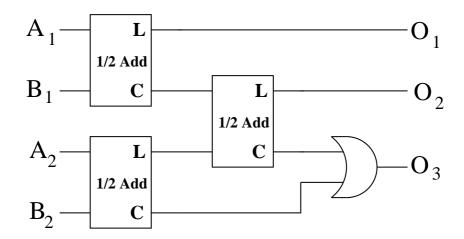

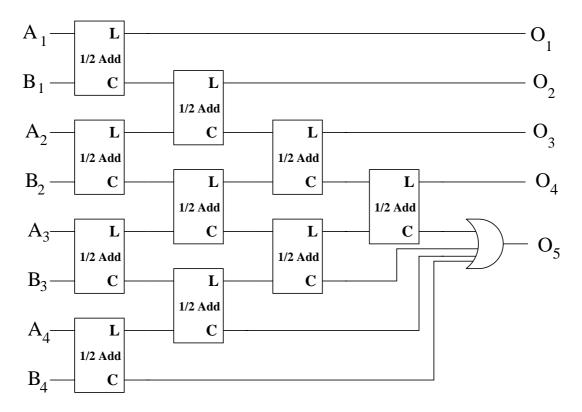

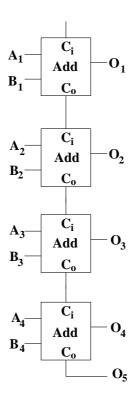

|     | 7.9                                    | Adder Circuits                                                                        |       | 219                                    |

|     |                                        | 7.9.1 The Half Adder Circuit                                                          |       | 219                                    |

|     |                                        | 7.9.2 Full Adder Circuits                                                             |       | 222                                    |

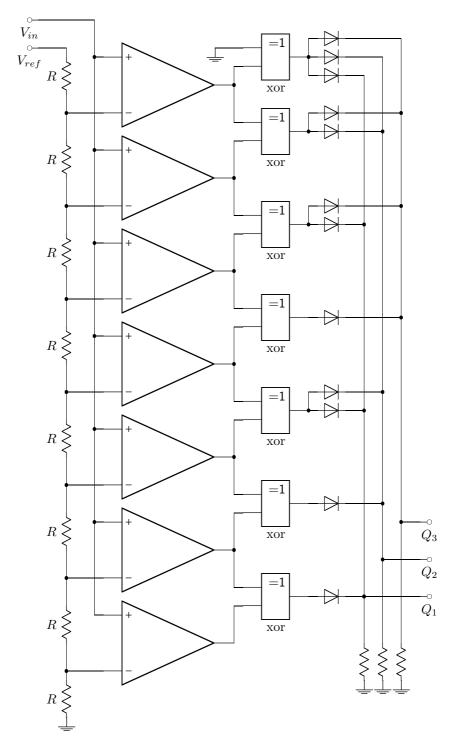

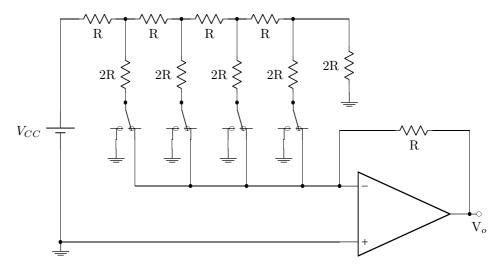

|     | 7.10                                   | Converters                                                                            |       |                                        |

|     |                                        | 7.10.1 Analog to Digital Converters                                                   |       | 224                                    |

|     |                                        | 7.10.2 Digital to Analog Converters                                                   |       |                                        |

|     |                                        |                                                                                       |       |                                        |

| A   | Con                                    | mponent Labels                                                                        | 2     | 227                                    |

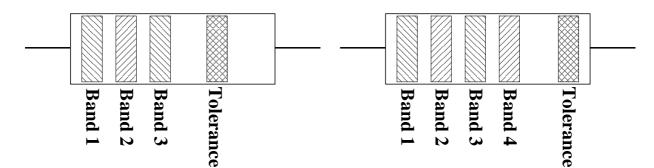

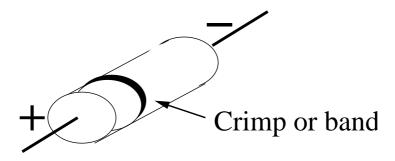

| A   |                                        | mponent Labels Resistor Codes                                                         | _     | •                                      |

| A   | A.1                                    |                                                                                       |       | 227                                    |

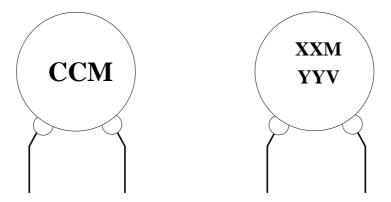

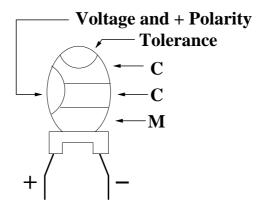

| A   | A.1<br>A.2                             | Resistor Codes                                                                        |       | 227 $230$                              |

| А   | A.1<br>A.2<br>A.3                      | Resistor Codes                                                                        |       | 227<br>230<br>232                      |

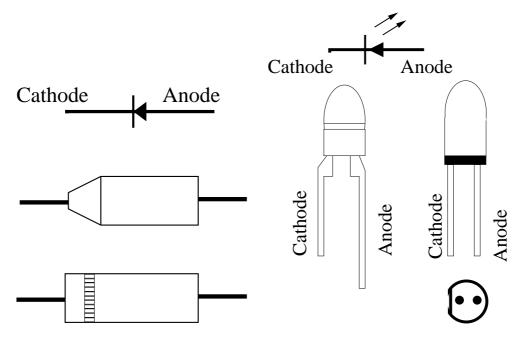

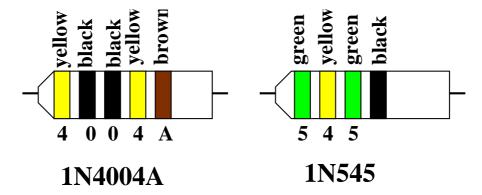

| A   | A.1<br>A.2<br>A.3<br>A.4               | Resistor Codes                                                                        |       | 227<br>230<br>232<br>233               |

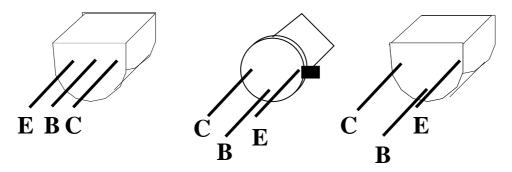

| A   | A.1<br>A.2<br>A.3<br>A.4<br>A.5        | Resistor Codes Capacitors Semiconductor Labels Diodes                                 |       | 227<br>230<br>232<br>233<br>235        |

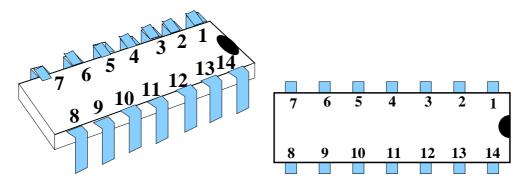

| В   | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | Resistor Codes Capacitors                                                             |       | 227<br>230<br>232<br>233<br>235<br>236 |

|     | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | Resistor Codes Capacitors Semiconductor Labels Diodes Transistors Integrated Circuits |       | 227<br>230<br>232<br>233<br>235<br>236 |

# Chapter 1

# **Direct-Current Circuits**

## 1.1 Introduction

This chapter is divided into two parts. The first is a review of basic electricity and magnetism concepts. We then review the definitions of voltage and current and move on to resistance, capacitance and then inductance. The second half of this chapter then looks in detail at direct-current circuits and the concept of equivalent circuits based on the current-versus-voltage curves of various devices. These latter concepts will be important throughout the remainder of the text.

## 1.2 Electricity and Magnetism

#### 1.2.1 Coulomb's Law

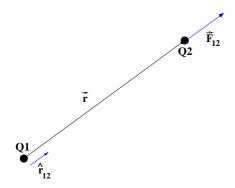

Figure 1.1: Two charges,  $Q_1$  and  $Q_2$  are separated by some radius,  $\vec{r}_{12}$ . The force exerted on charge 2 by charge 1 is given by Coulomb's law.

Any study of electricity and magnetism begins with Coulomb's law. This states that two electric charges separated by a distance r exert forces on each other given in equation 1.1, (see Figure 1.1).

$$\vec{F}_{1on2} = -\vec{F}_{2on1} = \frac{1}{4\pi\epsilon_o} \frac{Q_1 Q_2}{r^2} \hat{r}_{12} \,.$$

(1.1)

The quantity  $\hat{r}_{12}$  is a unit vector in the direction of  $\vec{r}_{12}$ . As one can see, the force falls off like one over the distance squared, and is proportional to the two electric charges. In the MKS system, charge is measured in *Coulombs*, C. The basic unit of charge is the magnitude of the charge on the electron,  $e=1.6\times 10^{-19}\,C$ . The quantity  $\epsilon_o$  is known as the *vacuum permittivity* and has a value of  $\epsilon_o=8.8541878176\times 10^{-12}\,C^2/Nm^2$ . From this, we find that the constant of proportionality in Coulomb's law is  $\frac{1}{4\pi\epsilon_o}=9\times 10^9\,Nm^2/C^2$ .

Coulomb's law can be generalized to the electric field of a point charge,  $\vec{E}$ , where for a point charge Q, the electric field is given as

$$\vec{E} = \frac{1}{4\pi\epsilon_0} \frac{Q}{r^2} \hat{r}.$$

This allows us to rewrite Coulomb's law for some electric charge,  $Q_2$  placed in some electric field  $\vec{E}$  as:

$$\vec{F} = Q_2 \vec{E}$$

If we consider a magnetic field,  $\vec{B}$ , and moving charges in addition to our electric fields, then we can generalize the force law to

$$\vec{F} = Q_2 \left( \vec{E} + \vec{v} \times \vec{B} \right) .$$

In MKS units,  $\vec{B}$  is measured in Tesla, T, such that  $T = (N \cdot s)/(C \cdot m)$  or  $N/(A \cdot m)$ , in which the unit of current, Ampere, A = C/s has been introduced.

#### 1.2.2 Voltage

The potential energy of a charge in an electric field is measured relative to the potential energy at some reference point:

$$U(\vec{r}) - U(\vec{r}_o) = -Q \int_{\vec{r}_o}^{\vec{r}} \vec{E}(\vec{r}) \cdot d\vec{r}.$$

This is just the work required to move the charge Q from  $\vec{r}_0$  to  $\vec{r}$  through the electric field  $\vec{E}$ . Recall that the differential amount of work is  $dW = \vec{F} \cdot d\vec{r}$  and that the potential energy is just the integral of this quantity. The potential energy,  $U(\vec{r})$ , is well-defined because the integral is independent of the path taken from  $\vec{r}_0$  to  $\vec{r}$ . Potential energy has the units of energy or Joules, J.

The electric potential, or just potential, at point  $\vec{r}$  is defined as the potential energy per unit of charge. The potential difference between the points  $\vec{r}$  and  $\vec{r}_o$  is given in equation 1.2. We refer to the potential difference between two points as the voltage between those points.

$$V(\vec{r}) - V(\vec{r}_o) = [U(\vec{r}) - U(\vec{r}_o)]/Q = \int_{\vec{r}_o}^{\vec{r}} \vec{E}(\vec{r}) \cdot d\vec{r}.$$

(1.2)

The units of potential difference, or voltage, are Volts, V = J/C. For positive Q, a point of higher potential energy is said to be at a higher potential. In fact, the charge carriers we usually deal with are electrons; we will finesse this point by pretending the charges are positive, but flowing in the opposite direction. This is discussed below. To summarize: a point of high potential is a point of high potential energy for positive charges; a point of negative potential is a point of negative potential energy for positive charges. Positive charges tend to move toward low potential points whereas electrons tend to move toward points of high potential. All potentials are defined relative to a chosen reference position and its potential, but in any physical problem, it is only the difference in potential that matters, not its absolute value at some given point. This difference is better referred to as the voltage between the points.

In electronics, we apply a voltage to a circuit by connecting the circuit to a voltage source which may be a battery, an electronic constant-voltage source (DC or "direct current" source) or a source whose voltage varies with time (AC or "alternating current" source in the case of a sinusoidal time dependence). Such a source always has (at least) two terminals (or connection points) and the "output voltage" of the source is the potential difference or voltage between these terminals.

Physiological response to an applied voltage is due to the fact that our bodies contain charged particles which can move in response to an electric. We sense a shock because it interferes with normal body function. Our nerves operate by sending electrical signals to our spinal cord and brain through electrically conducting nerve fibers. A few volts on the skin generally does not produce a discernible result—that is, noticeable current does not reach nerve fibers. Response to larger voltage differences depends on the distance  $|\vec{r}-\vec{r_o}|$  over which the voltage is applied and the physiological position of application. A voltage difference of thousands of volts applied over a distance of about 5 mm on the tip of a finger might only result in a surprise and a small burned spot. The same voltage applied from a finger on the left hand to a finger on the right hand might have dramatically different results! Here, an electrical disturbance might well pass near the heart which is controlled by electrical impulses.

A standard convention is to measure voltages relative to that of the Earth (i.e.,  $\vec{r_0}$  is some point deep in the ground). What this usually means is that we measure voltage relative to the power-company ground or relative to a cold water pipe which is literally attached to the earth (when things are working right, these are the same). As a practical matter, the boxes containing most electronic devices are grounded so that you do not shock yourself when you touch them.

An exception to this convention occurs when you use a battery or a *floating* power supply: these devices maintain (more or less) a fixed potential difference between their terminals. The potential *floats* relative to ground unless you explicitly connect one side to a conductor which is grounded. This is sometimes required and sometimes just a good idea. On rare occasions it cannot be done.

Since  $V(\vec{r})$  is independent of the path from the reference point to  $\vec{r}$ , we can follow *any* path from one of the source's terminals to the other and we will see the same potential difference. An extension of this logic is known as (one of) **Kirchhoff's laws**:

$$\sum_{loop} V_i = 0, \tag{1.3}$$

where the  $V_i$  are voltage rises (or drops—you choose one or the other and use appropriate signs) across elements in a loop. Note that in going around a loop, we may have some voltage rises and some drops: once we go around an entire loop, we must return to the potential at which we started.

In electronics, we generally approximate wires as perfect conductors. Wires therefore have NO potential drop. The voltage at one end of a wire is the same as that at the other end. In circuit diagrams, we represent wires as lines. All points connected to the same line have to be at the same potential. In a circuit, the standard symbol for a DC voltage source is shown in Figure 1.2. The longer line is the terminal that is at the higher potential.

Figure 1.2: The standard electrical symbol for a DC voltage source. The terminal on the left is at a higher potential than that on the right.

#### 1.2.3 Current

An electrical current corresponds to a flow of electrical charges. The current, I, is the charge per second passing through a cross-sectional area of interest. If there is a local density of carriers,  $n \, [\text{m}^{-3}]$  or, more conventionally,  $[\text{cm}^{-3}]$ , of charges Q, moving with average velocity  $\vec{v}$ , then the amount of charge per second per area is

$$\vec{J} = nQ\vec{v}. \tag{1.4}$$

$\vec{J}$  is the current density with units of  $C/(s \cdot m^2)$  or  $A/m^2$ . If A is the area, perpendicular to the average velocity,  $\vec{v}$ , over which this charge is flowing (think of a wire), then the magnitude of the total current is

$$I = JA. (1.5)$$

Expanding this, we find that

$$I = nQvA. (1.6)$$

In electrical circuits, the conducting objects are generally electrons flowing through various materials. For electrons, Q = -e, where  $e = 1.602 \times 10^{-19} C$ . Since the charge is negative (this is a convention that dates back to Benjamin Franklin—blame him!), the current flows in the opposite direction to the velocity or flow of electrons. However, I is unchanged if we replace Q by -Q and  $\vec{v}$  by  $-\vec{v}$ . Therefore,

we can just as well think of positively charged particles going in the opposite direction to the electrons. In electronics, we only concern ourselves with the direction of current flow and ignore the question of the sign of carrier.

So, in what direction does the charge flow? First of all, the electrons are bound in materials, so it would take a large amount of energy to make them flow out of the material. Thus, by configuring materials (metal wires and semiconductors) into specific shapes, we determine where current flows. In a metal, charges are free to distribute themselves in response to a potential field. If one applies a significant potential difference (voltage) between the ends of a wire, a very large current can flow. That is, if  $\vec{E}$  is finite, a force will quickly generate a significant  $\vec{v}$  and, thus, a significant current. On the other hand, even in a metal, collisions limit the velocity and this gives rise to resistance. In a passive circuit element, positive charge always flows from high voltage to low (that is, electrons flow in the opposite direction). Only where chemical (batteries) or other outside electromagnetic forces (DC or AC supplies) are active can charges flow in the opposite direction.

#### 1.2.4 Conductivity, Resistivity and Resistance

In the previous section, we related the current in a material to the flow of charge carriers through the material (equation 1.4). In fact, it is an electric field,  $\vec{E}$ , in the material that causes the charge carriers to move. As such, it makes sense to define a proportionality constant between the vector current density,  $\vec{J}$ , and the electric field in a material,  $\vec{E}$ . This constant is known as the *conductivity* of the material and is given the symbol g. Equation 1.7 expresses this relationship.

$$\vec{J} = g\vec{E} \tag{1.7}$$

If we consider current flowing through a wire, equation 1.5 gives us the current I in terms of J and the area of the wire. Assuming that the electric field is uniform throughout the wire, the potential difference along the length, l, of the wire is just  $V = E \cdot l$ . If we put all of this together, we arrive at an expression that relates the current flowing through a wire to the potential difference between the ends of the wire.

$$I = \frac{gA}{l} \cdot V$$

From this, we can define the conductance, G, of the wire to be

$$G = \frac{gA}{l}$$

and the inverse, known as the resistance, R, of the wire to be

$$R = \frac{l}{gA}.$$

We can rewrite this as the familiar Ohm's Law,

$$V = I \cdot R \tag{1.8}$$

which can also be written in terms of conductance as

$$I = V \cdot G$$

.

From equation 1.8, the dimensions of resistance are volts per ampere, or ohms,  $\Omega$ . The standard symbol for a resistor is shown in Figure 1.3.

While the conductivity is a convenient number to report, one normally finds the inverse of the conductivity listed. This is defined as the resistivity of the material:

$$\rho = \frac{1}{g}.$$

Using the resistivity, the resistance of some material is given as  $R = \rho l/A$ . The dimensions of resistivity are  $\Omega m$ . Table 1.1 gives resistivity values for several materials. Good conductors such as metals have a very small resistivity, while good insulators have a very large resistivity.

The resistivity of a material also has a temperature dependence. Equation 1.9 shows the temperature dependence of  $\rho$ . Resistivity is typically reported at some reference temperature,  $T_0$ , which is usually taken to be room temperature.

$$\rho(T) = \rho(T_0) \left[ 1 + \alpha \left( T - T_0 \right) \right] \tag{1.9}$$

The temperature coefficient,  $\alpha$  can then be used to compute the resistivity at some other temperature. The exact definition of the temperature coefficient,  $\alpha$ , is

$$\alpha = \frac{1}{\rho} \frac{d\rho}{dT}. \tag{1.10}$$

From this latter definition, it is clear that equation 1.9 is only an approximation for temperature dependence of  $\rho$ . It is valid if the difference between the temperature and the reference temperature are *small enough*. It is valid for nearly everything that we might do in an electronics course with the exception of burning out a resistor!

Figure 1.3: The standard electrical symbol for a resistor.

Values for  $\alpha$  are listed in Table 1.1. For metals, these numbers are positive, which means that the resistivity, and hence the resistance of the material goes up as the temperature is increased. Note that for semi-conductors, we find that  $\alpha$  is negative. The resistivity goes down as the temperature is increased. We will see when we discuss

semiconductors that the conductivity is in fact increasing with increasing temperature.

| Material    | $\rho, \Omega \cdot m$ | $\alpha, K^{-1}$ |

|-------------|------------------------|------------------|

|             | Metals                 |                  |

| Copper      | $17.2 \times 10^{-9}$  | 0.00393          |

| Silver      | $15.9 \times 10^{-9}$  | 0.0038           |

| Gold        | $24.4 \times 10^{-9}$  | 0.0034           |

| Aluminum    | $28.2 \times 10^{-9}$  | 0.0039           |

| Brass       | $70 \times 10^{-9}$    | 0.0038           |

| Iron        | $100 \times 10^{-9}$   | 0.005            |

| Mercury     | $957.8 \times 10^{-9}$ | 0.00089          |

| Nickel      | $78 \times 10^{-9}$    | 0.006            |

| Tantalum    | $155 \times 10^{-9}$   | 0.0031           |

| Tin         | $115 \times 10^{-9}$   | 0.0042           |

| Zinc        | $58 \times 10^{-9}$    | 0.0037           |

| $S\epsilon$ | emic onductors         |                  |

| Carbon      | $35 \times 10^{-6}$    | -0.0005          |

| Germanium   | 0.46                   | -0.048           |

| Silicon     | $0.64 \times 10^{3}$   | -0.075           |

|             | Insulators             |                  |

| Glass       | $10^{10}$ to $10^{14}$ |                  |

| Quartz      | $7.5\times10^{17}$     |                  |

Table 1.1: The resistivity,  $\rho$  and the thermal coefficient  $\alpha$  for several different materials at  $20\,^{\circ}$ C. Data for metals are taken from the *Handbook of Chemistry and Physics*, 56'th edition, CRC Press, Inc., Cleveland, OH. Data for the semiconductors and insulators are taken from Wikipedia.

#### 1.2.5 Power

As with any physical system, we know that in electronics energy is conserved. However, rather than talking about energy, we usually discuss the time rate of change of energy, or the *power*, where power, P, is defined as

$$P = \frac{dE}{dt}.$$

Since energy is measured in Joules, the unit of power is a Joule per second, or a Watt.

$$1W = 1J/s$$

In electronics, we supply power to a circuit, some power is dissipated by the circuit (as heat), and some power can be delivered to the output of the circuit. For a current I flowing through a resistor R, the power dissipated in the resistor is just

$$P_R = I^2 R$$

.

Using Ohm's law, we can write the power dissipated in a resistor in two other equivalent forms:

$$P_R = VI$$

$$P_R = \frac{V^2}{R}.$$

In addition to the dissipated power, we also have power supplied to a circuit. If there is a voltage source, V, which drives a current I through the circuit, then the power supplied to the circuit is

$$P_s = VI$$

.

By conservation of energy, we can easily show that the power a circuit delivered to its output is equal to the power supplied minus the power dissipated.

**Example:** A 5-Volt DC power supply has a  $1000 \Omega$  resistor connected between its leads. How much power does the power supply provide and what is the power dissipated in the resistor? From Ohm's law, we know that the current through the resistor must be I = V/R, or  $5 \, mA$ . This means that the power delivered by the supply is just P = VI, or  $25 \, mW$ . The power dissipated in the resistor is  $P_R = I^2 R$ , or again  $25 \, mW$ .

#### 1.2.6 Capacitance and Capacitors

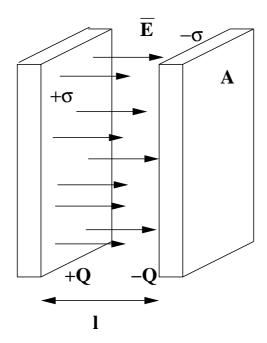

If a uniform electric field,  $\vec{E}$ , exists between two parallel conducting plates which are not electrically connected together, then we will induce surface charges on the surfaces of the two plates, +Q on the left-hand plate and -Q on the right-hand plate. This is shown schematically in Figure 1.4. The two plates are each of area A and are separated by a distance l. The induced charges will be spread over the surfaces with surface densities  $+\sigma$  and  $-\sigma$  respectively, where  $Q = \sigma \cdot A$ . Continuing, we also know that the electric field of an infinite plate with uniform surface charge density  $\sigma$  is given as

$$E = \frac{\sigma}{\epsilon_0}$$

.

The electric field creates a potential difference between the two plates of V = El, with the left-hand plate at a higher potential. So putting all of this together, we can arrive at a relationship between the charge on the capacitor plates, Q and the voltage between the two plates. This is given by:

$$Q = \frac{\epsilon_0 A}{l} \cdot V.$$

Figure 1.4: Two parallel conducting plates of area A separated by a distance l have an electric field  $\vec{E}$  that points from the left plate to the right plate. A positive charge, +Q is induced on the left-hand plate, while a negative charge, -Q is induced on the right-hand plate. The surface charge densities are  $+\sigma$  and  $-\sigma$  respectively.

We define the constant of proportionality as the capacitance, C, of the parallel plates.

$$C = \frac{\epsilon_0 A}{l} \tag{1.11}$$

╬

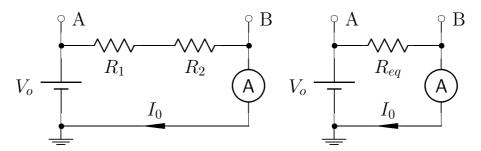

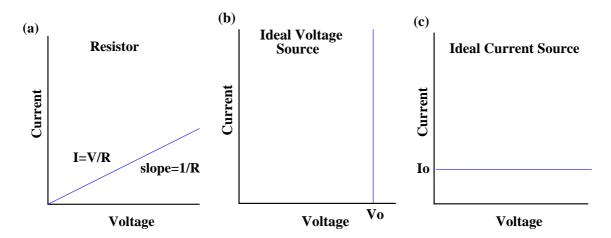

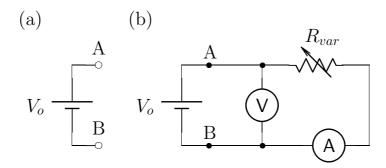

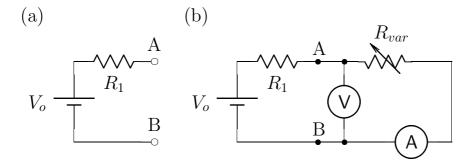

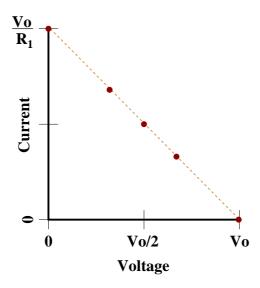

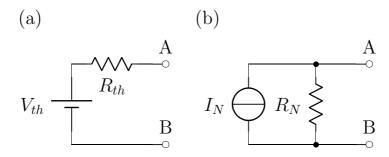

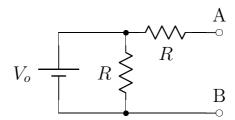

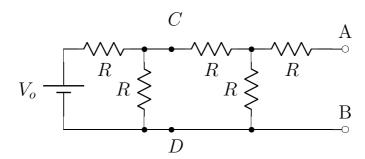

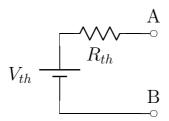

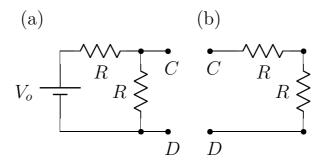

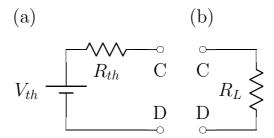

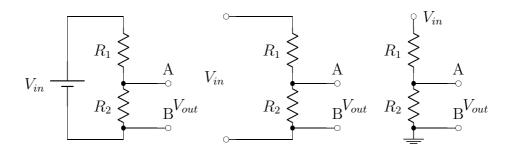

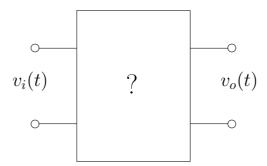

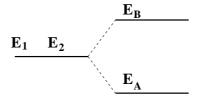

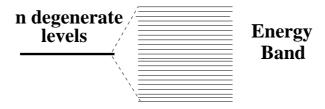

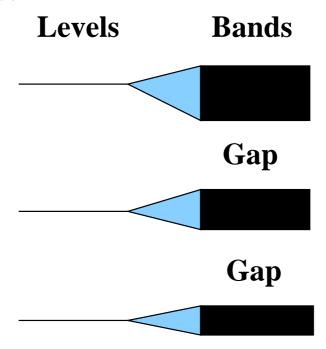

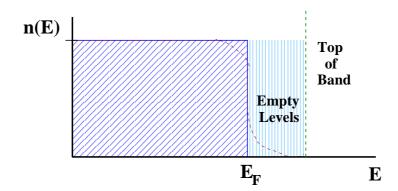

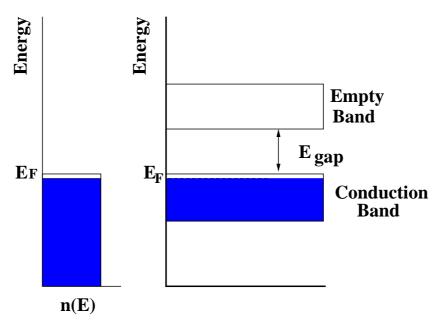

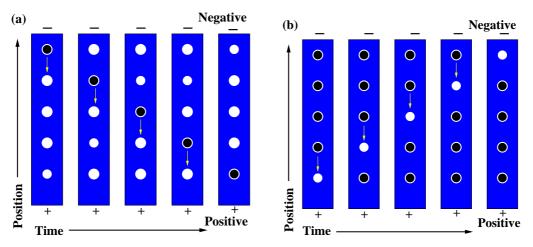

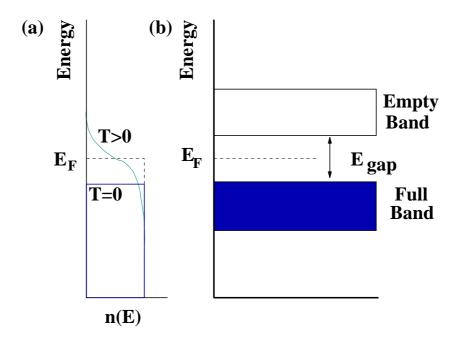

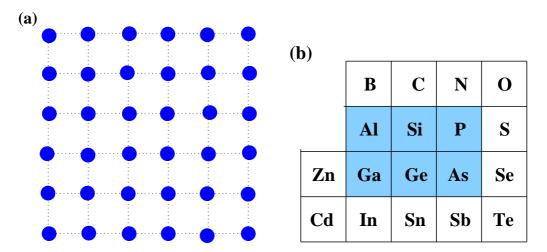

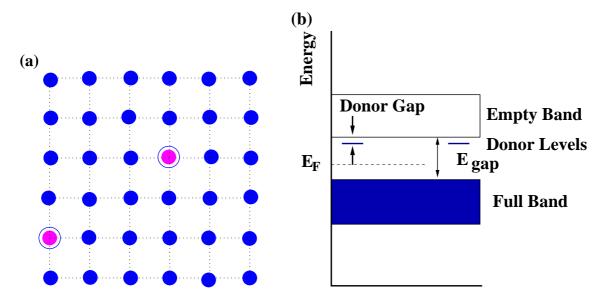

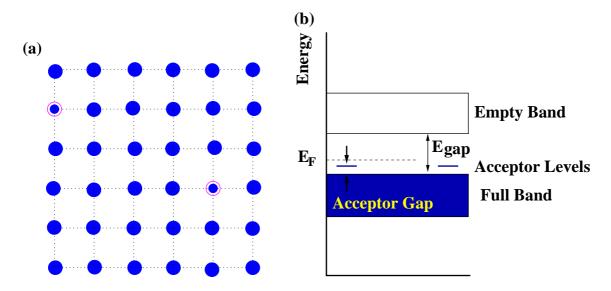

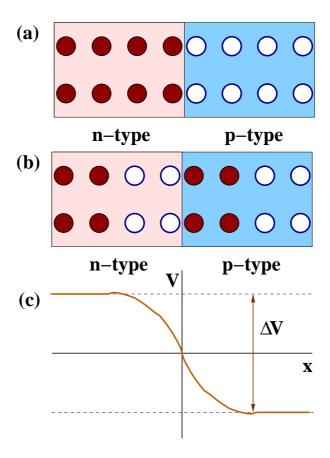

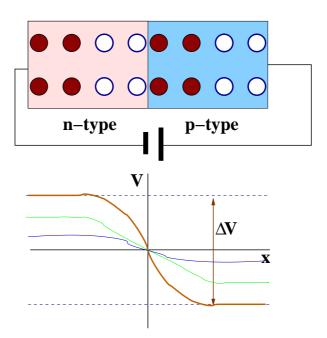

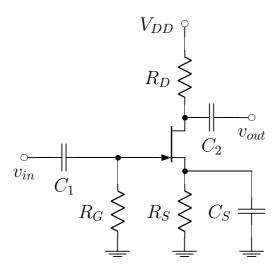

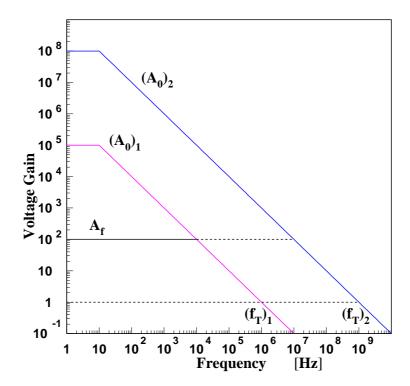

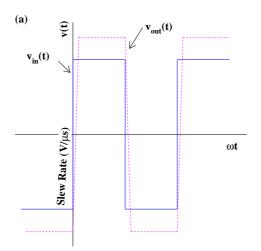

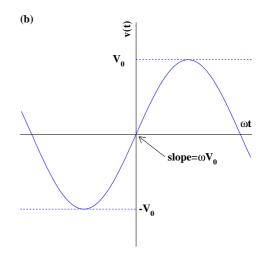

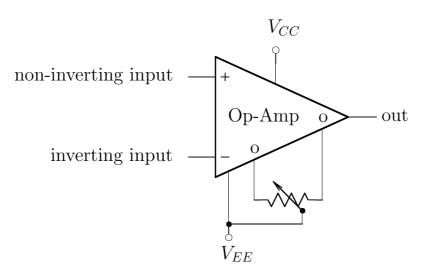

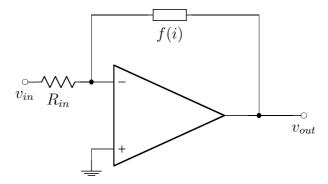

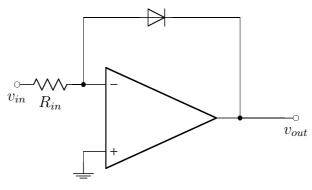

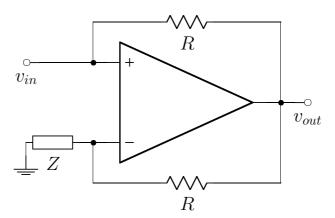

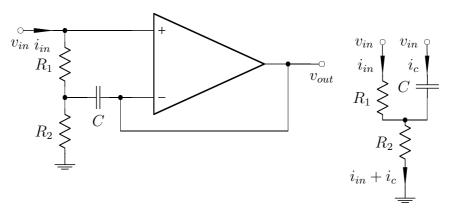

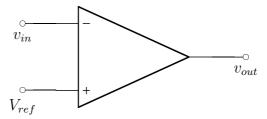

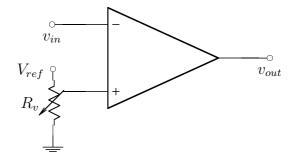

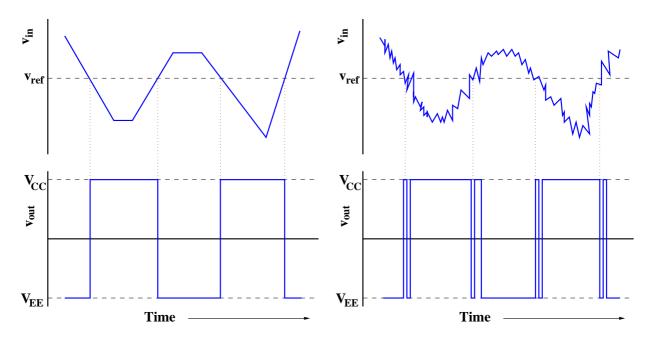

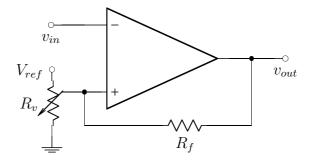

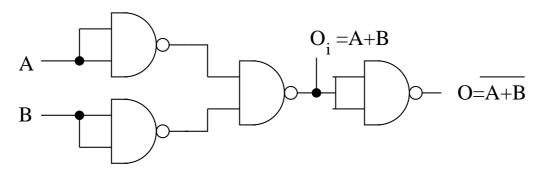

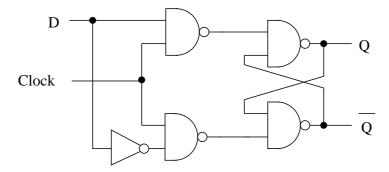

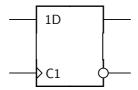

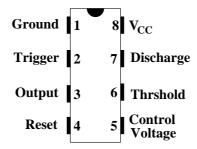

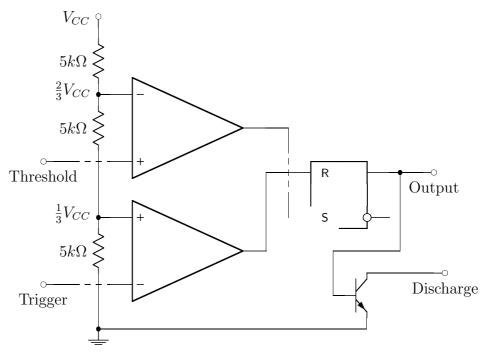

Figure 1.5: The standard electrical symbol for a capacitor. will just reduce the symbol for a capacitor is shown in Figure 1.5.